- 您现在的位置:买卖IC网 > PDF目录362741 > EP1S80F1508C7ES (Altera Corporation) Stratix Device Family Data Sheet PDF资料下载

参数资料

| 型号: | EP1S80F1508C7ES |

| 厂商: | Altera Corporation |

| 英文描述: | Stratix Device Family Data Sheet |

| 中文描述: | Stratix系列器件数据手册 |

| 文件页数: | 282/290页 |

| 文件大小: | 3559K |

| 代理商: | EP1S80F1508C7ES |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页第111页第112页第113页第114页第115页第116页第117页第118页第119页第120页第121页第122页第123页第124页第125页第126页第127页第128页第129页第130页第131页第132页第133页第134页第135页第136页第137页第138页第139页第140页第141页第142页第143页第144页第145页第146页第147页第148页第149页第150页第151页第152页第153页第154页第155页第156页第157页第158页第159页第160页第161页第162页第163页第164页第165页第166页第167页第168页第169页第170页第171页第172页第173页第174页第175页第176页第177页第178页第179页第180页第181页第182页第183页第184页第185页第186页第187页第188页第189页第190页第191页第192页第193页第194页第195页第196页第197页第198页第199页第200页第201页第202页第203页第204页第205页第206页第207页第208页第209页第210页第211页第212页第213页第214页第215页第216页第217页第218页第219页第220页第221页第222页第223页第224页第225页第226页第227页第228页第229页第230页第231页第232页第233页第234页第235页第236页第237页第238页第239页第240页第241页第242页第243页第244页第245页第246页第247页第248页第249页第250页第251页第252页第253页第254页第255页第256页第257页第258页第259页第260页第261页第262页第263页第264页第265页第266页第267页第268页第269页第270页第271页第272页第273页第274页第275页第276页第277页第278页第279页第280页第281页当前第282页第283页第284页第285页第286页第287页第288页第289页第290页

4–102

Stratix Device Handbook, Volume 1

Altera Corporation

July 2005

DLL Jitter

DLL Jitter

Table 4–134

reports the jitter for the DLL in the DQS phase shift reference

circuit.

f

For more information on DLL jitter, see the

DDR SRAM

section in the

Stratix Architecture

chapter of the

Stratix Device Handbook, Volume 1

.

t

ARESET

Minimum pulse width on

areset

signal

10

ns

Notes to

Tables 4–131

through

4–133

:

(1)

See

“Maximum Input & Output Clock Rates” on page 4–76

.

(2)

PLLs 7, 8, 9, and 10 in the EP1S80 device support up to 717-MHz input and output.

(3)

Use this equation (f

OUT

= f

IN

*

ml

(

n

× post-scale counter)) in conjunction with the specified f

INPFD

and f

VCO

ranges to determine the allowed PLL settings.

(4)

When using the SERDES, high-speed differential I/O mode supports a maximum output frequency of 210 MHz

to the global or regional clocks (that is, the maximum data rate 840 Mbps divided by the smallest SERDES J factor

of 4).

(5)

Refer to the section

“High-Speed I/O Specification” on page 4–87

for more information.

(6)

This parameter is for high-speed differential I/O mode only.

(7)

These counters have a maximum of 32 if programmed for 50/50 duty cycle. Otherwise, they have a maximum

of 16.

(8)

High-speed differential I/O mode supports

W

= 1 to 16 and

J

= 4, 7, 8, or 10.

Table 4–133. Fast PLL Specifications for -8 Speed Grades (Part 2 of 2)

Symbol

Parameter

Min

Max

Unit

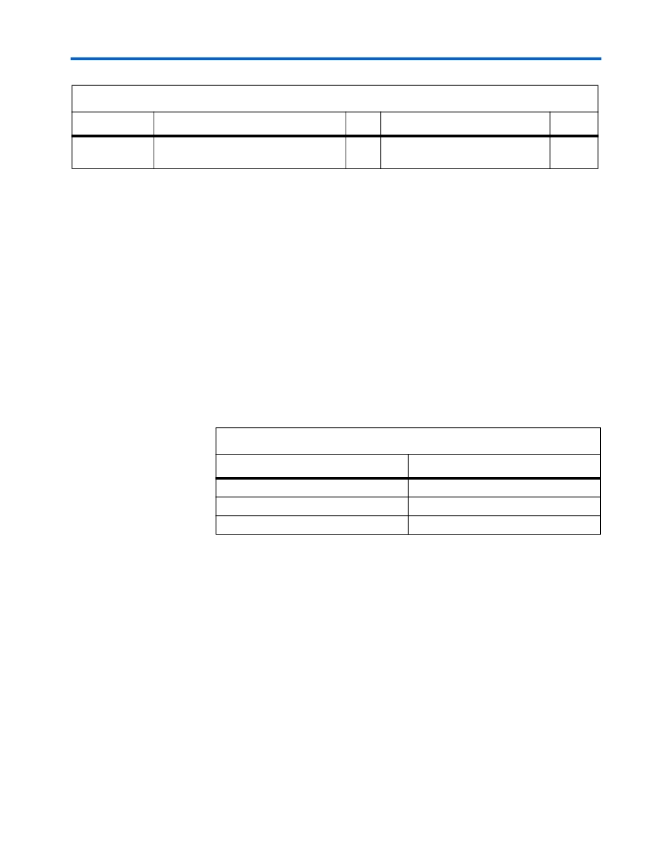

Table 4–134. DLL Jitter for DQS Phase Shift Reference Circuit

Frequency (MHz)

DLL Jitter (ps)

197 to 200

±

100

160 to 196

±

300

100 to 159

±

500

相关PDF资料 |

PDF描述 |

|---|---|

| EP20K100 | Programmable Logic Device Family |

| EP20K1000E | Programmable Logic Device Family |

| EP20K100E | Programmable Logic Device Family |

| EP20K1500E | Programmable Logic Device Family |

| EP20K160E | Programmable Logic Device Family |

相关代理商/技术参数 |

参数描述 |

|---|---|

| EP1S80F1508C7N | 功能描述:FPGA - 现场可编程门阵列 FPGA - Stratix I 7904 LABs 1203 IO RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 栅极数量: 逻辑块数量:943 内嵌式块RAM - EBR:1956 kbit 输入/输出端数量:128 最大工作频率:800 MHz 工作电源电压:1.1 V 最大工作温度:+ 70 C 安装风格:SMD/SMT 封装 / 箱体:FBGA-256 |

| EP1S80F1508I5ES | 制造商:ALTERA 制造商全称:Altera Corporation 功能描述:Stratix Device Family Data Sheet |

| EP1S80F1508I6ES | 制造商:ALTERA 制造商全称:Altera Corporation 功能描述:Stratix Device Family Data Sheet |

| EP1S80F1508I7 | 功能描述:FPGA - 现场可编程门阵列 FPGA - Stratix I 7904 LABs 1203 IO RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 栅极数量: 逻辑块数量:943 内嵌式块RAM - EBR:1956 kbit 输入/输出端数量:128 最大工作频率:800 MHz 工作电源电压:1.1 V 最大工作温度:+ 70 C 安装风格:SMD/SMT 封装 / 箱体:FBGA-256 |

| EP1S80F1508I7ES | 制造商:ALTERA 制造商全称:Altera Corporation 功能描述:Stratix Device Family Data Sheet |

发布紧急采购,3分钟左右您将得到回复。