- 您现在的位置:买卖IC网 > PDF目录299030 > EP20K100BC324-2 (ALTERA CORP) LOADABLE PLD, PBGA324 PDF资料下载

参数资料

| 型号: | EP20K100BC324-2 |

| 厂商: | ALTERA CORP |

| 元件分类: | PLD |

| 英文描述: | LOADABLE PLD, PBGA324 |

| 文件页数: | 29/68页 |

| 文件大小: | 975K |

| 代理商: | EP20K100BC324-2 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页当前第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页

35

4317K–AVR–03/2013

AT90PWM2/3/2B/3B

Note that this oscillator is used to time EEPROM and Flash write accesses, and these write

times will be affected accordingly. If the EEPROM or Flash are written, do not calibrate to more

than 8.8 MHz. Otherwise, the EEPROM or Flash write may fail.

The CAL7 bit determines the range of operation for the oscillator. Setting this bit to 0 gives the

lowest frequency range, setting this bit to 1 gives the highest frequency range. The two fre-

quency ranges are overlapping, in other words a setting of OSCCAL = 0x7F gives a higher

frequency than OSCCAL = 0x80.

The CAL6..0 bits are used to tune the frequency within the selected range. A setting of 0x00

gives the lowest frequency in that range, and a setting of 0x7F gives the highest frequency in the

range. Incrementing CAL6..0 by 1 will give a frequency increment of less than 2% in the fre-

quency range 7.3 - 8.1 MHz.

7.6

PLL

To generate high frequency and accurate PWM waveforms, the ‘PSC’s need high frequency

clock input. This clock is generated by a PLL. To keep all PWM accuracy, the frequency factor of

PLL must be configurable by software. With a system clock of 8 MHz, the PLL output is 32Mhz

or 64Mhz.

7.6.1

Internal PLL for PSC

The internal PLL in AT90PWM2/2B/3/3B generates a clock frequency that is 64x multiplied from

nominally 1 MHz input. The source of the 1 MHz PLL input clock is the output of the internal RC

Oscillator which is divided down to 1 MHz. See the Figure 7-4 on page 36.

The PLL is locked on the RC Oscillator and adjusting the RC Oscillator via OSCCAL Register

will adjust the fast peripheral clock at the same time. However, even if the possibly divided RC

Oscillator is taken to a higher frequency than 1 MHz, the fast peripheral clock frequency satu-

rates at 70 MHz (worst case) and remains oscillating at the maximum frequency. It should be

noted that the PLL in this case is not locked any more with the RC Oscillator clock.

Therefore it is recommended not to take the OSCCAL adjustments to a higher frequency than 1

MHz in order to keep the PLL in the correct operating range. The internal PLL is enabled only

when the PLLE bit in the register PLLCSR is set. The bit PLOCK from the register PLLCSR is

set when PLL is locked.

Both internal 1 MHz RC Oscillator and PLL are switched off in Power-down and Standby sleep

modes

.

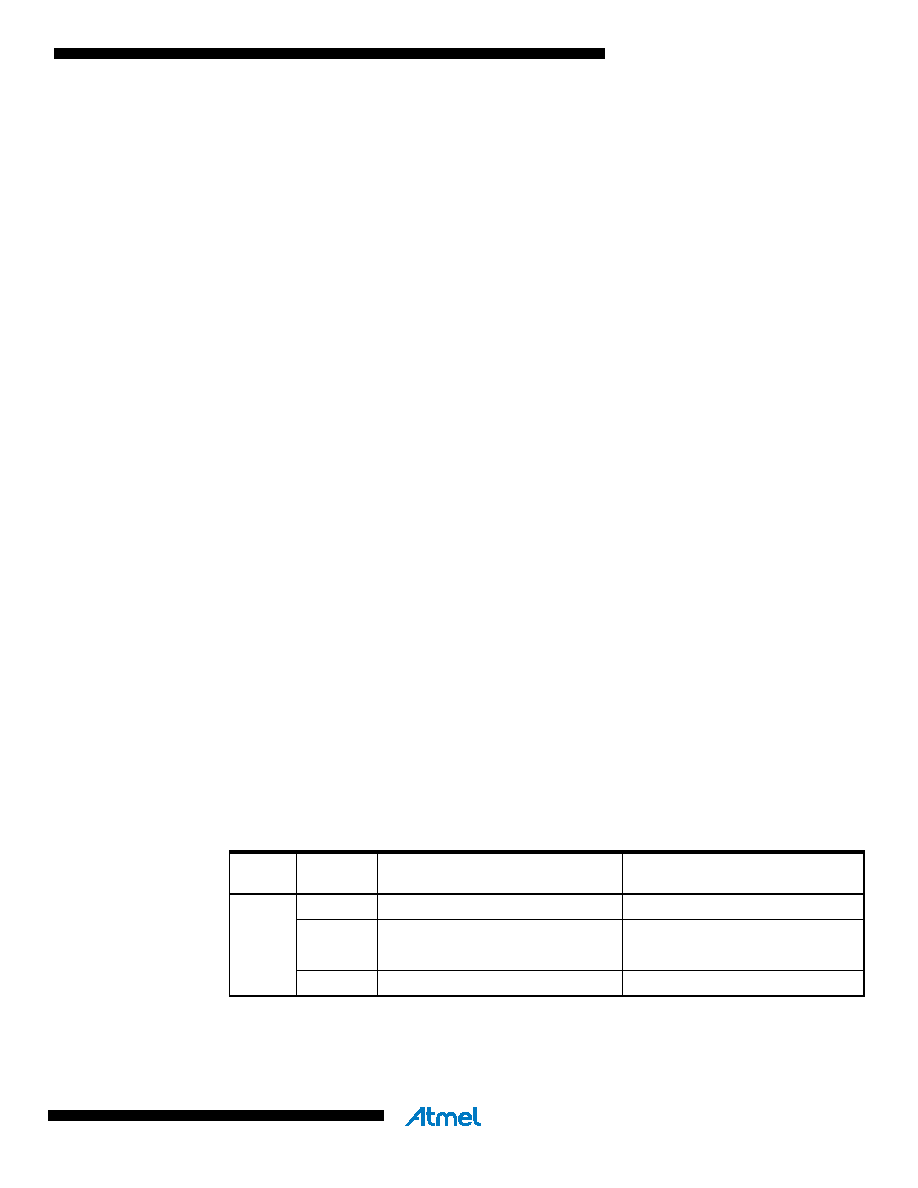

Table 7-9.

Start-up Times when the PLL is selected as system clock

CKSEL

3..0

SUT1..0

Start-up Time from Power-down

and Power-save

Additional Delay from Reset

(V

CC = 5.0V)

0011

RC Osc

00

1K CK

14CK

01

1K CK

14CK + 4 ms

10

1K CK

14CK + 64 ms

11

16K CK

14CK

相关PDF资料 |

PDF描述 |

|---|---|

| EP20K100BC324-3 | LOADABLE PLD, PBGA324 |

| EP20K100BI324-1 | LOADABLE PLD, PBGA324 |

| EP20K100BI324-2 | LOADABLE PLD, PBGA324 |

| EP20K100BI324-3 | LOADABLE PLD, PBGA324 |

| EP20K100BC484-1 | LOADABLE PLD, PBGA484 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| EP20K100BC356-1 | 功能描述:FPGA - 现场可编程门阵列 CPLD - APEX 20K 416 Macro 252 IOs RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 栅极数量: 逻辑块数量:943 内嵌式块RAM - EBR:1956 kbit 输入/输出端数量:128 最大工作频率:800 MHz 工作电源电压:1.1 V 最大工作温度:+ 70 C 安装风格:SMD/SMT 封装 / 箱体:FBGA-256 |

| EP20K100BC356-1ES | 制造商:未知厂家 制造商全称:未知厂家 功能描述:FPGA |

| EP20K100BC356-1V | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| EP20K100BC356-2 | 功能描述:FPGA - 现场可编程门阵列 CPLD - APEX 20K 416 Macro 252 IOs RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 栅极数量: 逻辑块数量:943 内嵌式块RAM - EBR:1956 kbit 输入/输出端数量:128 最大工作频率:800 MHz 工作电源电压:1.1 V 最大工作温度:+ 70 C 安装风格:SMD/SMT 封装 / 箱体:FBGA-256 |

| EP20K100BC356-2ES | 制造商:未知厂家 制造商全称:未知厂家 功能描述:FPGA |

发布紧急采购,3分钟左右您将得到回复。