参数资料

| 型号: | EP20K400EFC672-3N |

| 厂商: | Altera |

| 文件页数: | 68/117页 |

| 文件大小: | 0K |

| 描述: | IC APEX 20KE FPGA 400K 672-FBGA |

| 产品培训模块: | Three Reasons to Use FPGA's in Industrial Designs |

| 标准包装: | 40 |

| 系列: | APEX-20K® |

| LAB/CLB数: | 1664 |

| 逻辑元件/单元数: | 16640 |

| RAM 位总计: | 212992 |

| 输入/输出数: | 488 |

| 门数: | 1052000 |

| 电源电压: | 1.71 V ~ 1.89 V |

| 安装类型: | 表面贴装 |

| 工作温度: | 0°C ~ 85°C |

| 封装/外壳: | 672-BBGA |

| 供应商设备封装: | 672-BGA(27x27) |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页当前第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页第111页第112页第113页第114页第115页第116页第117页

54

Altera Corporation

APEX 20K Programmable Logic Device Family Data Sheet

(1)

All input clock specifications must be met. The PLL may not lock onto an incoming clock if the clock specifications

are not met, creating an erroneous clock within the device.

(2)

The maximum lock time is 40 s or 2000 input clock cycles, whichever occurs first.

(3)

Before configuration, the PLL circuits are disable and powered down. During configuration, the PLLs are still

disabled. The PLLs begin to lock once the device is in the user mode. If the clock enable feature is used, lock begins

once the CLKLK_ENA pin goes high in user mode.

(4)

The PLL VCO operating range is 200 MHz fVCO 840 MHz for LVDS mode.

SignalTap

Embedded

Logic Analyzer

APEX 20K devices include device enhancements to support the SignalTap

embedded logic analyzer. By including this circuitry, the APEX 20K

device provides the ability to monitor design operation over a period of

time through the IEEE Std. 1149.1 (JTAG) circuitry; a designer can analyze

internal logic at speed without bringing internal signals to the I/O pins.

This feature is particularly important for advanced packages such as

FineLine BGA packages because adding a connection to a pin during the

debugging process can be difficult after a board is designed and

manufactured.

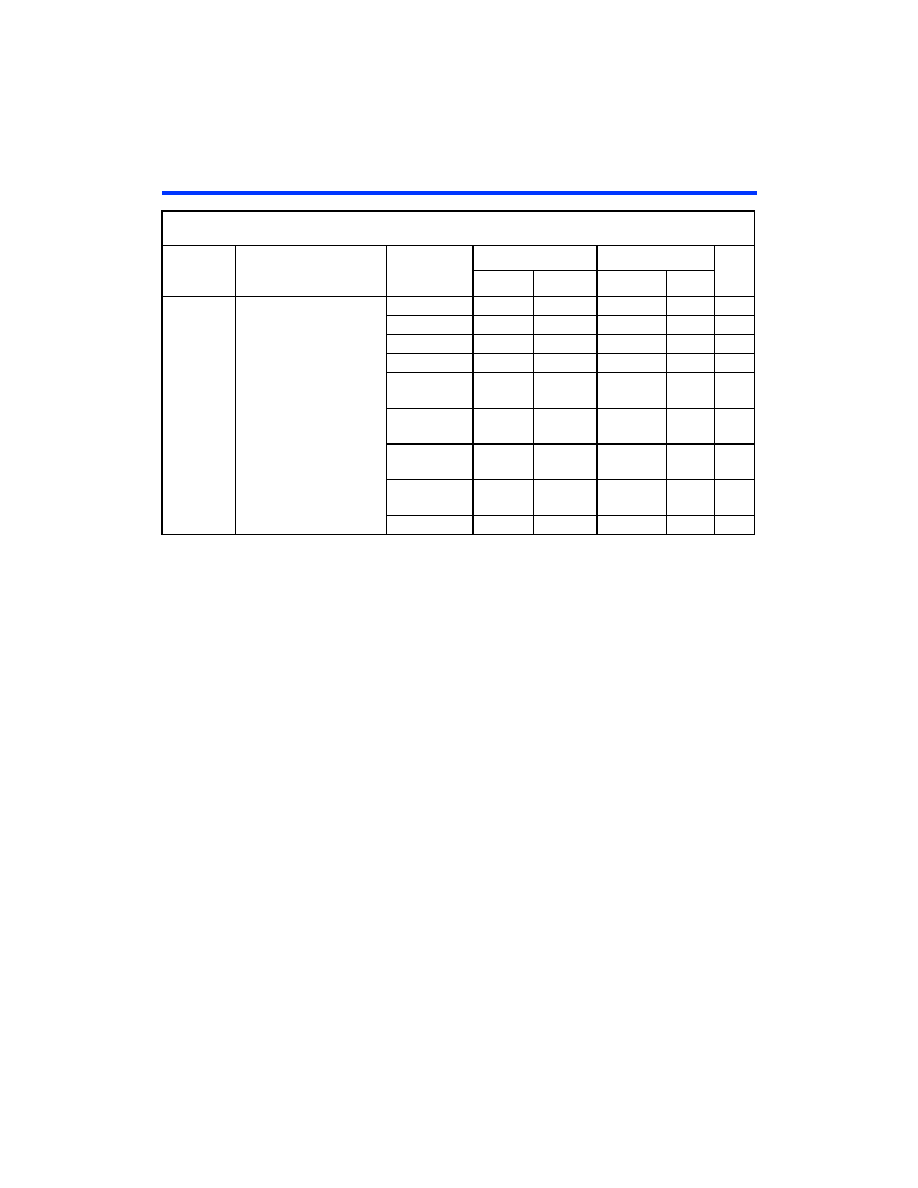

fIN

Input clock frequency

3.3-V LVTTL

1.5

290

1.5

257

MHz

2.5-V LVTTL

1.5

281

1.5

250

MHz

1.8-V LVTTL

1.5

272

1.5

243

MHz

GTL+

1.5

303

1.5

261

MHz

SSTL-2 Class

I

1.5

291

1.5

253

MHz

SSTL-2 Class

II

1.5

291

1.5

253

MHz

SSTL-3 Class

I

1.5

300

1.5

260

MHz

SSTL-3 Class

II

1.5

300

1.5

260

MHz

LVDS

1.5

420

1.5

350

MHz

Table 18. APEX 20KE Clock Input & Output Parameters

(Part 2 of 2)

Note (1)

Symbol

Parameter

I/O Standard

-1X Speed Grade

-2X Speed Grade

Units

Min

Max

Min

Max

相关PDF资料 |

PDF描述 |

|---|---|

| EP20K400EFC672-3 | IC APEX 20KE FPGA 400K 672-FBGA |

| IDT70V25L20PFI | IC SRAM 128KBIT 20NS 100TQFP |

| ACM44DRAN | CONN EDGECARD 88POS .156 R/A |

| A54SX16P-PQ208M | IC FPGA SX 24K GATES 208-PQFP |

| A54SX16P-PQG208M | IC FPGA SX 24K GATES 208-PQFP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| EP20K400EFI672-1ES | 制造商:未知厂家 制造商全称:未知厂家 功能描述:FPGA |

| EP20K400EFI672-2ES | 制造商:未知厂家 制造商全称:未知厂家 功能描述:FPGA |

| EP20K400EFI672-2N | 功能描述:FPGA - 现场可编程门阵列 CPLD - APEX 20K 1664 Macros 488 IO RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 栅极数量: 逻辑块数量:943 内嵌式块RAM - EBR:1956 kbit 输入/输出端数量:128 最大工作频率:800 MHz 工作电源电压:1.1 V 最大工作温度:+ 70 C 安装风格:SMD/SMT 封装 / 箱体:FBGA-256 |

| EP20K400EFI672-2X | 功能描述:FPGA - 现场可编程门阵列 CPLD - APEX 20K 1664 Macros 488 IO RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 栅极数量: 逻辑块数量:943 内嵌式块RAM - EBR:1956 kbit 输入/输出端数量:128 最大工作频率:800 MHz 工作电源电压:1.1 V 最大工作温度:+ 70 C 安装风格:SMD/SMT 封装 / 箱体:FBGA-256 |

| EP20K400EFI672-3ES | 制造商:未知厂家 制造商全称:未知厂家 功能描述:FPGA |

发布紧急采购,3分钟左右您将得到回复。