- 您现在的位置:买卖IC网 > PDF目录97925 > EP20K600EBI652-2ES RTC Module With CPU Supervisor PDF资料下载

参数资料

| 型号: | EP20K600EBI652-2ES |

| 元件分类: | CPU监测 |

| 英文描述: | RTC Module With CPU Supervisor |

| 中文描述: | 时钟模块CPU监控 |

| 文件页数: | 92/114页 |

| 文件大小: | 1623K |

| 代理商: | EP20K600EBI652-2ES |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页当前第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页第111页第112页第113页第114页

Altera Corporation

79

APEX 20K Programmable Logic Device Family Data Sheet

Note to tables:

(1)

These timing parameters are sample-tested only.

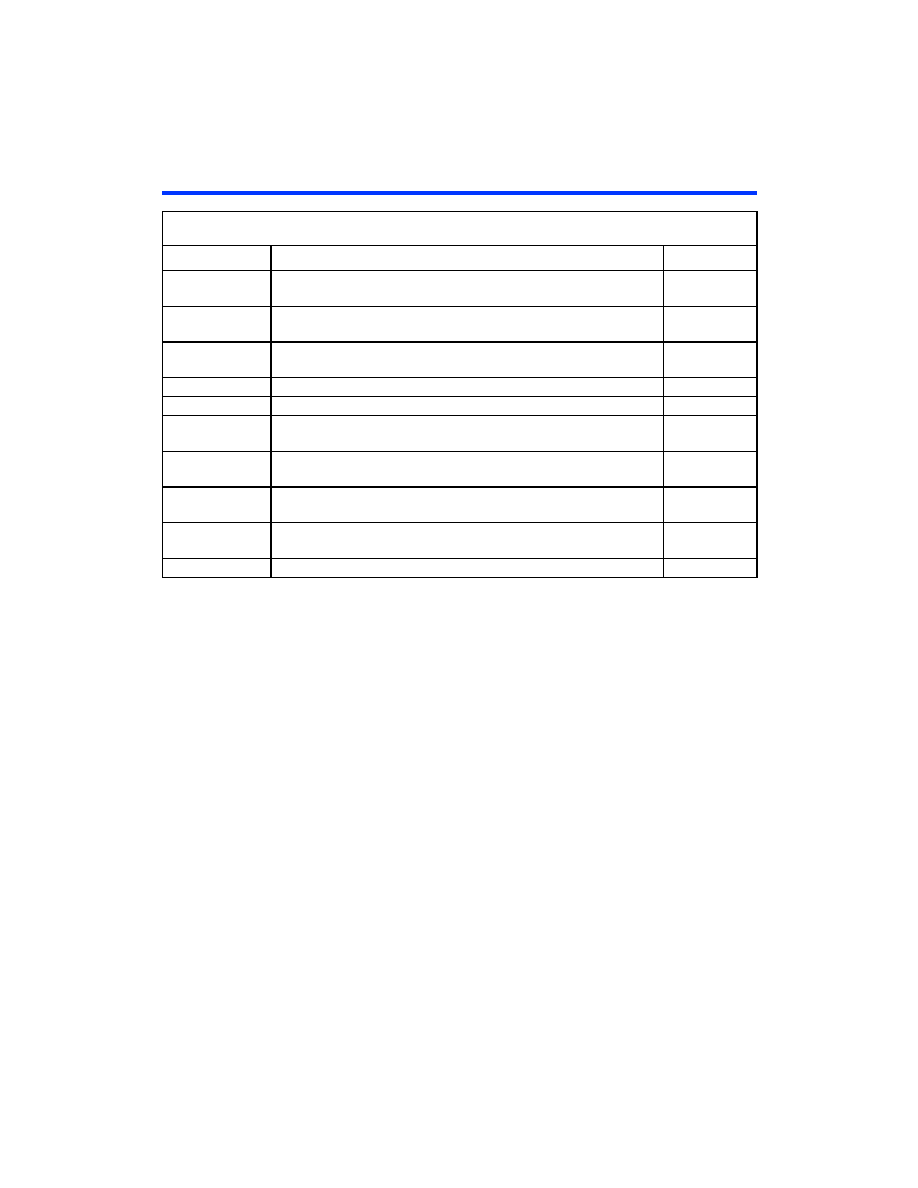

Table 43. APEX 20KE External Bidirectional Timing Parameters

Symbol

Parameter

Condition

tINSUBIDIR

Setup time for bi-directional pins with global clock at LAB adjacent Input

Register

tINHBIDIR

Hold time for bi-directional pins with global clock at LabB adjacent Input

Register

tOUTCOBIDIR

Clock-to-output delay for bi-directional pins with global clock at IOE output

register

C1 = 35 pF

tXZBIDIR

Synchronous Output Enable Register to output buffer disable delay

C1 = 35 pF

tZXBIDIR

Synchronous Output Enable Register output buffer enable delay

C1 = 35 pF

tINSUBIDIRPLL

Setup time for bi-directional pins with PLL clock at LAB adjacent Input

Register

tINHBIDIRPLL

Hold time for bi-directional pins with PLL clock at LAB adjacent Input

Register

tOUTCOBIDIRPLL

Clock-to-output delay for bi-directional pins with PLL clock at IOE output

register

C1 = 35 pF

tXZBIDIRPLL

Synchronous Output Enable Register to output buffer disable delay with

PLL

C1 = 35 pF

tZXBIDIRPLL

Synchronous Output Enable Register output buffer enable delay with PLL

C1 = 35 pF

相关PDF资料 |

PDF描述 |

|---|---|

| EP20K600EBI652-3ES | RTC Module With CPU Supervisor |

| EP20K600EFC1020-1 | RTC Module With CPU Supervisor |

| EP20K600EFC1020-1ES | FPGA |

| EP20K600EFC1020-1X | FPGA |

| EP20K600EFC1020-2 | FPGA |

相关代理商/技术参数 |

参数描述 |

|---|---|

| EP20K600EBI652-2X | 功能描述:FPGA - 现场可编程门阵列 CPLD - APEX 20K 2432 Macros 488 IO RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 栅极数量: 逻辑块数量:943 内嵌式块RAM - EBR:1956 kbit 输入/输出端数量:128 最大工作频率:800 MHz 工作电源电压:1.1 V 最大工作温度:+ 70 C 安装风格:SMD/SMT 封装 / 箱体:FBGA-256 |

| EP20K600EBI652-3ES | 制造商:未知厂家 制造商全称:未知厂家 功能描述:FPGA |

| EP20K600EFC1020-1 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:FPGA |

| EP20K600EFC1020-1ES | 制造商:未知厂家 制造商全称:未知厂家 功能描述:FPGA |

| EP20K600EFC1020-1X | 制造商:未知厂家 制造商全称:未知厂家 功能描述:FPGA |

发布紧急采购,3分钟左右您将得到回复。