参数资料

| 型号: | EP4SE530H35C3 |

| 厂商: | Altera |

| 文件页数: | 46/82页 |

| 文件大小: | 0K |

| 描述: | IC STRATIX IV FPGA 530K 1152HBGA |

| 产品培训模块: | Three Reasons to Use FPGA's in Industrial Designs |

| 标准包装: | 3 |

| 系列: | STRATIX® IV E |

| LAB/CLB数: | 21248 |

| 逻辑元件/单元数: | 531200 |

| RAM 位总计: | 28033024 |

| 输入/输出数: | 744 |

| 电源电压: | 0.87 V ~ 0.93 V |

| 安装类型: | 表面贴装 |

| 工作温度: | 0°C ~ 85°C |

| 封装/外壳: | 1152-BBGA 裸露焊盘 |

| 供应商设备封装: | 1152-HBGA(40x40) |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页当前第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页

1–42

Chapter 1: DC and Switching Characteristics for Stratix IV Devices

Switching Characteristics

Stratix IV Device Handbook

March 2014

Altera Corporation

Volume 4: Device Datasheet and Addendum

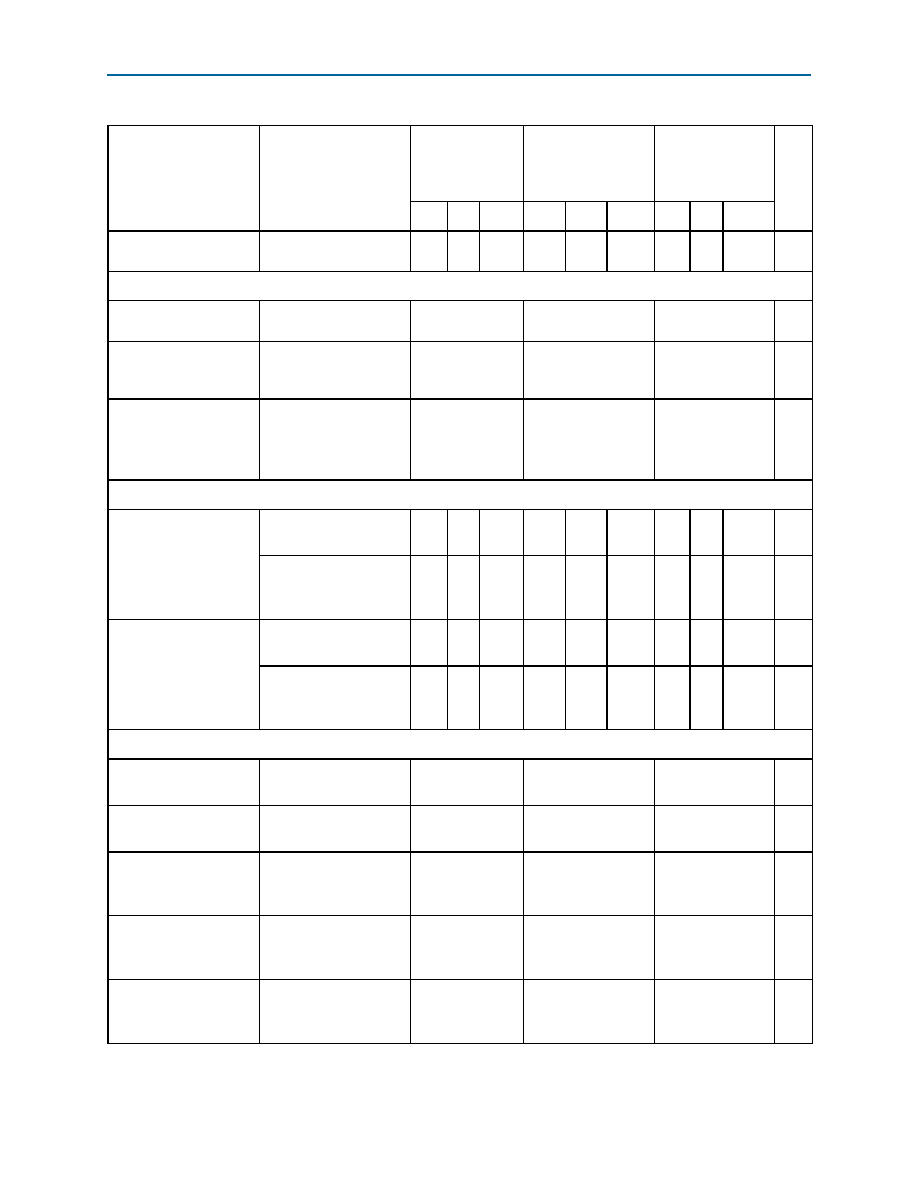

Random jitter at

6.0 Gbps (G3)

Pattern = CJPAT

—

0.15

—

0.15

—

0.15

UI

SAS Receiver Jitter Tolerance (17)

Total Jitter tolerance at

1.5 Gbps (G1)

Pattern = CJPAT

> 0.65

UI

Deterministic Jitter

tolerance at 1.5 Gbps

(G1)

Pattern = CJPAT

> 0.35

UI

Sinusoidal Jitter

tolerance at 1.5 Gbps

(G1)

Jitter Frequency = 900

KHz to 5 MHz

Pattern = CJTPAT BER =

1E-12

> 0.1

UI

CPRI Transmit Jitter Generation (18)

Total Jitter

E.6.HV, E.12.HV

Pattern = CJPAT

—

0.279

—

0.279

—

0.279

UI

E.6.LV, E.12.LV, E.24.LV,

E.30.LV

Pattern = CJTPAT

—

0.35

—

0.35

—

0.35

UI

Deterministic Jitter

E.6.HV, E.12.HV

Pattern = CJPAT

—

0.14

—

0.14

—

0.14

UI

E.6.LV, E.12.LV, E.24.LV,

E.30.LV

Pattern = CJTPAT

—

0.17

—

0.17

—

0.17

UI

CPRI Receiver Jitter Tolerance (18)

Total jitter tolerance

E.6.HV, E.12.HV

Pattern = CJPAT

> 0.66

UI

Deterministic jitter

tolerance

E.6.HV, E.12.HV

Pattern = CJPAT

> 0.4

UI

Total jitter tolerance

E.6.LV, E.12.LV, E.24.LV,

E.30.LV

Pattern = CJTPAT

> 0.65

UI

Deterministic jitter

tolerance

E.6.LV, E.12.LV, E.24.LV,

E.30.LV

Pattern = CJTPAT

> 0.37

UI

Combined deterministic

and random jitter

tolerance

E.6.LV, E.12.LV, E.24.LV,

E.30.LV

Pattern = CJTPAT

> 0.55

UI

Table 1–30. Transceiver Block Jitter Specifications for Stratix IV GX Devices (1), (2) (Part 7 of 9)

Symbol/

Description

Conditions

–2 Commercial

Speed Grade

–3 Commercial/

Industrial

and –2× Commercial

Speed Grade

–3 Military (3) and

–4 Commercial/

Industrial Speed

Grade

Unit

Min

Typ

Max

Min

Typ

Max

Min Typ

Max

相关PDF资料 |

PDF描述 |

|---|---|

| HMC65DREF | CONN EDGECARD 130POS .100 EYELET |

| EMC61DRST-S273 | CONN EDGECARD 122PS DIP .100 SLD |

| ASM40DRMI | CONN EDGECARD 80POS .156 SQ WW |

| 170-101-170L002 | CONN PIN STAMPED 24-28AWG 10GOLD |

| ASC50DRTI-S734 | CONN EDGECARD 100PS DIP .100 SLD |

相关代理商/技术参数 |

参数描述 |

|---|---|

| EP4SE530H35C3ES | 功能描述:IC STRATIX IV E 530K 1152-HBGA RoHS:否 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:STRATIX® IV E 产品变化通告:XC4000(E,L) Discontinuation 01/April/2002 标准包装:24 系列:XC4000E/X LAB/CLB数:100 逻辑元件/单元数:238 RAM 位总计:3200 输入/输出数:80 门数:3000 电源电压:4.5 V ~ 5.5 V 安装类型:表面贴装 工作温度:-40°C ~ 100°C 封装/外壳:120-BCBGA 供应商设备封装:120-CPGA(34.55x34.55) |

| EP4SE530H35C3N | 功能描述:FPGA - 现场可编程门阵列 FPGA - Stratix IV E 21248 LABs 744 IOs RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 栅极数量: 逻辑块数量:943 内嵌式块RAM - EBR:1956 kbit 输入/输出端数量:128 最大工作频率:800 MHz 工作电源电压:1.1 V 最大工作温度:+ 70 C 安装风格:SMD/SMT 封装 / 箱体:FBGA-256 |

| EP4SE530H35C3NES | 功能描述:IC STRATIX IV E 530K 1152-HBGA RoHS:是 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:STRATIX® IV E 产品变化通告:XC4000(E,L) Discontinuation 01/April/2002 标准包装:24 系列:XC4000E/X LAB/CLB数:100 逻辑元件/单元数:238 RAM 位总计:3200 输入/输出数:80 门数:3000 电源电压:4.5 V ~ 5.5 V 安装类型:表面贴装 工作温度:-40°C ~ 100°C 封装/外壳:120-BCBGA 供应商设备封装:120-CPGA(34.55x34.55) |

| EP4SE530H35C4 | 功能描述:FPGA - 现场可编程门阵列 FPGA - Stratix IV E 21248 LABs 744 IOs RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 栅极数量: 逻辑块数量:943 内嵌式块RAM - EBR:1956 kbit 输入/输出端数量:128 最大工作频率:800 MHz 工作电源电压:1.1 V 最大工作温度:+ 70 C 安装风格:SMD/SMT 封装 / 箱体:FBGA-256 |

| EP4SE530H35C4ES | 制造商:Altera Corporation 功能描述:IC STRATIX IV E FPGA 1152HBGA 制造商:Altera Corporation 功能描述:IC FPGA 744 I/O 1152HBGA |

发布紧急采购,3分钟左右您将得到回复。