- 您现在的位置:买卖IC网 > PDF目录19910 > EPC4QC100N (Altera)IC CONFIG DEVICE 4MBIT 100-PQFP PDF资料下载

参数资料

| 型号: | EPC4QC100N |

| 厂商: | Altera |

| 文件页数: | 18/36页 |

| 文件大小: | 0K |

| 描述: | IC CONFIG DEVICE 4MBIT 100-PQFP |

| 产品培训模块: | Three Reasons to Use FPGA's in Industrial Designs |

| 标准包装: | 66 |

| 系列: | EPC |

| 可编程类型: | 系统内可编程 |

| 存储容量: | 4Mb |

| 电源电压: | 3 V ~ 3.6 V |

| 工作温度: | 0°C ~ 70°C |

| 封装/外壳: | 100-BQFP |

| 供应商设备封装: | 100-PQFP(14x20) |

| 包装: | 托盘 |

| 产品目录页面: | 604 (CN2011-ZH PDF) |

| 其它名称: | 544-1378 EPC4QC100N-ND |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页当前第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页

Power-On Reset

Page 25

Enhanced Configuration (EPC) Devices Datasheet

January 2012

Altera Corporation

Power-On Reset

The POR circuit keeps the system in reset until power-supply voltage levels have

stabilized. The POR time consists of the VCC ramp time and a user-programmable

POR delay counter. When the supply is stable and the POR counter expires, the POR

circuit releases the OE pin. The POR time can be further extended by an external

device by driving the OE pin low.

1 Do not execute JTAG or ISP instructions until POR is complete.

The EPC device supports a programmable POR delay setting. You can set the POR

delay to the default 100-ms setting or reduce the POR delay to 2 ms for systems that

require fast power-up. The PORSEL input pin controls this POR delay—a logic-high

level selects the 2-ms delay, while a logic-low level selects the 100-ms delay.

The EPC device enters reset under the following conditions:

■

The POR reset starts at initial power-up during VCC ramp-up or if VCC drops

below the minimum operating condition anytime after VCC has stabilized

■

The FPGA initiates reconfiguration by driving nSTATUS low, which occurs if the

FPGA detects a CRC error or if the FPGA’s nCONFIG input pin is asserted

■

The controller detects a configuration error and asserts OE to begin reconfiguration

of the Altera FPGA (for example, when CONF_DONE stays low after all configuration

data has been transmitted)

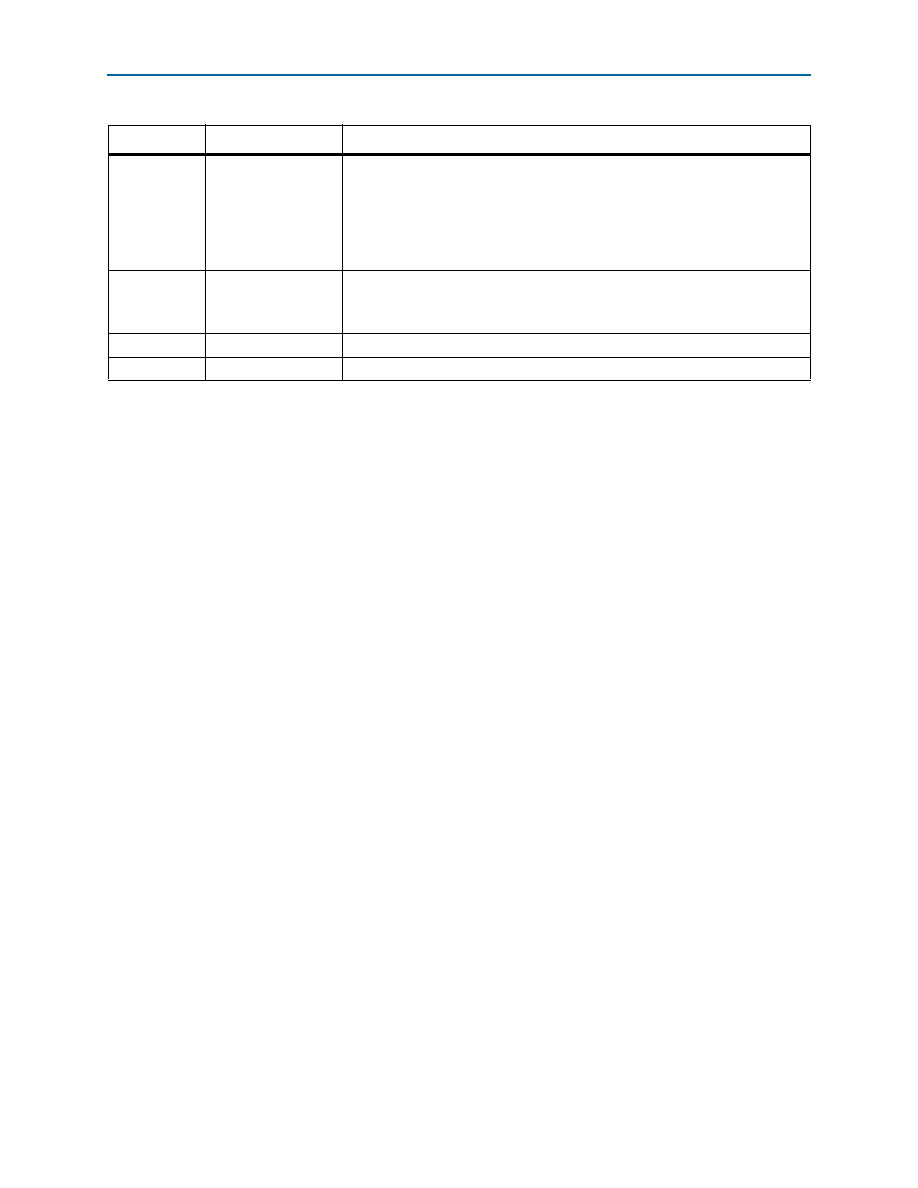

EXCLK

Input

Optional external clock input pin that can be used to generate the configuration

clock (DCLK).

When an external clock source is not used, connect this pin to a valid logic level

(high or low) to prevent a floating-input buffer. If EXCLK is used, toggling the

EXCLK

input pin after the FPGA enters user mode will not effect the EPC device

operation.

PORSEL

Input

This pin selects a 2-ms or 100-ms POR counter delay during power up. When

PORSEL

is low, POR time is 100 ms. When PORSEL is high, POR time is 2 ms.

This pin must be connected to a valid logic level.

TM0

Input

For normal operation, this test pin must be connected to GND.

TM1

Input

For normal operation, this test pin must be connected to VCC.

Table 10. JTAG Interface Pins and Other Required Controller Pins (Part 2 of 2)

Pin Name

Pin Type

Description

相关PDF资料 |

PDF描述 |

|---|---|

| V24C48H100BL | CONVERTER MOD DC/DC 48V 100W |

| XCF01SVO20C | IC PROM IN SYST PRG 3.3V 20TSSOP |

| HSC36DREH-S93 | CONN EDGECARD 72POS .100 EYELET |

| EBM15DCCS | CONN EDGECARD 30POS R/A .156 SLD |

| EPC2TC32N | IC CONFIG DEVICE 1.6MBIT 32-TQFP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| EPC4QI100 | 功能描述:FPGA-配置存储器 IC - Ser. Config Mem Flash 4Mb 66 MHz RoHS:否 制造商:Altera Corporation 存储类型:Flash 存储容量:1.6 Mbit 工作频率:10 MHz 电源电压-最大:5.25 V 电源电压-最小:3 V 电源电流:50 uA 最大工作温度:+ 85 C 最小工作温度:- 40 C 安装风格:SMD/SMT 封装 / 箱体:PLCC-20 |

| EPC4QI100N | 功能描述:FPGA-配置存储器 IC - Ser. Config Mem Flash 4Mb 66 MHz RoHS:否 制造商:Altera Corporation 存储类型:Flash 存储容量:1.6 Mbit 工作频率:10 MHz 电源电压-最大:5.25 V 电源电压-最小:3 V 电源电流:50 uA 最大工作温度:+ 85 C 最小工作温度:- 40 C 安装风格:SMD/SMT 封装 / 箱体:PLCC-20 |

| EPC4XXX | 制造商:ALTERA 制造商全称:Altera Corporation 功能描述:2. Enhanced Configuration Devices (EPC4, EPC8 & EPC16) Data Sheet |

| EPC50C605 | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| EPC-525-0.5 | 制造商:EPIGAP 制造商全称:EPIGAP 功能描述:Photodiode-Chip |

发布紧急采购,3分钟左右您将得到回复。