参数资料

| 型号: | EPF8636AQC160-3 |

| 厂商: | Altera |

| 文件页数: | 27/62页 |

| 文件大小: | 0K |

| 描述: | IC FLEX 8000A FPGA 6K 160-PQFP |

| 产品培训模块: | Three Reasons to Use FPGA's in Industrial Designs |

| 标准包装: | 72 |

| 系列: | FLEX 8000 |

| LAB/CLB数: | 63 |

| 逻辑元件/单元数: | 504 |

| 输入/输出数: | 118 |

| 门数: | 6000 |

| 电源电压: | 4.75 V ~ 5.25 V |

| 安装类型: | 表面贴装 |

| 工作温度: | 0°C ~ 85°C |

| 封装/外壳: | 160-BQFP |

| 供应商设备封装: | 160-PQFP(28x28) |

| 其它名称: | 544-2261 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页当前第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页

Altera Corporation

33

FLEX 8000 Programmable Logic Device Family Data Sheet

FL

EX

800

0

3

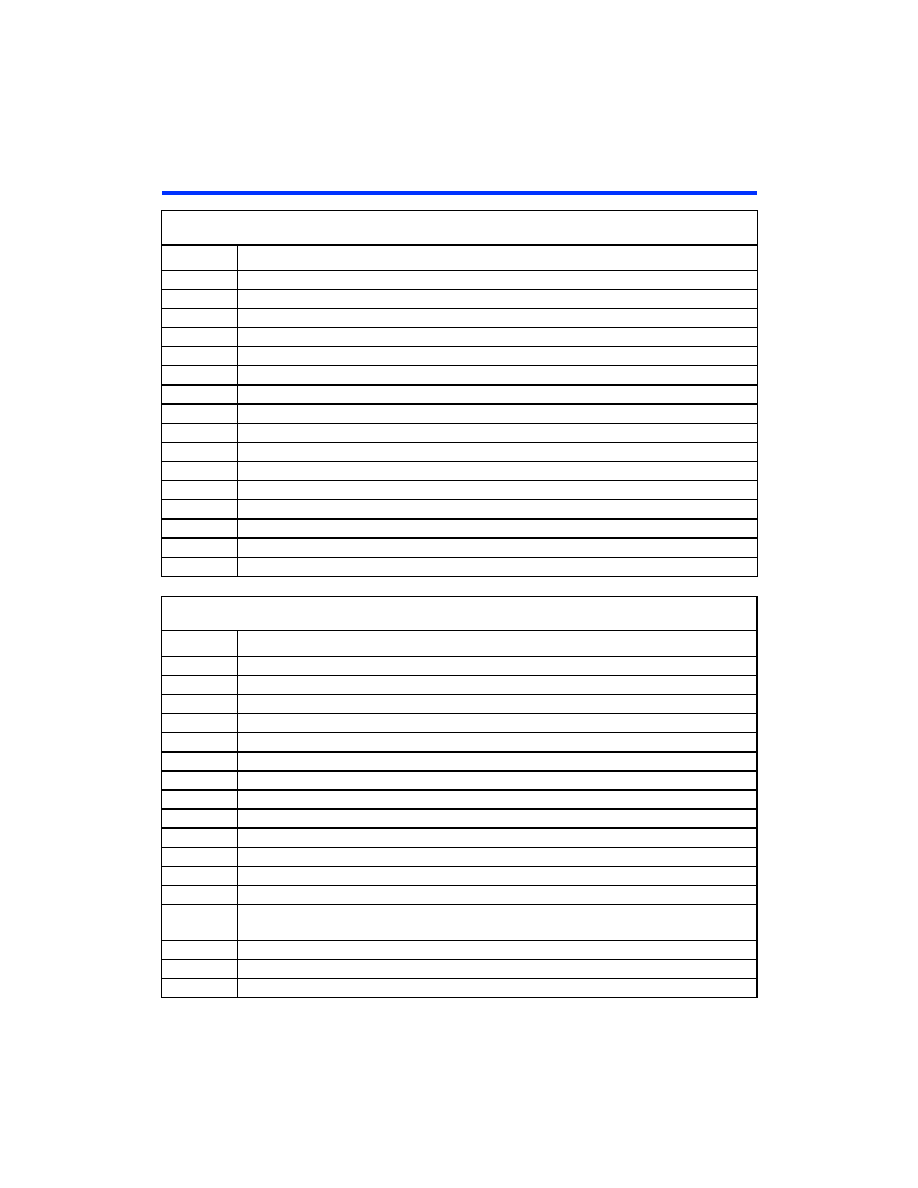

Table 17. FLEX 8000 Internal Timing Parameters

Symbol

Parameter

t IOD

IOE register data delay

t IOC

IOE register control signal delay

t IOE

Output enable delay

t IOCO

IOE register clock-to-output delay

t IOCOMB

IOE combinatorial delay

t IOSU

IOE register setup time before clock; IOE register recovery time after asynchronous clear

t IOH

IOE register hold time after clock

t IOCLR

IOE register clear delay

t IN

Input pad and buffer delay

t OD1

t OD2

t OD3

Output buffer and pad delay, slow slew rate = on, C1 = 35 pF (3)

t XZ

Output buffer disable delay, C1 = 5 pF

t ZX1

t ZX2

t ZX3

Output buffer enable delay, slow slew rate = on, C1 = 35 pF (3)

Table 18. FLEX 8000 LE Timing Parameters

Symbol

Parameter

t LUT

LUT delay for data-in

t CLUT

LUT delay for carry-in

t RLUT

LUT delay for LE register feedback

t GATE

Cascade gate delay

t CASC

Cascade chain routing delay

t CICO

Carry-in to carry-out delay

t CGEN

Data-in to carry-out delay

t CGENR

LE register feedback to carry-out delay

t C

LE register control signal delay

t CH

LE register clock high time

t CL

LE register clock low time

t CO

LE register clock-to-output delay

t COMB

Combinatorial delay

t SU

LE register setup time before clock; LE register recovery time after asynchronous preset, clear, or

load

t H

LE register hold time after clock

t PRE

LE register preset delay

t CLR

LE register clear delay

相关PDF资料 |

PDF描述 |

|---|---|

| A40MX02-3PQG100 | IC FPGA MX SGL CHIP 3K 100-PQFP |

| A40MX02-3PQ100 | IC FPGA MX SGL CHIP 3K 100-PQFP |

| M1AFS250-FG256 | IC FPGA 2MB FLASH 250K 256-FBGA |

| M1AFS250-FGG256 | IC FPGA 2MB FLASH 250K 256-FBGA |

| AFS250-FG256 | IC FPGA 2MB FLASH 250K 256FBGA |

相关代理商/技术参数 |

参数描述 |

|---|---|

| EPF8636AQC160-3N | 功能描述:FPGA - 现场可编程门阵列 FPGA - Flex 8000 63 LABs 118 IOs RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 栅极数量: 逻辑块数量:943 内嵌式块RAM - EBR:1956 kbit 输入/输出端数量:128 最大工作频率:800 MHz 工作电源电压:1.1 V 最大工作温度:+ 70 C 安装风格:SMD/SMT 封装 / 箱体:FBGA-256 |

| EPF8636AQC160-4 | 功能描述:FPGA - 现场可编程门阵列 FPGA - Flex 8000 63 LABs 118 IOs RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 栅极数量: 逻辑块数量:943 内嵌式块RAM - EBR:1956 kbit 输入/输出端数量:128 最大工作频率:800 MHz 工作电源电压:1.1 V 最大工作温度:+ 70 C 安装风格:SMD/SMT 封装 / 箱体:FBGA-256 |

| EPF8636AQC160-4N | 功能描述:FPGA - 现场可编程门阵列 FPGA - Flex 8000 63 LABs 118 IOs RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 栅极数量: 逻辑块数量:943 内嵌式块RAM - EBR:1956 kbit 输入/输出端数量:128 最大工作频率:800 MHz 工作电源电压:1.1 V 最大工作温度:+ 70 C 安装风格:SMD/SMT 封装 / 箱体:FBGA-256 |

| EPF8636AQC208-2 | 功能描述:FPGA - 现场可编程门阵列 FPGA - Flex 8000 63 LABs 136 IOs RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 栅极数量: 逻辑块数量:943 内嵌式块RAM - EBR:1956 kbit 输入/输出端数量:128 最大工作频率:800 MHz 工作电源电压:1.1 V 最大工作温度:+ 70 C 安装风格:SMD/SMT 封装 / 箱体:FBGA-256 |

| EPF8636AQC208-3 | 功能描述:FPGA - 现场可编程门阵列 FPGA - Flex 8000 63 LABs 136 IOs RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 栅极数量: 逻辑块数量:943 内嵌式块RAM - EBR:1956 kbit 输入/输出端数量:128 最大工作频率:800 MHz 工作电源电压:1.1 V 最大工作温度:+ 70 C 安装风格:SMD/SMT 封装 / 箱体:FBGA-256 |

发布紧急采购,3分钟左右您将得到回复。