- 您现在的位置:买卖IC网 > PDF目录299033 > EPM3256AQC208-6 (ALTERA CORP) EE PLD, 6 ns, PQFP208 PDF资料下载

参数资料

| 型号: | EPM3256AQC208-6 |

| 厂商: | ALTERA CORP |

| 元件分类: | PLD |

| 英文描述: | EE PLD, 6 ns, PQFP208 |

| 封装: | PLASTIC, QFP-208 |

| 文件页数: | 1/43页 |

| 文件大小: | 716K |

| 代理商: | EPM3256AQC208-6 |

当前第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页

Altera Corporation

1

MAX 3000A

Programmable Logic

Device Family

July 1999, ver. 1.01

Data Sheet

A-DS-M3000A-01.01

Features...

s

High-performance, low-cost CMOS EEPROM-based programmable

logic devices (PLDs) built on a Multiple Array MatriX (MAX)

architecture (see Table 1)

s

3.3-V in-system programmability (ISP) through the built-in

IEEE Std. 1149.1 Joint Test Action Group (JTAG) interface with

advanced pin-locking capability

Preliminary

Information

s

Built-in boundary-scan test (BST) circuitry compliant with

IEEE Std. 1149.1-1990

s

Enhanced ISP features:

–

Enhanced ISP algorithm for faster programming

–

ISP_Done bit to ensure complete programming

–

Pull-up resistor on I/O pins during in-system programming

s

High-density PLDs ranging from 600 to 5,000 usable gates

s

4.5-ns pin-to-pin logic delays with counter frequencies of up to

192.3 MHz

s

MultiVoltTM I/O interface enabling the device core to run at 3.3 V,

while I/O pins are compatible with 5.0-V, 3.3-V, and 2.5-V logic

levels

s

Pin counts ranging from 44 to 208 in a variety of thin quad flat pack

(TQFP), plastic quad flat pack (PQFP), and plastic J-lead chip carrier

(PLCC) packages

s

Supports hot-socketing

s

Programmable interconnect array (PIA) continuous routing structure

for fast, predictable performance

s

Peripheral component interconnect (PCI) compatible

s

Bus friendly architecture including programmable slew-rate control

s

Open-drain output option

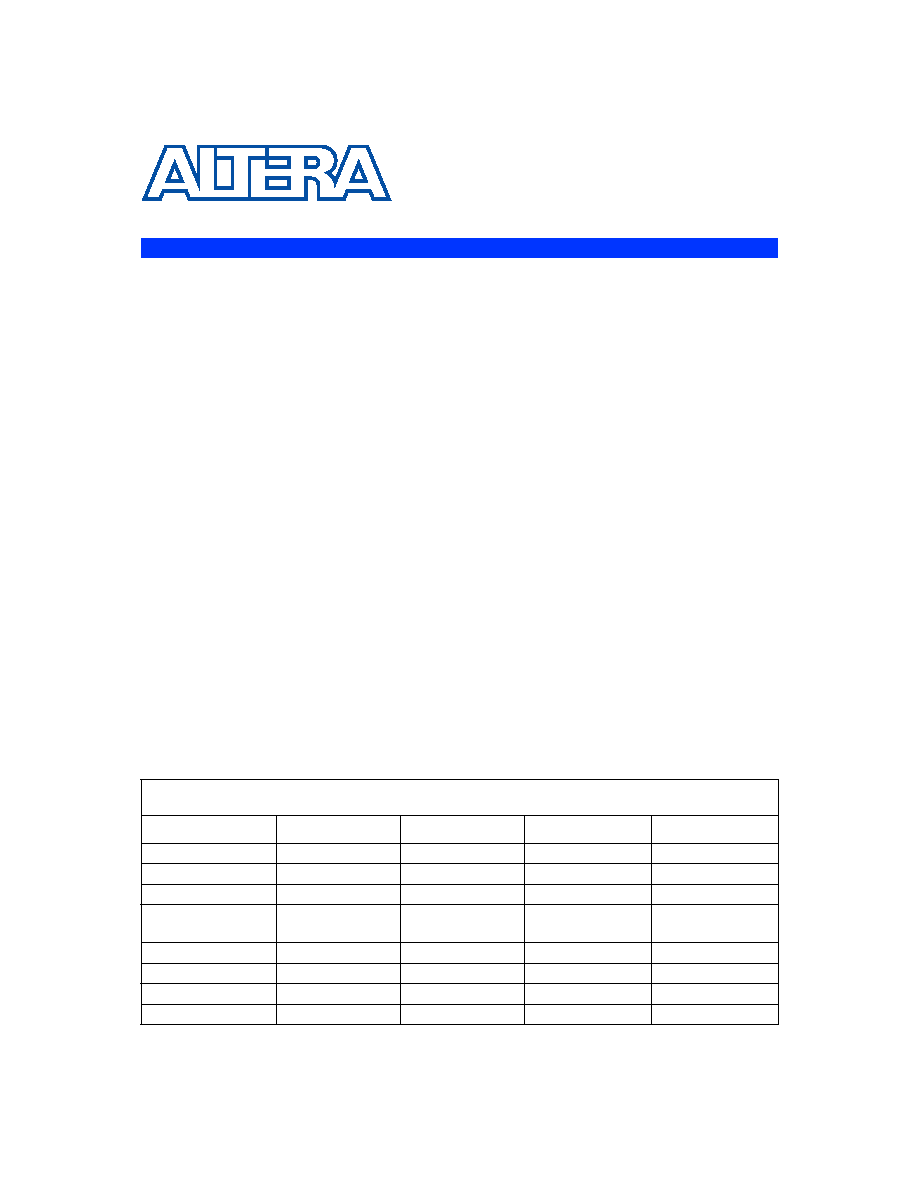

Table 1. MAX 3000A Device Features

Feature

EPM3032A

EPM3064A

EPM3128A

EPM3256A

Usable gates

600

1,250

2,500

5,000

Macrocells

32

64

128

256

Logic array blocks

2

4

8

16

Maximum user I/O

pins

34

66

96

158

tPD (ns)

4.5

5.0

6.0

tSU (ns)

3.0

3.2

3.7

tCO1 (ns)

2.8

3.0

3.3

fCNT (MHz)

192.3

181.8

156.3

相关PDF资料 |

PDF描述 |

|---|---|

| EPM3256AQI208-6 | EE PLD, 6 ns, PQFP208 |

| EPM7128ABC100-6 | EE PLD, 6 ns, PBGA100 |

| EPM7128ABC100-7 | EE PLD, 7.5 ns, PBGA100 |

| EPM7128ABI100-10 | EE PLD, 10 ns, PBGA100 |

| EPM7128ABI100-12 | EE PLD, 12 ns, PBGA100 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| EPM3256AQC208-7 | 功能描述:CPLD - 复杂可编程逻辑器件 CPLD - MAX 3000A 256 Macro 161 IOs RoHS:否 制造商:Lattice 系列: 存储类型:EEPROM 大电池数量:128 最大工作频率:333 MHz 延迟时间:2.7 ns 可编程输入/输出端数量:64 工作电源电压:3.3 V 最大工作温度:+ 90 C 最小工作温度:0 C 封装 / 箱体:TQFP-100 |

| EPM3256AQC208-7N | 功能描述:CPLD - 复杂可编程逻辑器件 CPLD - MAX 3000A 256 Macro 161 IOs RoHS:否 制造商:Lattice 系列: 存储类型:EEPROM 大电池数量:128 最大工作频率:333 MHz 延迟时间:2.7 ns 可编程输入/输出端数量:64 工作电源电压:3.3 V 最大工作温度:+ 90 C 最小工作温度:0 C 封装 / 箱体:TQFP-100 |

| EPM3256AQI208-10 | 功能描述:CPLD - 复杂可编程逻辑器件 CPLD - MAX 3000A 256 Macro 161 IOs RoHS:否 制造商:Lattice 系列: 存储类型:EEPROM 大电池数量:128 最大工作频率:333 MHz 延迟时间:2.7 ns 可编程输入/输出端数量:64 工作电源电压:3.3 V 最大工作温度:+ 90 C 最小工作温度:0 C 封装 / 箱体:TQFP-100 |

| EPM3256AQI208-10N | 功能描述:CPLD - 复杂可编程逻辑器件 CPLD - MAX 3000A 256 Macro 161 IOs RoHS:否 制造商:Lattice 系列: 存储类型:EEPROM 大电池数量:128 最大工作频率:333 MHz 延迟时间:2.7 ns 可编程输入/输出端数量:64 工作电源电压:3.3 V 最大工作温度:+ 90 C 最小工作温度:0 C 封装 / 箱体:TQFP-100 |

| EPM3256ATC100-5N | 制造商:ALTERA 制造商全称:Altera Corporation 功能描述:Higha??performance, lowa??cost CMOS EEPROMa??based programmable |

发布紧急采购,3分钟左右您将得到回复。