- 您现在的位置:买卖IC网 > PDF目录97933 > EPM9560RC208-15 PDF资料下载

参数资料

| 型号: | EPM9560RC208-15 |

| 文件页数: | 10/42页 |

| 文件大小: | 489K |

| 代理商: | EPM9560RC208-15 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页当前第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页

18

Altera Corporation

MAX 9000 Programmable Logic Device Family Data Sheet

The output buffer in each IOC has an adjustable output slew rate that can

be configured for low-noise or high-speed performance. A slower slew

rate reduces board-level noise and adds a nominal timing delay to the

output buffer delay (tOD) parameter. The fast slew rate should be used for

speed-critical outputs in systems that are adequately protected against

noise. Designers can specify the slew rate on a pin-by-pin basis during

design entry or assign a default slew rate to all pins on a global basis. The

slew rate control affects both rising and falling edges of the output signals.

Output

Configuration

The MAX 9000 device architecture supports the MultiVolt I/O interface

feature, which allows MAX 9000 devices to interface with systems of

differing supply voltages. The 5.0-V devices in all packages can be set for

3.3-V or 5.0-V I/O pin operation. These devices have one set of VCC pins

for internal operation and input buffers (VCCINT), and another set for I/O

output drivers (VCCIO).

The VCCINT pins must always be connected to a 5.0-V power supply.

With a 5.0-V VCCINT level, input voltages are at TTL levels and are

therefore compatible with 3.3-V and 5.0-V inputs.

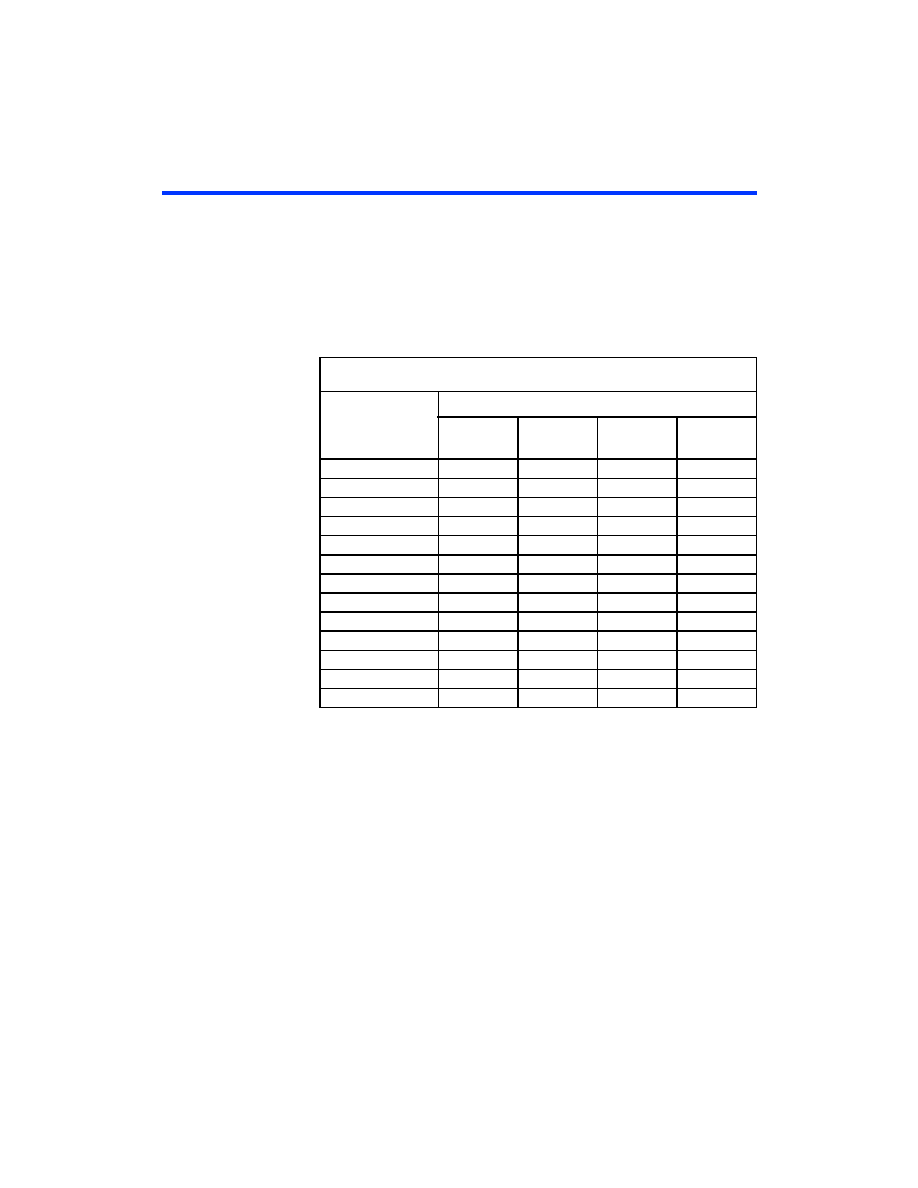

Table 6. Peripheral Bus Sources

Peripheral Control

Signal

Source

EPM9320

EPM9320A

EPM9400

EPM9480

EPM9560

EPM9560A

OE0/ENA0

Row C

Row E

Row F

Row G

OE1/ENA1

Row B

Row E

Row F

OE2/ENA2

Row ARow ERow ERow E

OE3/ENA3

Row BRow BRow BRow B

OE4/ENA4

Row ARow ARow ARow A

OE5

Row DRow DRow DRow D

OE6

Row CRow CRow CRow C

OE7/CLR1

Row B/GOE

CLR0/ENA5

Row A/GCLR

CLK0

GCLK1

CLK1

GCLK2

CLK2

Row DRow DRow DRow D

CLK3

Row CRow CRow CRow C

相关PDF资料 |

PDF描述 |

|---|---|

| EPM9560RC208-20 | |

| EPM9560RC240-15 | |

| EPM9560RC240-20 | |

| EPM9560RC304-15 | |

| EPM9560RI208-15 | |

相关代理商/技术参数 |

参数描述 |

|---|---|

| EPM9560RC208-20 | 制造商:Altera Corporation 功能描述:IC MAX |

| EPM9560RC240-15 | 功能描述:CPLD - 复杂可编程逻辑器件 CPLD - MAX 9000 560 Macro 191 IOs RoHS:否 制造商:Lattice 系列: 存储类型:EEPROM 大电池数量:128 最大工作频率:333 MHz 延迟时间:2.7 ns 可编程输入/输出端数量:64 工作电源电压:3.3 V 最大工作温度:+ 90 C 最小工作温度:0 C 封装 / 箱体:TQFP-100 |

| EPM9560RC240-15YY | 制造商:Altera Corporation 功能描述:CPLD MAX 9000 Family 12K Gates 560 Macro Cells 117.6MHz CMOS Technology 5V 240-Pin RQFP 制造商:Altera Corporation 功能描述:CPLD MAX 9000 Family 12K Gates 560 Macro Cells 117.6MHz 5V 240-Pin RQFP |

| EPM9560RC240-20 | 功能描述:CPLD - 复杂可编程逻辑器件 CPLD - MAX 9000 560 Macro 191 IOs RoHS:否 制造商:Lattice 系列: 存储类型:EEPROM 大电池数量:128 最大工作频率:333 MHz 延迟时间:2.7 ns 可编程输入/输出端数量:64 工作电源电压:3.3 V 最大工作温度:+ 90 C 最小工作温度:0 C 封装 / 箱体:TQFP-100 |

| EPM9560RC304-15 | 制造商:Altera Corporation 功能描述:IC MAX |

发布紧急采购,3分钟左右您将得到回复。