- 您现在的位置:买卖IC网 > PDF目录16568 > EVAL-AD2S1205SDZ (Analog Devices Inc)BOARD EVAL FOR AD2S1205 PDF资料下载

参数资料

| 型号: | EVAL-AD2S1205SDZ |

| 厂商: | Analog Devices Inc |

| 文件页数: | 3/20页 |

| 文件大小: | 0K |

| 描述: | BOARD EVAL FOR AD2S1205 |

| 标准包装: | 1 |

| 主要目的: | 接口,旋转变压至数字 |

| 嵌入式: | 否 |

| 已用 IC / 零件: | AD2S1205 |

| 主要属性: | 12 位分辨率,最大 1250 rps 或 1024 脉冲/反向 |

| 已供物品: | 板 |

AD2S1205

Rev. A | Page 11 of 20

ON-BOARD PROGRAMMABLE SINUSOIDAL

OSCILLATOR

An on-board oscillator provides the sinusoidal excitation signal

(EXC) and its complement signal (EXC) to the resolver. The fre-

quency of this reference signal is programmable to four standard

frequencies (10 kHz, 12 kHz, 15 kHz, or 20 kHz) by using the

FS1 and FS2 pins (see

). FS1 and FS2 have internal pull-ups,

so the default frequency is 10 kHz. The amplitude of this signal

is centered on 2.5 V and has an amplitude of 3.6 V p-p.

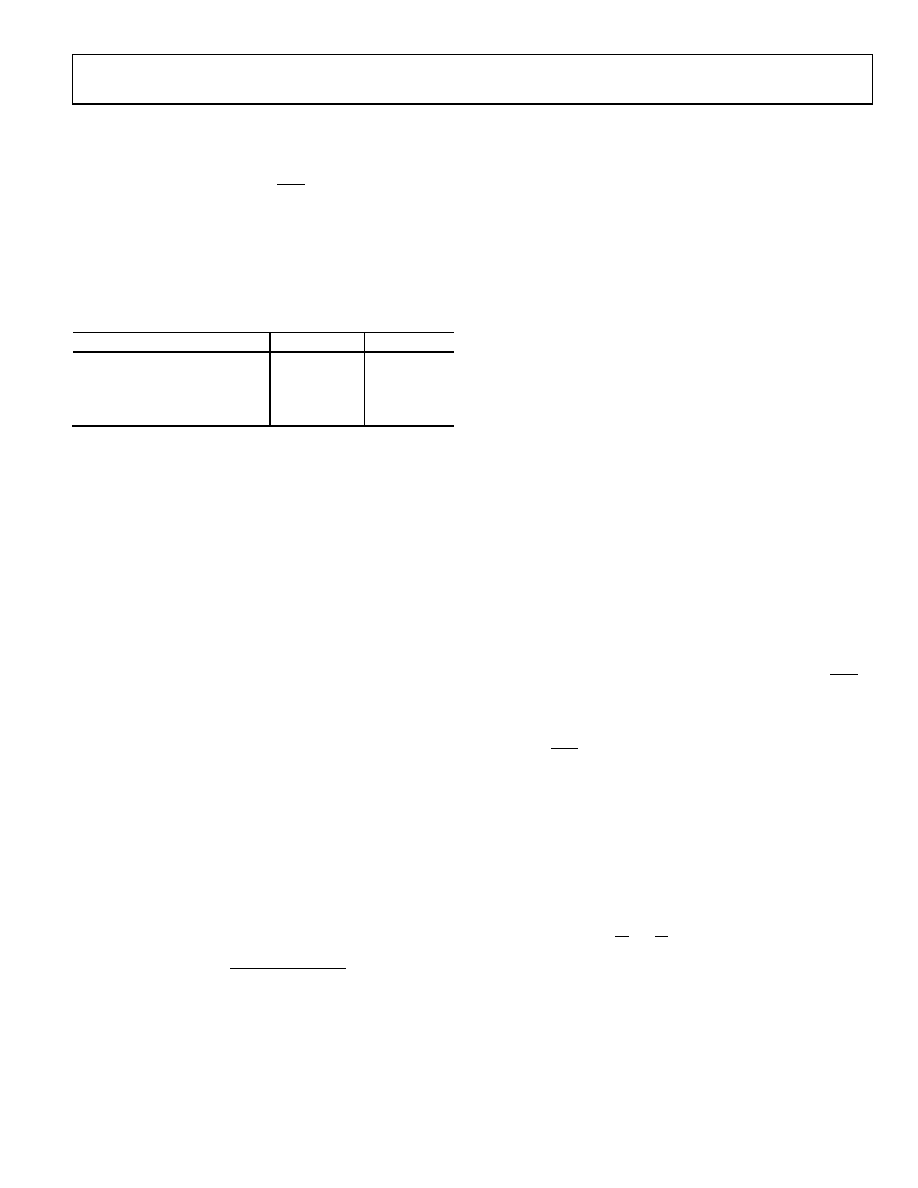

Table 5. Excitation Frequency Selection

Frequency Selection (kHz)

FS1

FS2

10

1

12

1

0

15

0

1

20

0

The frequency of the reference signal is a function of the CLKIN

frequency. By decreasing the CLKIN frequency, the minimum

excitation frequency can also be decreased. This allows an

excitation frequency of 7.5 kHz to be set when using a CLKIN

frequency of 6.144 MHz, and it also decreases the maximum

tracking rate to 750 rps.

The reference output of the AD2S1205 requires an external buffer

amplifier to provide gain and additional current to drive the

resolver. See Figure 6 for a suggested buffer circuit.

The AD2S1205 also provides an internal synchronous reference

signal that is phase locked to its Sin and Cos inputs. Phase errors

between the resolver’s primary and secondary windings may

degrade the accuracy of the RDC and are compensated for by using

this synchronous reference signal. This also compensates for the

phase shifts due to temperature and cabling, and it eliminates the

need for an external preset phase-compensation circuit.

SYNTHETIC REFERENCE GENERATION

When a resolver undergoes a high rotation rate, the RDC tends

to act as an electric motor and produces speed voltages in

addition to the ideal Sin and Cos outputs. These speed voltages are

in quadrature to the main signal waveform. Moreover, nonzero

resistance in the resolver windings causes a nonzero phase shift

between the reference input and the Sin and Cos outputs. The

combination of the speed voltages and the phase shift causes a

tracking error in the RDC that is approximated by

Frequency

Reference

Rate

Rotation

Shift

Phase

Error

×

=

(6)

To compensate for the described phase error between the resolver

reference excitation and the Sin/Cos signals, an internal synthetic

reference signal is generated in phase with the reference frequency

carrier. The synthetic reference is derived using the internally

filtered Sin and Cos signals. It is generated by determining the

zero crossing of either the Sin or Cos (whichever signal is

larger), which improves phase accuracy, and evaluating the phase

of the resolver reference excitation. The synthetic reference reduces

the phase shift between the reference and Sin/Cos inputs to less

than 10° and can operate for phase shifts of ±45°.

CHARGE-PUMP OUTPUT

A 204.8 kHz square wave output with a 50% duty cycle is available

at the CPO pin of the AD2S1205. This square wave output can

be used for negative rail voltage generation or to create a VCC rail.

CONNECTING THE CONVERTER

Ground is connected to the AGND and DGND pins (see Figure 5).

A positive power supply (VDD) of 5 V dc ± 5% is connected to

the AVDD and DVDD pins, with typical values for the decoupling

capacitors being 10 nF and 4.7 μF. These capacitors are then

placed as close to the device pins as possible and are connected

to both AVDD and DVDD. If desired, the reference oscillator

frequency can be changed from the nominal value of 10 kHz

using FS1 and FS2. Typical values for the oscillator decoupling

capacitors are 20 pF, whereas typical values for the reference

decoupling capacitors are 10 μF and 0.01 μF. As outlined in the

Loss of Signal Detection section 68 kΩ resistors between the Sin

and SinLO inputs and the Cos and CosLO inputs can be used to

ensure loss of signal detection when all four inputs from resolver

are disconnected.

In this recommended configuration, the converter introduces a

VREF/2 offset in the Sin and Cos signal outputs from the resolver.

The SinLO and CosLO signals can each be connected to a different

potential relative to ground if the Sin and Cos signals adhere to the

recommended specifications. Note that because the EXC and EXC

outputs are differential, there is an inherent gain of 2×.

shows a suggested buffer circuit. Capacitor C1 may be used in

parallel with Resistor R2 to filter out any noise that may exist on the

EXC and

EXC outputs. Care should be taken when selecting the

cutoff frequency of this filter to ensure that phase shifts of the

carrier caused by the filter do not exceed the phase lock range

of the AD2S1205.

The gain of the circuit is

))

1

/(

1

(

)

/

(

ω

C1

R2

R1

R2

n

CarrierGai

×

+

×

=

(7)

and

×

+

×

+

×

=

IN

REF

OUT

V

ω

C1

R2

R1

R2

R1

R2

V

))

1

/(

1

(

1

(8)

where:

ω

is the radian frequency of the applied signal.

VREF, a dc voltage, is set so that VOUT is always a positive value,

eliminating the need for a negative supply.

相关PDF资料 |

PDF描述 |

|---|---|

| EBM25DCCI-S189 | CONN EDGECARD 50POS R/A .156 SLD |

| RCC15DCMT-S288 | CONN EDGECARD 30POS .100 EXTEND |

| EMM06DTMT-S189 | CONN EDGECARD 12POS R/A .156 SLD |

| L-14C12NKV4T | CER INDUCTOR 12NH 0603 |

| GBC10DRAN-S734 | CONN EDGECARD 20POS .100 R/A SLD |

相关代理商/技术参数 |

参数描述 |

|---|---|

| EVAL-AD2S1210EDZ | 功能描述:BOARD EVAL AD2S1210 RoHS:是 类别:编程器,开发系统 >> 评估演示板和套件 系列:- 标准包装:1 系列:PSoC® 主要目的:电源管理,热管理 嵌入式:- 已用 IC / 零件:- 主要属性:- 次要属性:- 已供物品:板,CD,电源 |

| EVAL-AD4001FMCZ | 功能描述:EVAL BOARD FOR AD4001 制造商:analog devices inc. 系列:- 零件状态:在售 A/D 转换器数:1 位数:16 采样率(每秒):2M 数据接口:SPI,DSP 输入范围:±VREF 不同条件下的功率(典型值):20mW @ 2MSPS 使用的 IC/零件:AD4001 所含物品:板,电源 标准包装:1 |

| EVAL-AD421EB | 制造商:AD 制造商全称:Analog Devices 功能描述:Loop-Powered 4 mA to 20 mA DAC |

| EVAL-AD5025EBZ | 制造商:AD 制造商全称:Analog Devices 功能描述:Fully Accurate 12-/14-/16-Bit VOUT DAC SPI Interface 2.7 V to 5.5 V in a TSSOP |

| EVAL-AD5045EBZ | 制造商:AD 制造商全称:Analog Devices 功能描述:Fully Accurate 12-/14-/16-Bit VOUT DAC SPI Interface 2.7 V to 5.5 V in a TSSOP |

发布紧急采购,3分钟左右您将得到回复。