- 您现在的位置:买卖IC网 > PDF目录17031 > EVAL-AD7641CBZ (Analog Devices Inc)BOARD EVALUATION FOR AD7641 PDF资料下载

参数资料

| 型号: | EVAL-AD7641CBZ |

| 厂商: | Analog Devices Inc |

| 文件页数: | 28/28页 |

| 文件大小: | 0K |

| 描述: | BOARD EVALUATION FOR AD7641 |

| 产品培训模块: | ADC Applications ADC Architectures ADC DC/AC Performance |

| 标准包装: | 1 |

| 系列: | PulSAR® |

| ADC 的数量: | 1 |

| 位数: | 18 |

| 采样率(每秒): | 2M |

| 数据接口: | 串行 |

| 输入范围: | ±2.5 V |

| 在以下条件下的电源(标准): | 2MSPS 带内部基准时为 75mW |

| 工作温度: | -40°C ~ 85°C |

| 已用 IC / 零件: | AD7641 |

| 已供物品: | 板 |

| 相关产品: | AD7641BSTZRL-ND - IC ADC 18BIT 2MSPS SAR 48-LQFP AD7641BCPZRL-ND - IC ADC 18BIT 2MSPS SAR 48-LFCSP AD7641BSTZ-ND - IC ADC 18BIT 2MSPS SAR 48-LQFP AD7641BCPZ-ND - IC ADC 18BIT 2MSPS SAR 48-LFCSP |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页当前第28页

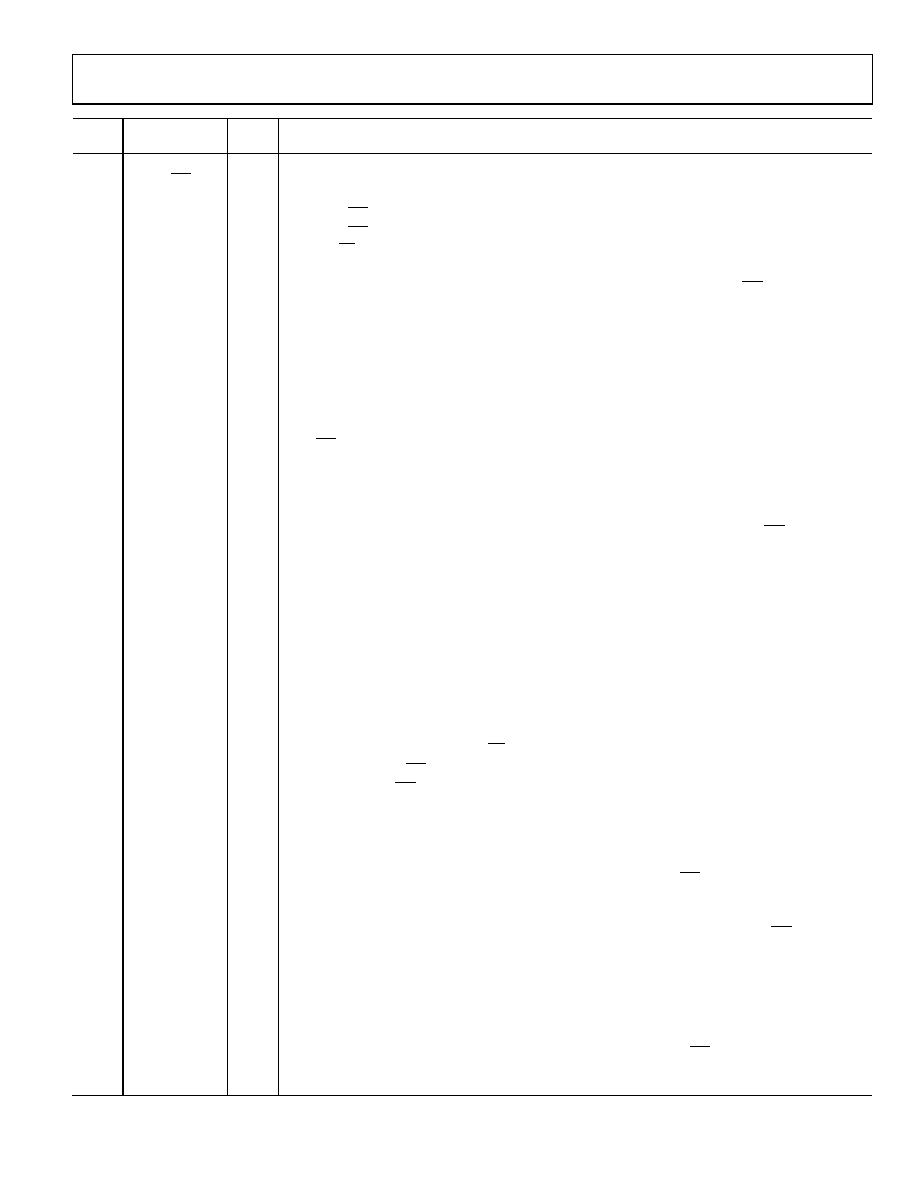

AD7641

Rev. 0 | Page 9 of 28

Pin

No.

Mnemonic

Type1

Description

13

D6

DI/O

When MODE[1:0] = 0, 1, or 2, this output is used as Bit 6 of the parallel port data output bus.

or EXT/INT

When MODE[1:0] = 3, (serial mode), serial clock source select. This input is used to select the

internally generated (master) or external (slave) serial data clock.

When EXT/INT = low, master mode. The internal serial clock is selected on SCLK output.

When EXT/INT = high, slave mode. The output data is synchronized to an external clock signal,

gated by CS, connected to the SCLK input.

14

D7

DI/O

When MODE[1:0] = 0, 1, or 2, this output is used as Bit 7 of the parallel port data output bus.

or INVSYNC

When MODE[1:0] = 3, (serial mode), invert sync select. In serial master mode (EXT/INT = low), this

input is used to select the active state of the SYNC signal.

When INVSYNC = low, SYNC is active high.

When INVSYNC = high, SYNC is active low.

15

D8

DI/O

When MODE[1:0] = 0, 1, or 2, this output is used as Bit 8 of the parallel port data output bus.

or INVSCLK

When MODE[1:0] = 3, (serial mode), invert SCLK select. In all serial modes, this input is used to

invert the SCLK signal.

16

D9

DI/O

When MODE[1:0] = 0, 1, or 2, this output is used as bit 9 of the parallel port data output bus.

or RDC

When MODE[1:0] = 3, (serial mode), read during convert. When using serial master mode

(EXT/INT = low), RDC is used to select the read mode.

When RDC = high, the previous conversion result is output on SDOUT during conversion and

the period of SCLK changes (see the Master Serial Interface section).

When RDC = low (read after convert), the current result can be output on SDOUT only when

the conversion is complete.

or SDIN

When MODE[1:0] = 3, (serial mode), serial data in. When using serial slave mode, (EXT/INT = high),

SDIN could be used as a data input to daisy-chain the conversion results from two or more ADCs

onto a single SDOUT line. The digital data level on SDIN is output on SDOUT with a delay of 18 SCLK

periods after the initiation of the read sequence.

17

OGND

P

Input/Output Interface Digital Power Ground.

18

OVDD

P

Input/Output Interface Digital Power. Nominally at the same supply as the supply of the

host interface (2.5 V or 3 V).

19

DVDD

P

Digital Power. Nominally at 2.5 V.

20

DGND

P

Digital Power Ground.

21

D10

DO

When MODE[1:0] = 0, 1, or 2, this output is used as Bit 10 of the parallel port data output bus.

or SDOUT

When MODE[1:0] = 3, (serial mode), serial data output. In serial mode, this pin is used as the serial

data output synchronized to SCLK. Conversion results are stored in an on-chip register. The AD7641

provides the conversion result, MSB first, from its internal shift register. The data format is

determined by the logic level of OB/2C.

In master mode, EXT/INT = low. SDOUT is valid on both edges of SCLK.

In slave mode, EXT/INT = high:

When INVSCLK = low, SDOUT is updated on SCLK rising edge and valid on the next falling edge.

When INVSCLK = high, SDOUT is updated on SCLK falling edge and valid on the next rising edge.

22

D11

DI/O

When MODE[1:0] = 0, 1, or 2, this output is used as Bit 11 of the parallel port data output bus.

or SCLK

When MODE[1:0] = 3, (serial mode), serial clock. In all serial modes, this pin is used as the serial

data clock input or output, depending upon the logic state of the EXT/INT pin. The active edge

where the data SDOUT is updated depends on the logic state of the INVSCLK pin.

23

D12

DO

When MODE[1:0] = 0, 1, or 2, this output is used as Bit 12 of the parallel port data output bus.

or SYNC

When MODE[1:0] = 3, (serial mode), frame synchronization. In serial master mode (EXT/INT= low),

this output is used as a digital output frame synchronization for use with the internal data clock.

When a read sequence is initiated and INVSYNC = low, SYNC is driven high and remains high

while SDOUT output is valid.

When a read sequence is initiated and INVSYNC = high, SYNC is driven low and remains low

while SDOUT output is valid.

24

D13

DO

When MODE[1:0] = 0, 1, or 2, this output is used as Bit 13 of the parallel port data output bus.

or RDERROR

When MODE[1:0] = 3, (serial mode), read error. In serial slave mode (EXT/INT = high), this output

is used as an incomplete read error flag. If a data read is started and not completed when the

current conversion is complete, the current data is lost and RDERROR is pulsed high.

相关PDF资料 |

PDF描述 |

|---|---|

| DC1571A-B | BOARD SAR ADC LTC2382-16 |

| DC1571A-A | BOARD SAR ADC LTC2383-16 |

| STD17W-5 | WIRE & CABLE MARKERS |

| STD17W-T | WIRE & CABLE MARKERS |

| EVAL-AD7612CBZ | BOARD EVALUATION FOR AD7612 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| EVAL-AD7641EDZ | 功能描述:BOARD EVAL FOR AD7641 RoHS:是 类别:编程器,开发系统 >> 评估板 - 模数转换器 (ADC) 系列:* 产品培训模块:Obsolescence Mitigation Program 标准包装:1 系列:- ADC 的数量:1 位数:12 采样率(每秒):94.4k 数据接口:USB 输入范围:±VREF/2 在以下条件下的电源(标准):- 工作温度:-40°C ~ 85°C 已用 IC / 零件:MAX11645 已供物品:板,软件 |

| EVAL-AD7643CB | 制造商:Analog Devices 功能描述:EVAL BD FOR AD7643 - Bulk |

| EVAL-AD7643CBZ | 功能描述:BOARD EVALUATION FOR AD7643 RoHS:是 类别:编程器,开发系统 >> 评估板 - 模数转换器 (ADC) 系列:PulSAR® 产品培训模块:Obsolescence Mitigation Program 标准包装:1 系列:- ADC 的数量:1 位数:12 采样率(每秒):94.4k 数据接口:USB 输入范围:±VREF/2 在以下条件下的电源(标准):- 工作温度:-40°C ~ 85°C 已用 IC / 零件:MAX11645 已供物品:板,软件 |

| EVAL-AD7643EDZ | 功能描述:BOARD EVAL FOR AD7643 RoHS:是 类别:编程器,开发系统 >> 评估板 - 模数转换器 (ADC) 系列:* 产品培训模块:Obsolescence Mitigation Program 标准包装:1 系列:- ADC 的数量:1 位数:12 采样率(每秒):94.4k 数据接口:USB 输入范围:±VREF/2 在以下条件下的电源(标准):- 工作温度:-40°C ~ 85°C 已用 IC / 零件:MAX11645 已供物品:板,软件 |

| EVAL-AD7650CB | 制造商:Analog Devices 功能描述:EVAL BD EVAL BD AD765X/AD766X/AD767X - Bulk |

发布紧急采购,3分钟左右您将得到回复。