- 您现在的位置:买卖IC网 > PDF目录17055 > EVAL-AD7946CBZ (Analog Devices Inc)BOARD EVALUATION FOR AD7946 PDF资料下载

参数资料

| 型号: | EVAL-AD7946CBZ |

| 厂商: | Analog Devices Inc |

| 文件页数: | 10/24页 |

| 文件大小: | 0K |

| 描述: | BOARD EVALUATION FOR AD7946 |

| 标准包装: | 1 |

| 系列: | PulSAR® |

| ADC 的数量: | 1 |

| 位数: | 14 |

| 采样率(每秒): | 500k |

| 数据接口: | 串行 |

| 输入范围: | 0 ~ 5.5 V |

| 在以下条件下的电源(标准): | 19mW @ 500kSPS,5 V |

| 工作温度: | -40°C ~ 85°C |

| 已用 IC / 零件: | AD7946 |

| 已供物品: | 板,CD |

| 相关产品: | AD7946BCPZRL7TR-ND - IC ADC 14BIT 500KSPS 10-LFCSP AD7946BCPZRL-ND - IC ADC 14BIT 500KSPS 10-LFCSP AD7946BRMZRL7-ND - IC ADC 14BIT 500KSPS 10-MSOP AD7946BRMZ-ND - IC ADC 14BIT 500KSPS SAR 10-MSOP |

AD7946

Rev. A | Page 18 of 24

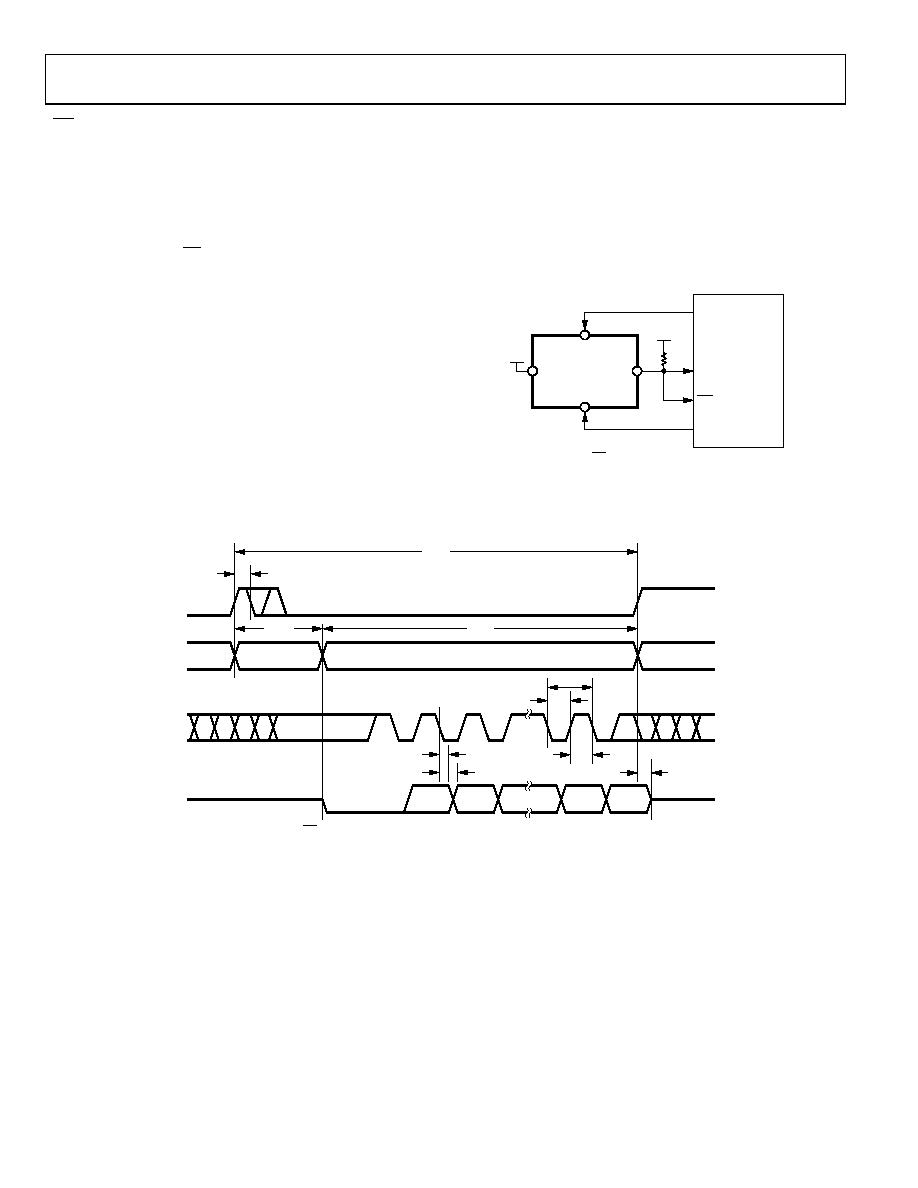

CS MODE 3-WIRE WITH BUSY INDICATOR

This mode is usually used when a single AD7946 is connected

to an SPI-compatible digital host having an interrupt input.

The connection diagram is shown in Figure 35, and the

corresponding timing is given in Figure 36.

With SDI tied to VIO, a rising edge on CNV initiates a

conversion, selects the CS mode, and forces SDO to high

impedance. SDO is maintained in high impedance until the

completion of the conversion irrespective of the state of CNV.

Prior to the minimum conversion time, CNV could be used to

select other SPI devices, such as analog multiplexers, but CNV

must be returned low before the minimum conversion time and

held low until the maximum conversion time to guarantee the

generation of the BUSY signal indicator. When the conversion

is complete, SDO goes from high impedance to low. With a

pull-up on the SDO line, this transition can be used as an

interrupt signal to initiate the data reading controlled by the

digital host. The AD7946 then enters the acquisition phase and

powers down. The data bits are then clocked out, MSB first, by

subsequent SCK falling edges. The data is valid on both SCK

edges. Although the rising edge can be used to capture the data,

a digital host using the SCK falling edge allows a faster reading

rate, provided it has an acceptable hold time. After the optional

15th SCK falling edge, or when CNV goes high, whichever is

earlier, SDO returns to high impedance.

If multiple AD7946s are selected at the same time, the SDO

output pin handles this contention without damage or induced

latch-up. Meanwhile, it is recommended to keep this contention

as short as possible to limit extra power dissipation.

DATA IN

IRQ

CLK

CONVERT

VIO

DIGITAL HOST

04

65

6-

0

34

47k

CNV

SCK

SDO

SDI

VIO

AD7946

Figure 35. CS Mode 3-Wire with BUSY Indicator

Connection Diagram (SDI High)

SDO

D13

D12

D1

D0

tDIS

SCK

12

3

13

14

15

tSCK

tSCKL

tSCKH

tHSDO

tDSDO

CNV

CONVERSION

ACQUISITION

tCONV

tCYC

tCNVH

tACQ

ACQUISITION

SDI = 1

04656-035

Figure 36. CS Mode 3-Wire with BUSY Indicator Serial Interface Timing (SDI High)

相关PDF资料 |

PDF描述 |

|---|---|

| MIC2015-0.8YML TR | IC DISTRIBUTION SW 0.8A 6-MLF |

| RBA10DTKT-S288 | CONN EDGECARD 20POS .125 EXTEND |

| HCC10DRYS | CONN EDGECARD 20POS DIP .100 SLD |

| HBC08DRAS | CONN EDGECARD 16POS R/A .100 SLD |

| GEC50DRXS | CONN EDGECARD 100PS DIP .100 SLD |

相关代理商/技术参数 |

参数描述 |

|---|---|

| EVAL-AD7946SDZ | 功能描述:BOARD EVAL FOR AD7946 RoHS:否 类别:编程器,开发系统 >> 评估板 - 模数转换器 (ADC) 系列:* 产品培训模块:Obsolescence Mitigation Program 标准包装:1 系列:- ADC 的数量:1 位数:12 采样率(每秒):94.4k 数据接口:USB 输入范围:±VREF/2 在以下条件下的电源(标准):- 工作温度:-40°C ~ 85°C 已用 IC / 零件:MAX11645 已供物品:板,软件 |

| EVAL-AD7949CBZ | 制造商:Analog Devices 功能描述:EVAL BOARD 8 CH 250KSPS 14BIT ADC IC. - Bulk |

| EVAL-AD7949EDZ | 功能描述:BOARD EVAL AD7949 RoHS:是 类别:编程器,开发系统 >> 评估板 - 模数转换器 (ADC) 系列:PulSAR® 产品培训模块:Obsolescence Mitigation Program 标准包装:1 系列:- ADC 的数量:1 位数:12 采样率(每秒):94.4k 数据接口:USB 输入范围:±VREF/2 在以下条件下的电源(标准):- 工作温度:-40°C ~ 85°C 已用 IC / 零件:MAX11645 已供物品:板,软件 |

| EVAL-AD7951EDZ | 功能描述:BOARD EVAL FOR AD7951 RoHS:是 类别:编程器,开发系统 >> 评估板 - 模数转换器 (ADC) 系列:* 产品培训模块:Obsolescence Mitigation Program 标准包装:1 系列:- ADC 的数量:1 位数:12 采样率(每秒):94.4k 数据接口:USB 输入范围:±VREF/2 在以下条件下的电源(标准):- 工作温度:-40°C ~ 85°C 已用 IC / 零件:MAX11645 已供物品:板,软件 |

| EVAL-AD7960FMCZ | 制造商:Analog Devices 功能描述:AD7960 18BIT PULSAR DIFF ADC 制造商:Analog Devices 功能描述:EVAL BOARD, AD7960 ADC, Silicon Manufacturer:Analog Devices, Silicon Core Number:AD7960, Kit Application Type:Data Converter, Application Sub Type:ADC, Kit Contents:Eval Board AD7960,, Features:(Not Applicable) |

发布紧急采购,3分钟左右您将得到回复。