- 您现在的位置:买卖IC网 > PDF目录16598 > EVAL-AD9838SDZ (Analog Devices Inc)BOARD EVAL FOR AD9838 PDF资料下载

参数资料

| 型号: | EVAL-AD9838SDZ |

| 厂商: | Analog Devices Inc |

| 文件页数: | 9/32页 |

| 文件大小: | 0K |

| 描述: | BOARD EVAL FOR AD9838 |

| 产品培训模块: | Direct Digital Synthesis Tutorial Series (1 of 7): Introduction Direct Digital Synthesizer Tutorial Series (7 of 7): DDS in Action Direct Digital Synthesis Tutorial Series (3 of 7): Angle to Amplitude Converter Direct Digital Synthesis Tutorial Series (6 of 7): SINC Envelope Correction Direct Digital Synthesis Tutorial Series (4 of 7): Digital-to-Analog Converter Direct Digital Synthesis Tutorial Series (2 of 7): The Accumulator |

| 标准包装: | 1 |

| 主要目的: | 计时,直接数字合成(DDS) |

| 嵌入式: | 否 |

| 已用 IC / 零件: | AD9838 |

| 主要属性: | USB 供电或外部电源 |

| 次要属性: | SPI 接口 |

| 已供物品: | 板,线缆,CD,文档 |

第1页第2页第3页第4页第5页第6页第7页第8页当前第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页

AD9838

Rev. A | Page 17 of 32

FUNCTIONAL DESCRIPTION

SERIAL INTERFACE

The AD9838 has a standard 3-wire serial interface that is

compatible with the SPI, QSPI, MICROWIRE, and DSP

interface standards.

Data is loaded into the device as a 16-bit word under the control

of a serial clock input, SCLK. The timing diagram for this oper-

ation is given in Figure 4.

FSYNC is a level triggered input that acts as a frame synchroni-

zation and chip enable input. Data can be transferred into the

device only when FSYNC is low. To start the serial data transfer,

FSYNC should be taken low, observing the minimum FSYNC

goes low, serial data is shifted into the input shift register of the

device on the falling edges of SCLK for 16 clock pulses. FSYNC

can be taken high after the 16th falling edge of SCLK, observing

the minimum SCLK falling edge to FSYNC rising edge time, t8.

Alternatively, FSYNC can be kept low for a multiple of 16 SCLK

pulses and then brought high at the end of the data transfer. In

this way, a continuous stream of 16-bit words can be loaded

while FSYNC is held low; FSYNC goes high only after the 16th

SCLK falling edge of the last word loaded.

The SCLK can be continuous, or it can idle high or low between

write operations. In either case, it must be high when FSYNC

goes low (t12).

For an example of how to program the AD9838, see the AN-1070

Application Note on the Analog Devices, Inc., website. The

LATENCY PERIOD

A latency period is associated with each operation. When the

FSELECT and PSELECT pins change value, there is a pipeline

delay before control is transferred to the selected register.

FSELECT and PSELECT have latencies of eight MCLK cycles.

When the t11 and t11A timing specifications are not met, the latency

is increased by one MCLK cycle.

Similarly, a latency period is associated with each asynchronous

write operation. If a selected frequency or phase register is

loaded with a new word, there is a delay of eight or nine MCLK

cycles before the analog output changes. The delay can be eight

or nine MCLK cycles, depending on the position of the MCLK

rising edge when the data is loaded into the destination register.

The negative transitions of the RESET and SLEEP pins are

sampled on the internal falling edge of MCLK. Therefore, they

also have a latency period associated with them.

CONTROL REGISTER

The AD9838 contains a 16-bit control register that allows the

user to configure the operation of the AD9838. All control bits

other than the MODE bit are sampled on the internal falling

edge of MCLK.

describes the individual bits of the control register. The different

functions and the various output options of the AD9838 are

described in more detail in the following sections.

To inform the AD9838 that the contents of the control register

will be altered, Bit D15 and Bit D14 must be set to 0, as shown

in Table 6.

Table 6. Control Register Bits

D15

D14

D13 to D0

0

Control bits

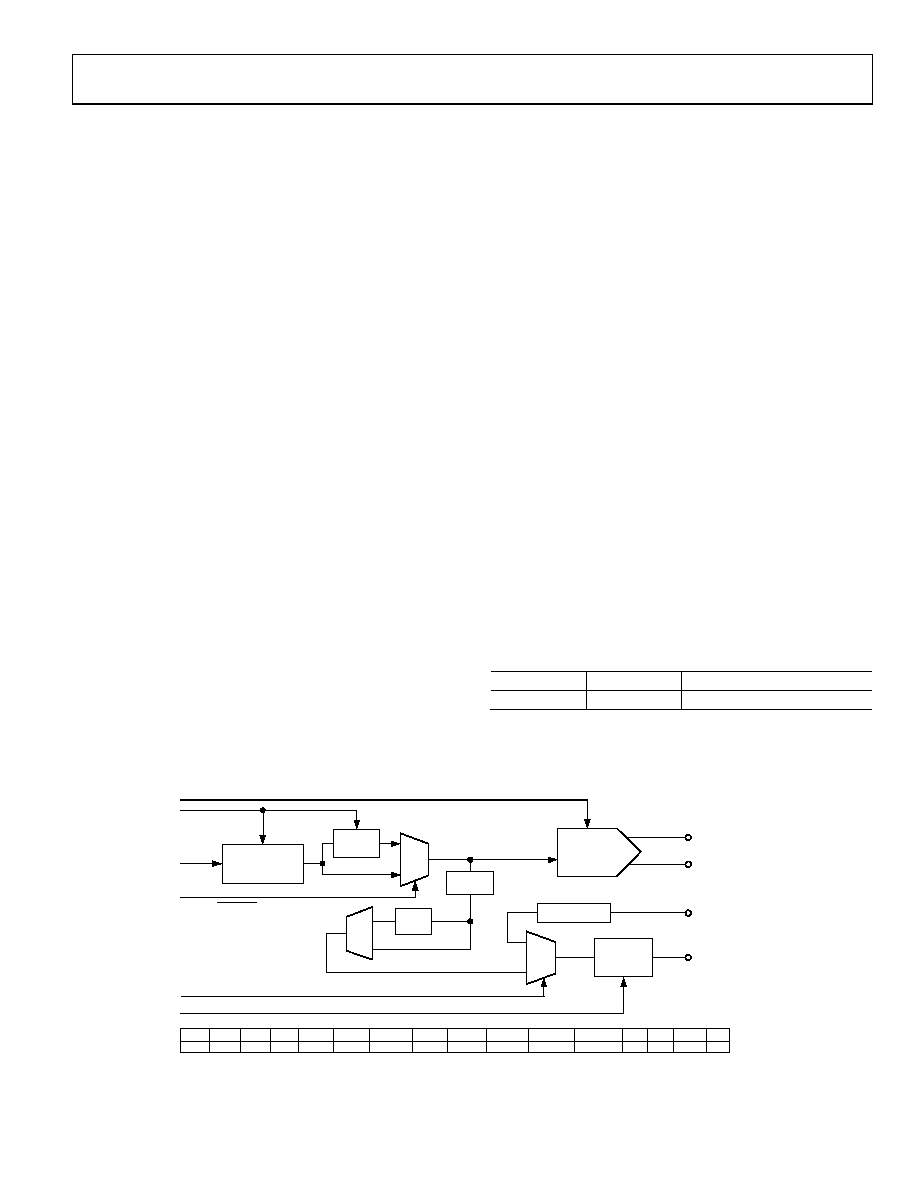

MUX

SLEEP12

SLEEP1

RESET

OPBITEN

IOUTB

IOUT

COMPARATOR

VIN

SIGN/PIB

MUX

MSB

SIGN BIT OUT

0

1

MUX

1

0

1

DIGITAL

OUTPUT

(ENABLE)

(LOW POWER)

10-BIT DAC

DIVIDE

BY 2

SIN

ROM

MODE + OPBITEN

PHASE

ACCUMULATOR

(28-BIT)

09

07

7-

0

26

D15

0

D14

0

D13

B28

D12

HLB

D11

FSEL

D10

PSEL

D9

PIN/SW

D8

RESET

D7

SLEEP1

D6

SLEEP12

D5

OPBITEN

D4

SIGN/PIB

D3

DIV2

D2

0

D1

MODE

D0

0

Figure 22. Function of Control Bits

相关PDF资料 |

PDF描述 |

|---|---|

| A3AAH-2036M | IDC CABLE - ASC20H/AE20M/ASC20H |

| M1CXA-3436R | IDC CABLE - MKC34A/MC34M/X |

| M1AXA-3436R | IDC CABLE - MSC34A/MC34M/X |

| B82477R4472M100 | INDUCTOR POWER 4.7UH 7.5A SMD |

| 860529-8 | CONN LEAD ASSY DBL-END 20AWG 10" |

相关代理商/技术参数 |

参数描述 |

|---|---|

| EVAL-AD9880-ABZ | 功能描述:KIT MODULE VIDEO INPUT AD9880 RoHS:是 类别:编程器,开发系统 >> 评估演示板和套件 系列:- 标准包装:1 系列:PCI Express® (PCIe) 主要目的:接口,收发器,PCI Express 嵌入式:- 已用 IC / 零件:DS80PCI800 主要属性:- 次要属性:- 已供物品:板 |

| EVAL-ADAS1000EBZU1 | 功能描述:EVAL BOARD ADAS1000 ECG AFE RoHS:是 类别:编程器,开发系统 >> 评估演示板和套件 系列:* 产品培训模块:Obsolescence Mitigation Program 标准包装:1 系列:- 主要目的:电源管理,电池充电器 嵌入式:否 已用 IC / 零件:MAX8903A 主要属性:1 芯锂离子电池 次要属性:状态 LED 已供物品:板 |

| EVAL-ADAS1000SDZ | 功能描述:数据转换 IC 开发工具 EVALUATION BOARD RoHS:否 制造商:Texas Instruments 产品:Demonstration Kits 类型:ADC 工具用于评估:ADS130E08 接口类型:SPI 工作电源电压:- 6 V to + 6 V |

| EVAL-ADAS1000SDZU3 | 制造商:Analog Devices 功能描述:EVALUATION KIT - Boxed Product (Development Kits) |

| EVAL-ADAS1000SDZU4 | 制造商:Analog Devices 功能描述:EVAL BOARD ANAS1000 ECG AFE |

发布紧急采购,3分钟左右您将得到回复。