参数资料

| 型号: | EVAL-CED1Z |

| 厂商: | Analog Devices Inc |

| 文件页数: | 5/24页 |

| 文件大小: | 0K |

| 描述: | BOARD EVAL CONVERTER |

| 标准包装: | 1 |

| 附件类型: | 接口板 |

| 适用于相关产品: | ADI 高速 ADC 评估板 |

| 其它名称: | Q3407966B Q4537177 Q5381772 |

�� �

�

�

�Preliminary� Technical� Data�

�J1� –� MINI� USB� ‘B’� CONNECTOR�

�This� is� used� to� connect� the� CED1� to� the� PC� for� control� and� data�

�transfer�

�J2� –� 2-PIN� SCREW� TERMINAL� POWER� CONNECTOR�

�This� connector� is� used� when� powering� the� CED� board� with� a�

�lab� supply.� Care� must� be� taken� to� ensure� the� external� supply� is�

�connected� with� the� correct� polarity.�

�J4� –� DC� POWER� CONNECTOR�

�When� using� the� CED1� with� the� supplied� power� supply,� the� DC�

�plug� should� be� connected� here.� The� polarity� for� this� connector�

�is� centre� positive.�

�J6� –� FPGA� JTAG� CONNECTOR�

�This� can� be� used� with� Altera� SignalTap� Logic� Analyzer� and�

�appropriate� hardware� to� assist� with� FPGA� development� and�

�debug.�

�J8,� 9,� 10� –� 3×� 90-WAY� BLACKFIN� EZ-KIT�

�CONNECTORS�

�These� three� connectors� bring� across� most� of� the� peripheral�

�signals� from� the� Blackfin� Ez-Kit� directly� into� the� FPGA� where�

�Table� 2.� 96-way� connector� pin-out�

�EVAL-CED1Z�

�they� can� be� used� directly� or� rerouted� to� the� other� connectors.�

�Additional� processor� or� microcontroller� boards� could� be�

�designed� and� connected� here� if� the� user� wished� to� add� a�

�processor� to� the� design.� See� the� Blackfin� Ez-Kit� manual� for�

�details� of� these� connectors.�

�J3� –� 96-WAY� DIN41612� CONNECTOR�

�This� connector� has� traditionally� appeared� on� most� precision�

�ADC� evaluation� boards.� It� contains� SPI,� SPORT� and� Parallel�

�signals� as� well� as� programmable� digital� and� 5� separate� analog�

�power� supplies.� Pin� out� for� this� connector� is� shown� in� Table� 2.�

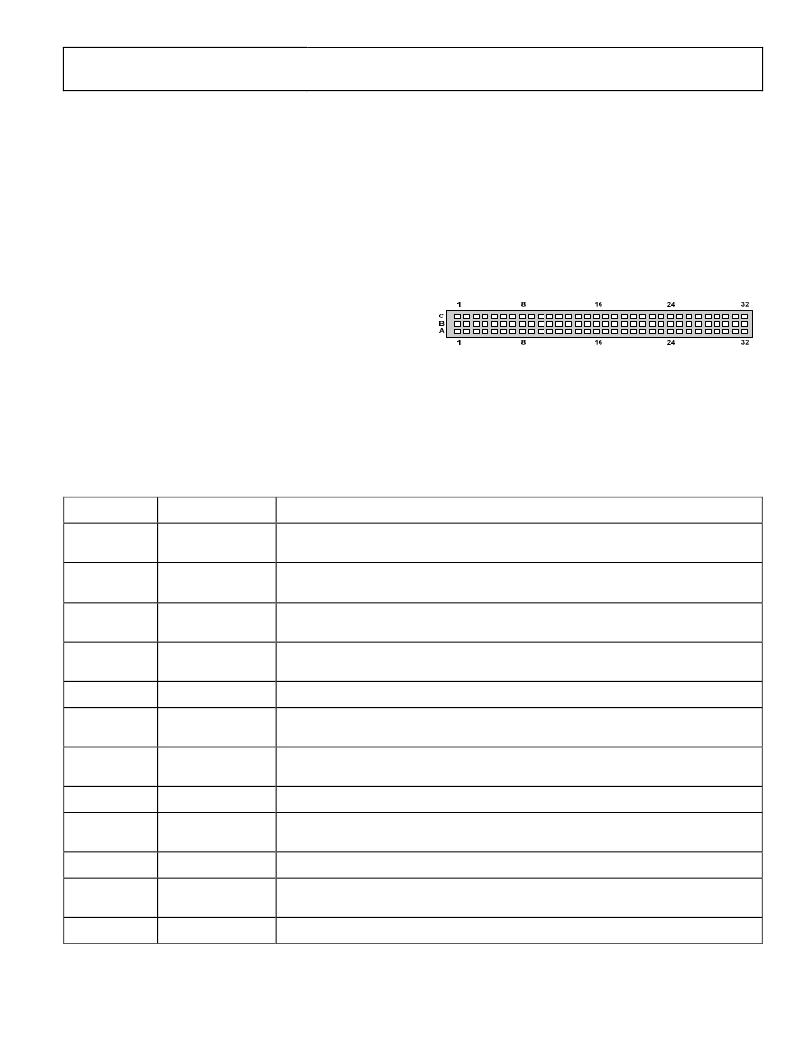

�Figure� 4.� 96-way� connector� pin� locations�

�Pin� Num�

�A1�

�B1�

�C1�

�A2�

�B2�

�C2�

�A3�

�B3�

�C3�

�A4,� B4,� C4�

�A5�

�B5�

�Pin� Name�

�SPORT_DT1PRI/�

�SPI_MOSI/PAR_D16�

�GPIO3/TMR1/�

�PPI_FS1�

�SPORT_DR1PRI/�

�SPI_MISO/PAR_D19�

�SPORT_TFS1/�

�SPI_SEL0/PAR_D17�

�PAR_D0�

�SPORT_RFS1/�

�SPI_SEL1/PAR_D20�

�SPORT_TSCLK1/�

�SPI_CLK/PAR_D18�

�PAR_D1�

�SPORT_RSCLK1/�

�SPI_CLK/PAR_D21�

�DGND�

�SPORT_DT0PRI/�

�SPI_SEL7�

�PAR_D2�

�Description�

�Sport1� Data� Transmit� Primary.� SPI� Master� Out,� Slave� In� data� line.� Parallel� Data� bit� 16.�

�General� Purpose� I/O� bit� 3.� Timer� 1.� Parallel� Peripheral� Interface� Frame� Sync� 1.�

�Sport� 1� Data� Receive� Primary.� SPI� Master� In,� Slave� Out� data� line.� Parallel� Data� bit� 19.�

�Sport� 1� Transmit� Frame� Sync.� SPI� Peripheral� Chip� Select� 0.� Parallel� Data� bit� 17.�

�Parallel� Data� bit� 0� (LSb)�

�Sport� 1� Receive� Frame� Sync.� SPI� Peripheral� Chip� Select� 1.� Parallel� Data� bit� 20.�

�Sport� 1� Transmit� Serial� Clock.� SPI� Clock.� Parallel� Data� bit� 18.�

�Parallel� Data� bit� 1.�

�Sport� 1� Receive� Clock.� SPI� Clock.� Parallel� Data� bit� 21.�

�Digital� Ground�

�Sport� 0� Data� Transmit� Primary.� SPI� Peripheral� Chip� Select� 7�

�Parallel� Data� bit� 2�

�Rev.� PrA� |� Page� 5� of� 24�

�相关PDF资料 |

PDF描述 |

|---|---|

| EVAL-CN0218-SDPZ | BOARD CFTL AD8212 |

| EVAL-CN0229-SDPZ | EVAL-CN0229-SDPZ |

| EVAL-CN0235-SDPZ | BOARD EVAL LITHIUM ION MONITOR |

| EVAL-CN0253-SDPZ | EVAL MONITOR CIRCUIT FRONT END |

| EVAL-CN0271-SDPZ | EVAL SYSTEM FOR CN0271 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| EVAL-CED1Z | 制造商:Analog Devices 功能描述:EVALUATION BOARD ((NS)) |

| EVAL-CED1Z3 | 制造商:AD 制造商全称:Analog Devices 功能描述:18-Bit, 2.5 LSB INL, 800 kSPS SAR ADC |

| EVAL-CFTL-6V-PWRZ | 功能描述:EVAL DC POWER SUPPLY RoHS:是 类别:编程器,开发系统 >> 评估板 - DC/DC 与 AC/DC(离线)SMPS 系列:- 标准包装:1 系列:- 主要目的:DC/DC,步降 输出及类型:1,非隔离 功率 - 输出:- 输出电压:3.3V 电流 - 输出:3A 输入电压:4.5 V ~ 28 V 稳压器拓扑结构:降压 频率 - 开关:250kHz 板类型:完全填充 已供物品:板 已用 IC / 零件:L7981 其它名称:497-12113STEVAL-ISA094V1-ND |

| EVAL-CFTL-LVDT | 功能描述:界面开发工具 RoHS:否 制造商:Bourns 产品:Evaluation Boards 类型:RS-485 工具用于评估:ADM3485E 接口类型:RS-485 工作电源电压:3.3 V |

| EVAL-CN0150A-SDPZ | 功能描述:EVAL CIRCUIT BOARD RoHS:是 类别:RF/IF 和 RFID >> RF 评估和开发套件,板 系列:- 标准包装:1 系列:- 类型:GPS 接收器 频率:1575MHz 适用于相关产品:- 已供物品:模块 其它名称:SER3796 |

发布紧急采购,3分钟左右您将得到回复。