- 您现在的位置:买卖IC网 > Datasheet目录412 > EZLC-4421 LB (Silicon Laboratories Inc)KIT EZLINK F930/SI4421 LOW BAND Datasheet资料下载

参数资料

| 型号: | EZLC-4421 LB |

| 厂商: | Silicon Laboratories Inc |

| 文件页数: | 34/45页 |

| 文件大小: | 0K |

| 描述: | KIT EZLINK F930/SI4421 LOW BAND |

| 标准包装: | 1 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页当前第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页

�� �

�

Si4421�

�RESET� MODES�

�The� chip� will� enter� into� reset� mode� if� any� of� the� following� conditions� are� met:�

�?� Power-on� reset:� During� a� power� up� sequence� until� the� V� dd� has� reached� the� correct� level� and� stabilized�

�?� Power� glitch� reset:� Transients� present� on� the� V� dd� line�

�?� Software� reset:� Special� control� command� received� by� the� chip�

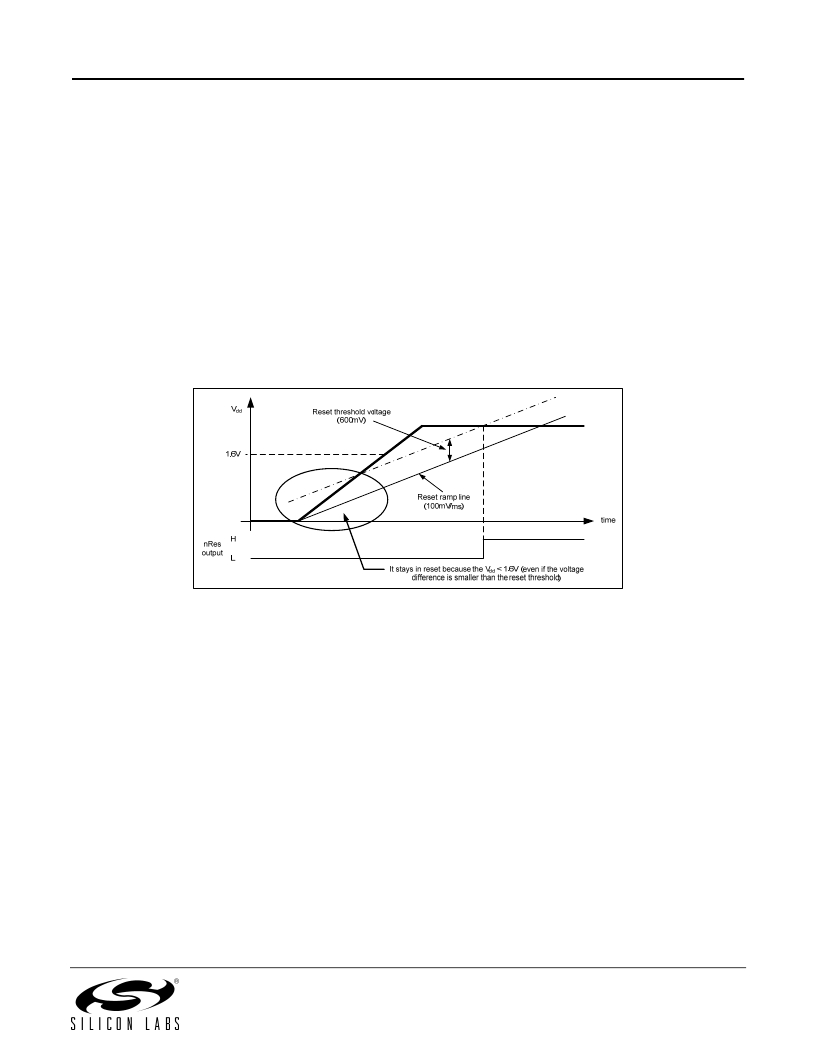

�Power-on� reset�

�After� power� up� the� supply� voltage� starts� to� rise� from� 0V.� The� reset� block� has� an� internal� ramping� voltage� reference� (reset-ramp�

�signal),� which� is� rising� at� 100mV/ms� (typical)� rate.� The� chip� remains� in� reset� state� while� the� voltage� difference� between� the� actual�

�V� dd� and� the� internal� reset-ramp� signal� is� higher� than� the� reset� threshold� voltage,� which� is� 600� mV� (typical).� As� long� as� the� V� dd� voltage�

�is� less� than� 1.6V� (typical)� the� chip� stays� in� reset� mode� regardless� the� voltage� difference� between� the� V� dd� and� the� internal� ramp�

�signal.�

�The� reset� event� can� last� up� to� 100ms� supposing� that� the� V� dd� reaches� 90%� its� final� value� within� 1ms.� During� this� period,� the� chip�

�does� not� accept� control� commands� via� the� serial� control� interface.�

�Power-on� reset� example:�

�Power� glitch� reset�

�The� internal� reset� block� has� two� basic� mode� of� operation:� normal� and� sensitive� reset.� The� default� mode� is� sensitive,� which� can� be�

�changed� by� the� appropriate� control� command� (see� Related� control� commands� at� the� end� of� this� section).� In� normal� mode� the� power�

�glitch� detection� circuit� is� disabled.�

�There� can� be� spikes� or� glitches� on� the� V� dd� line� if� the� supply� filtering� is� not� satisfactory� or� the� internal� resistance� of� the� power� supply�

�is� too� high.� In� such� cases� if� the� sensitive� reset� is� enabled� an� (unwanted)� reset� will� be� generated� if� the� positive� going� edge� of� the� V� dd�

�has� a� rising� rate� greater� than� 100mV/ms� and� the� voltage� difference� between� the� internal� ramp� signal� and� the� V� dd� reaches� the� reset�

�threshold� voltage� (600� mV).� Typical� case� when� the� battery� is� weak� and� due� to� its� increased� internal� resistance� a� sudden� decrease� of�

�the� current� consumption� (for� example� turning� off� the� power� amplifier)� might� lead� to� an� increase� in� supply� voltage.� If� for� some� reason�

�the� sensitive� reset� cannot� be� disabled� step-by-step� decrease� of� the� current� consumption� (by� turning� off� the� different� stages� one� by�

�one)� can� help� to� avoid� this� problem.�

�Any� negative� change� in� the� supply� voltage� will� not� cause� reset� event� unless� the� V� dd� level� reaches� the� reset� threshold� voltage� (250mV�

�in� normal� mode,� 1.6V� in� sensitive� reset� mode).�

�If� the� sensitive� mode� is� disabled� and� the� power� supply� turned� off� the� V� dd� must� drop� below� 250mV� in� order� to� trigger� a� power-on� reset�

�event� when� the� supply� voltage� is� turned� back� on.� If� the� decoupling� capacitors� keep� their� charges� for� a� long� time� it� could� happen� that�

�no� reset� will� be� generated� upon� power-up� because� the� power� glitch� detector� circuit� is� disabled.�

�Note� that� the� reset� event� reinitializes� the� internal� registers,� so� the� sensitive� mode� will� be� enabled� again.�

�34�

�相关PDF资料 |

PDF描述 |

|---|---|

| F2M03G-KIT-1 | KIT EVAL G MOD SNGL (NO OEM BRD) |

| F2M03M-KIT-1 | KIT EVAL M MOD SNGL (NO OEM BRD) |

| FA10323_K2S-W | LENS FOR LUXEON K2 |

| FA10539_SSS-W | LENS FOR SEOUL P4 |

| FA10643_TINA-M | LENS FOR GOLDEN/PLATINUM DRAGON |

相关代理商/技术参数 |

参数描述 |

|---|---|

| EZLC4431B1-D434 | 功能描述:射频开发工具 EZLink Kit F930 Si4431 Rev B1 434MHz RoHS:否 制造商:Taiyo Yuden 产品:Wireless Modules 类型:Wireless Audio 工具用于评估:WYSAAVDX7 频率: 工作电源电压:3.4 V to 5.5 V |

| EZLC4431B1-D868 | 功能描述:射频开发工具 EZLink Kit F930 Si4431 Rev B1 868MHz RoHS:否 制造商:Taiyo Yuden 产品:Wireless Modules 类型:Wireless Audio 工具用于评估:WYSAAVDX7 频率: 工作电源电压:3.4 V to 5.5 V |

| EZLC-4432 HB | 功能描述:射频开发工具 EZLink Fast Prototype Kit Hiband RoHS:否 制造商:Taiyo Yuden 产品:Wireless Modules 类型:Wireless Audio 工具用于评估:WYSAAVDX7 频率: 工作电源电压:3.4 V to 5.5 V |

| EZLC-4432 HB/LB KIT | 制造商:Silicon Laboratories Inc 功能描述: |

| EZLC-4432 LB | 功能描述:射频开发工具 EZLink Fast Prototype Kit Lwband RoHS:否 制造商:Taiyo Yuden 产品:Wireless Modules 类型:Wireless Audio 工具用于评估:WYSAAVDX7 频率: 工作电源电压:3.4 V to 5.5 V |

发布紧急采购,3分钟左右您将得到回复。