- 您现在的位置:买卖IC网 > PDF目录385376 > HFA3861BIN (INTERSIL CORP) Direct Sequence Spread Spectrum Baseband Processor PDF资料下载

参数资料

| 型号: | HFA3861BIN |

| 厂商: | INTERSIL CORP |

| 元件分类: | 无绳电话/电话 |

| 英文描述: | Direct Sequence Spread Spectrum Baseband Processor |

| 中文描述: | TELECOM, CELLULAR, BASEBAND CIRCUIT, PQFP64 |

| 封装: | 10 X 10 MM, PLASTIC, MS-026ACD, TQFP-64 |

| 文件页数: | 16/36页 |

| 文件大小: | 733K |

| 代理商: | HFA3861BIN |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页当前第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页

16

detected output is then processed through the differential

decoder to demodulate the last two bits of the symbol.

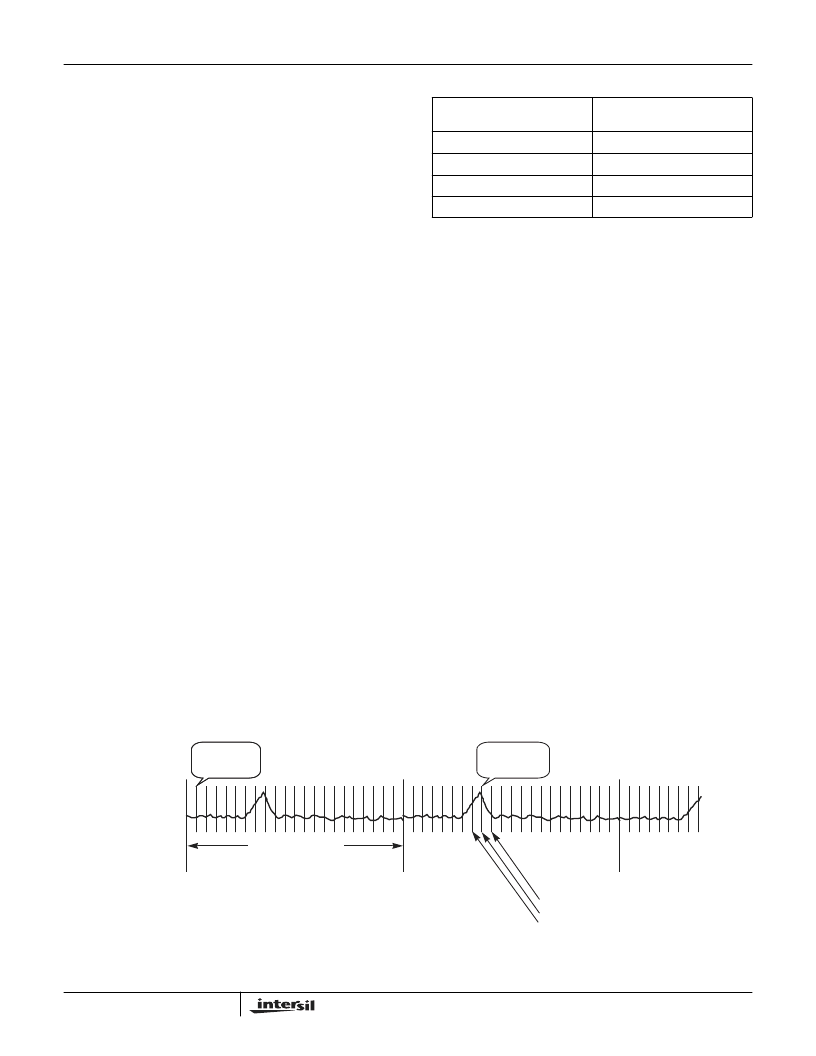

Data Demodulation and Tracking

Description (DBPSK and DQPSK Modes)

The signal is demodulated from the correlation peaks

tracked by the symbol timing loop (bit sync) as shown in

Figure 12. The frequency and phase of the signal is

corrected using the NCO that is driven by the phase locked

loop. Demodulation of the DBPSK data in the early stages of

acquisition is done by differential detection. Once phase

locked loop tracking of the carrier is established, coherent

demodulation is enabled for better performance. Averaging

the phase errors over 10 symbols gives the necessary

frequency information for proper NCO operation.

Configuration Register 10 sets the search timer for the SFD.

This register sets this time-out length in symbols for the

receiver. If the time out is reached, and no SFD is found, the

receiver resets to the acquisition mode. The suggested value is

the number of preamble symbols plus 16. If different transmit

preamble lengths are used by various transmitters in a network,

the longest value should be used for the receiver settings.

Data Decoder and Descrambler

Description

The data decoder that implements the desired DQPSK

coding/decoding as shown in Table 8. The data is formed

into pairs of bits called dibits. The left bit of the pair is the first

in time. This coding scheme results from differential coding

of the dibits. Vector rotation is counterclockwise for a positive

phase shift, but can be reversed with bit 7 or 6 of CR 1.

For DBPSK, the decoding is simple differential decoding.

The data scrambler and de-scrambler are self synchronizing

circuits. They consist of a 7-bit shift register with feedback of

some of the taps of the register. The scrambler is designed to

insure smearing of the discrete spectrum lines produced by the

PN code. One thing to keep in mind is that both the differential

decoding and the descrambling cause error extension or burst

errors. This is due to two properties of the processing. First, the

differential decoding process causes errors to occur on pairs of

symbols. When a symbol’s phase is in error, the next symbol

will also be decoded wrong since the data is encoded in the

change in phase from one symbol to the next. Thus, two errors

are made on two successive symbols. Therefore up to 4 bits

may be wrong although on the average only 2 are. In QPSK

mode, these may occur next to one another or separated by up

to 2 bits. In the CCK mode, when a symbol decision error is

made, up to 6 bits may be in error although on average only 3

bits will be in error. Secondly, when the bits are processed by

the descrambler, these errors are further extended. The

descrambler is a 7-bit shift register with two taps exclusive or’ed

with the bit stream. Thus, each error is extended by a factor of

three. Multiple errors can be spaced the same as the tap

spacing, so they can be canceled in the descrambler. In this

case, two wrongs do make a right. Given all that, if a single

error is made the whole packet is discarded anyway, so the

error extension property has no effect on the packet error rate.

Descrambling is self synchronizing and is done by a

polynomial division using a prescribed polynomial. A shift

register holds the last quotient and the output is the exclusive-

or of the data and the sum of taps in the shift register.

TABLE 8. DQPSK DATA DECODER

PHASE SHIFT

DIBIT PATTERN (D0, D1)

D0 IS FIRST IN TIME

0

00

+90

01

+180

11

-90

10

T0 + 1

SYMBOL

CORRELATOR

OUTPUT

REPEATS

CORRELATION

PEAK

T0 + 2

SYMBOLS

T0

CORRELATOR OUTPUT IS

THE RESULT OF CORRELATING

THE PN SEQUENCE WITH THE

RECEIVED SIGNAL

SAMPLES

AT 2X CHIP

RATE

EARLY

ON-TIME

LATE

CORRELATION TIME

FIGURE 12. CORRELATION PROCESS

HFA3861B

相关PDF资料 |

PDF描述 |

|---|---|

| HFA3861BIN96 | Direct Sequence Spread Spectrum Baseband Processor |

| HFA3925IA | null2.4GHz - 2.5GHz 250mW Power Amplifier |

| HFA3925IA96 | null2.4GHz - 2.5GHz 250mW Power Amplifier |

| HFA50PA60C | RxxP2xx Series - Econoline Unregulated DC-DC Converters; Input Voltage (Vdc): 05V; Output Voltage (Vdc): 15V; Power: 2W; EN 60950 certified, rated for 250VAC; UL-60950-1 / CSA C22.2 certified; 5.2kVDC Isolation for 1 Minute; Optional Continuous Short Circuit Protected; Wide Operating Temperature Range atfull 2 Watts Load, ?40??C to +85??C; Twin Chamber Transformer System; UL94V-0 Package Material; Efficiency to 80% |

| HFB50PA60C | Ultrafast, Soft Recovery Diode |

相关代理商/技术参数 |

参数描述 |

|---|---|

| HFA3861BIN96 | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:Direct Sequence Spread Spectrum Baseband Processor |

| HFA3861IV | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:Direct Sequence Spread Spectrum Baseband Processor |

| HFA3861IV96 | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:Direct Sequence Spread Spectrum Baseband Processor |

| HFA3863 | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:Direct Sequence Spread Spectrum Baseband Processor |

| HFA3863IN | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:Direct Sequence Spread Spectrum Baseband Processor |

发布紧急采购,3分钟左右您将得到回复。