- 您现在的位置:买卖IC网 > PDF目录371807 > HFA3863 (Intersil Corporation) Direct Sequence Spread Spectrum Baseband Processor(直接序列扩谱基带处理器) PDF资料下载

参数资料

| 型号: | HFA3863 |

| 厂商: | Intersil Corporation |

| 元件分类: | 基带处理器 |

| 英文描述: | Direct Sequence Spread Spectrum Baseband Processor(直接序列扩谱基带处理器) |

| 中文描述: | 直接序列扩频基带处理器(直接序列扩谱基带处理器) |

| 文件页数: | 12/39页 |

| 文件大小: | 305K |

| 代理商: | HFA3863 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页当前第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页

4-12

to all code chips,

2 is added to all odd code chips,

3 is

added to all odd pairs of code chips and

4 is added to all

odd quads of code chips.

The phase

1 modifies the phase of all code chips of the

sequence and is DQPSK encoded for 5.5 and 11Mbps. This

will take the form of rotating the whole symbol by the

appropriate amount relative to the phase of the preceding

symbol. Note that the last chip of the symbol defined above

is the chip that indicates the symbol’s reference phase.

For the 5.5Mbps CCK mode, the output of the scrambler is

partitioned into nibbles. The first two bits are encoded as

differential symbol phase modulation in accordance with

Table 5. All odd numbered symbols of the MPDU are given

an extra 180 degree (

π

) rotation in addition to the standard

DQPSK modulation as shown in the table. The symbols of

the MPDU shall be numbered starting with “0” for the first

symbol for the purposes of determining odd and even

symbols. That is, the MPDU starts on an even numbered

symbol. The last data dibits d2, and d3 CCK encode the

basic symbol as specified in Table 6. This table is derived

from the CCK formula above by setting

2 = (d2*pi)+ pi/2,

3

= 0, and

4 = d3*pi. In the table d2 and d3 are in the order

shown and the complex chips are shown LSB to MSB (left to

right) with LSB transmitted first.

At 11Mbps, 8 bits (d0 to d7; d0 first in time) are transmitted

per symbol.

The first dibit (d0, d1) encodes the phase

1 based on

DQPSK. The DQPSK encoder is specified in Table 6 above.

The phase change for

1 is relative to the phase

1 of the

preceding symbol. In the case of rate change, the phase

change for

1 is relative to the phase

1 of the preceding

CCK symbol. All odd numbered symbols of the MPDU are

given an extra 180 degree (

π

) rotation in accordance with the

DQPSK modulation as shown in Table 7. Symbol numbering

starts with “0” for the first symbol of the MPDU.

The data dibits: (d2, d3), (d4, d5), (d6, d7) encode

2,

3,

and

4 respectively based on QPSK as specified in Table 7.

Note that this table is binary, not Grey, coded.

TX Power Control

The transmitter power can be controlled by the MAC via two

registers. The first register, CR58, contains the results of

power measurements digitized by the HFA3863. By

comparing this measurement to what the MAC needs for

transmit power, the MAC can determine whether to raise or

lower the transmit power. It does this by writing the power

level desired to register CR31.

Clear Channel Assessment (CCA) and

Energy Detect (ED) Description

The Clear Channel Assessment (CCA) circuit implements the

carrier sense portion of a Carrier Sense Multiple Access

(CSMA) networking scheme. The Clear Channel Assessment

(CCA)monitorstheenvironmenttodeterminewhenitisclearto

transmit. The CCA circuit in the HFA3863 can be programmed

to be a function of RSSI (energy detected on the channel),

CS1, SQ1, or various combinations. The CCA output goes to

the Media Access Controller (MAC). The MAC decides on

transmission based on traffic to send and the CCA indication.

The CCA indication can be ignored, allowing transmissions

independent of any channel conditions. The CCA in

combination with the visibility of the various internal parameters

(i.e., Energy Detection measurement results), can assist the

MACinexecutingalgorithmsthatcanadapttotheenvironment.

These algorithms can increase network throughput by

minimizing collisions and reducing transmissions liable to

errors.

There are three measures that can be used in the CCA

assessment. The receive signal strength indication (RSSI)

which indicates the energy at the antenna, CS1 and carrier

sense (SQ1). CS1 becomes active anytime the AGC portion

of the circuit becomes unlocked, which is likely at the onset

of a signal that is strong enough to support 11Mbps, but may

not occur with the onset of a signal that is only strong

enough to support 1 or 2MBps. CS1 stays active until the

AGC locks and a SQ1 assessment is done, if SQ1 is false,

then CS1 is cleared, which deasserts CCA. If SQ1 is true,

then tracking is begun, and CCA continues to show the

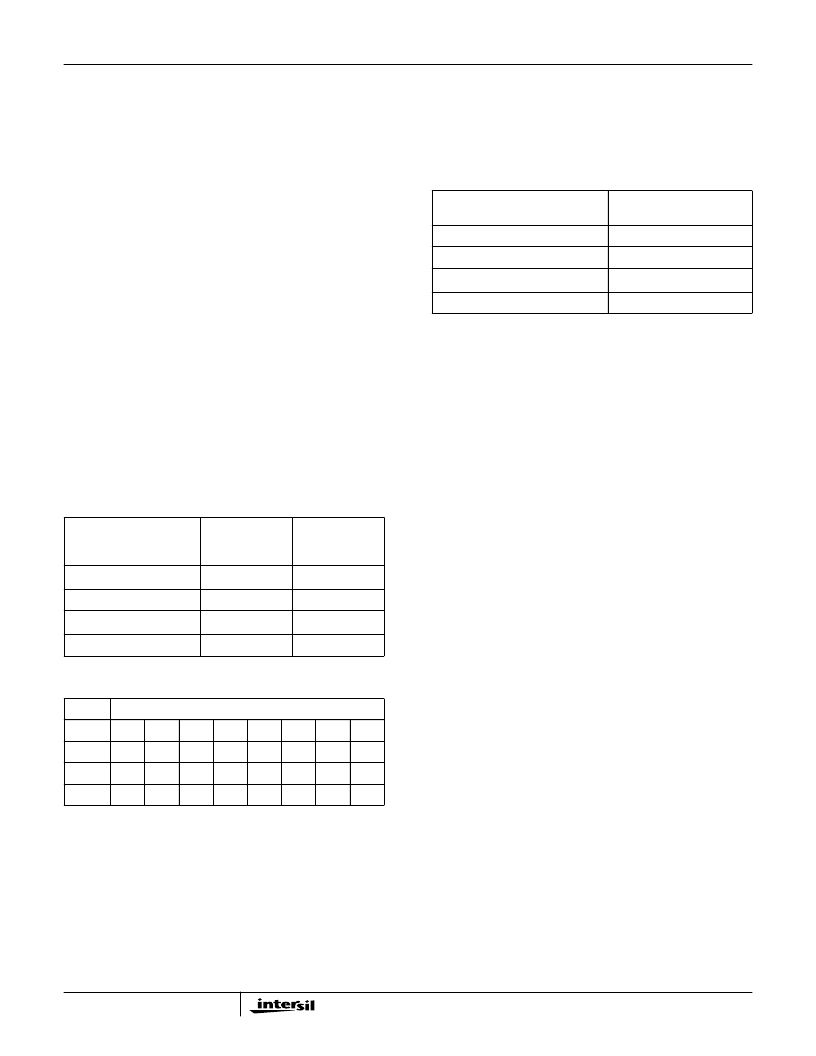

TABLE 5. DQPSK ENCODING TABLE

DIBIT PATTERN (d(0), d(1))

d(0) IS FIRST IN TIME

EVEN SYMBOLS

PHASECHANGE

(+j

ω)

ODD SYMBOLS

PHASECHANGE

(+j

ω

)

π

3

π

/2 (-

π

/2)

00

0

01

π

/2

π

11

0

10

3

π

/2 (-

π

/2)

π

/2

TABLE 6. 5.5Mbps CCK ENCODING TABLE

d2, d3

CHIPS

00

1

j

1

1

j

-1

1

j

1

-1

j

1

01

-1

j

-1

-1

j

1

1

j

1

-1

j

1

10

-1

j

1

-1

j

-1

-1

j

1

1

j

1

11

1

j

-1

1

j

1

-1

j

1

1

j

1

TABLE 7. QPSK ENCODING TABLE

DIBIT PATTERN (d(i), d(i+1))

d(i) IS FIRST IN TIME

PHASE

00

0

01

π

/2

π

10

11

3

π

/2 (-

π

/2)

HFA3863

相关PDF资料 |

PDF描述 |

|---|---|

| HFA3983IV96 | 2.4GHz Power Amplifier and Detector |

| HFA3983 | 2.4GHz Power Amplifier and Detector(2.4GHz 功率放大器探测器) |

| HFA3983IV | 2.4GHz Power Amplifier and Detector |

| HFB60HF20 | 200V 60A Hi-Rel Ultra-Fast Discrete Diode in a SMD-1 package |

| HFB60HF20C | 200V 60A Hi-Rel Ultra-Fast Common Cathode Diode in a SMD-1 package |

相关代理商/技术参数 |

参数描述 |

|---|---|

| HFA3863IN | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:Direct Sequence Spread Spectrum Baseband Processor |

| HFA3863IN96 | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:Direct Sequence Spread Spectrum Baseband Processor |

| HFA3925 | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:null2.4GHz - 2.5GHz 250mW Power Amplifier |

| HFA3925IA | 制造商:Rochester Electronics LLC 功能描述:- Bulk 制造商:Harris Corporation 功能描述: |

| HFA3925IA1K | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

发布紧急采购,3分钟左右您将得到回复。