参数资料

| 型号: | HI1-565AJD-5 |

| 厂商: | Intersil |

| 文件页数: | 6/9页 |

| 文件大小: | 0K |

| 描述: | CONV D/A 12BIT 6.7MHZ 24-DIP |

| 标准包装: | 165 |

| 位数: | 12 |

| 数据接口: | 并联 |

| 转换器数目: | 1 |

| 电压电源: | 双 ± |

| 功率耗散(最大): | 250mW |

| 工作温度: | 0°C ~ 75°C |

| 安装类型: | 通孔 |

| 封装/外壳: | 24-CDIP(0.600",15.24mm) |

| 供应商设备封装: | 24-DIP |

| 包装: | 管件 |

| 输出数目和类型: | 1 电流,单极;1 电流,双极 |

| 采样率(每秒): | 6.7M |

6

Settling Time

This is a challenging measurement, in which the result

depends on the method chosen, the precision and quality of

test equipment and the operating configuration of the DAC

(test conditions). As a result, the different techniques in use

by converter manufacturers can lead to consistently different

results. An engineer should understand the advantage and

limitations of a given test method before using the specified

settling time as a basis for design.

The previous approach calls for a strobed comparator to

sense final perturbations of the DAC output waveform. This

gives the LSB a reasonable magnitude (814

V for the

HI-565A), which provides the comparator with enough

overdrive to establish an accurate

±0.5 LSB window about the

final settled value. Also, the required test conditions simulate

the DACs environment for a common application - use in a

successive approximation A/D converter. Considerable

experience has shown this to be a reliable and repeatable

way to measure settling time.

The usual specification is based on a 10V step, produced by

simultaneously switching all bits from off-to-on (tON) or on-

to-off (tOFF). The slower of the two cases is specified, as

measured from 50% of the digital input transition to the final

entry within a window of

±0.5 LSB about the settled value.

Four measurements characterize a given type of DAC:

(a)

tON, to final value +0.5 LSB

(b)

tON, to final value -0.5 LSB

(c)

tOFF, to final value +0.5 LSB

(d)

tOFF, to final value -0.5 LSB

(Cases (b) and (c) may be eliminated unless the overshoot

exceeds 0.5 LSB). For example, refer to Figure 3 for the

measurement of case (d).

Procedure

As shown in Figure 3B, settling time equals tX plus the

comparator delay (tD = 15ns). To measure tX:

Adjust the delay on generator No. 2 for a tX of several

microseconds. This assures that the DAC output has

settled to its final value.

Switch on the LSB (+5V).

Adjust the VLSB supply for 50% triggering at

COMPARATOR OUT. This is indicated by traces of

equal brightness on the oscilloscope display as shown

in Figure 3B. Note DVM reading.

Switch the LSB to Pulse (P).

Readjust the VLSB supply for 50% triggering as before,

and note DVM reading. One LSB equals one tenth the

difference in the DVM readings noted above.

Adjust the VLSB supply to reduce the DVM reading by

5 LSBs (DVM reads 10X, so this sets the comparator to

sense the final settled value minus 0.5 LSB).

Comparator output disappears.

Reduce generator No. 2 delay until comparator output

reappears, and adjust for “equal brightness”.

Measure tX from scope as shown in Figure 3B. Settling

time equals tX + tD, i.e., tX + 15ns.

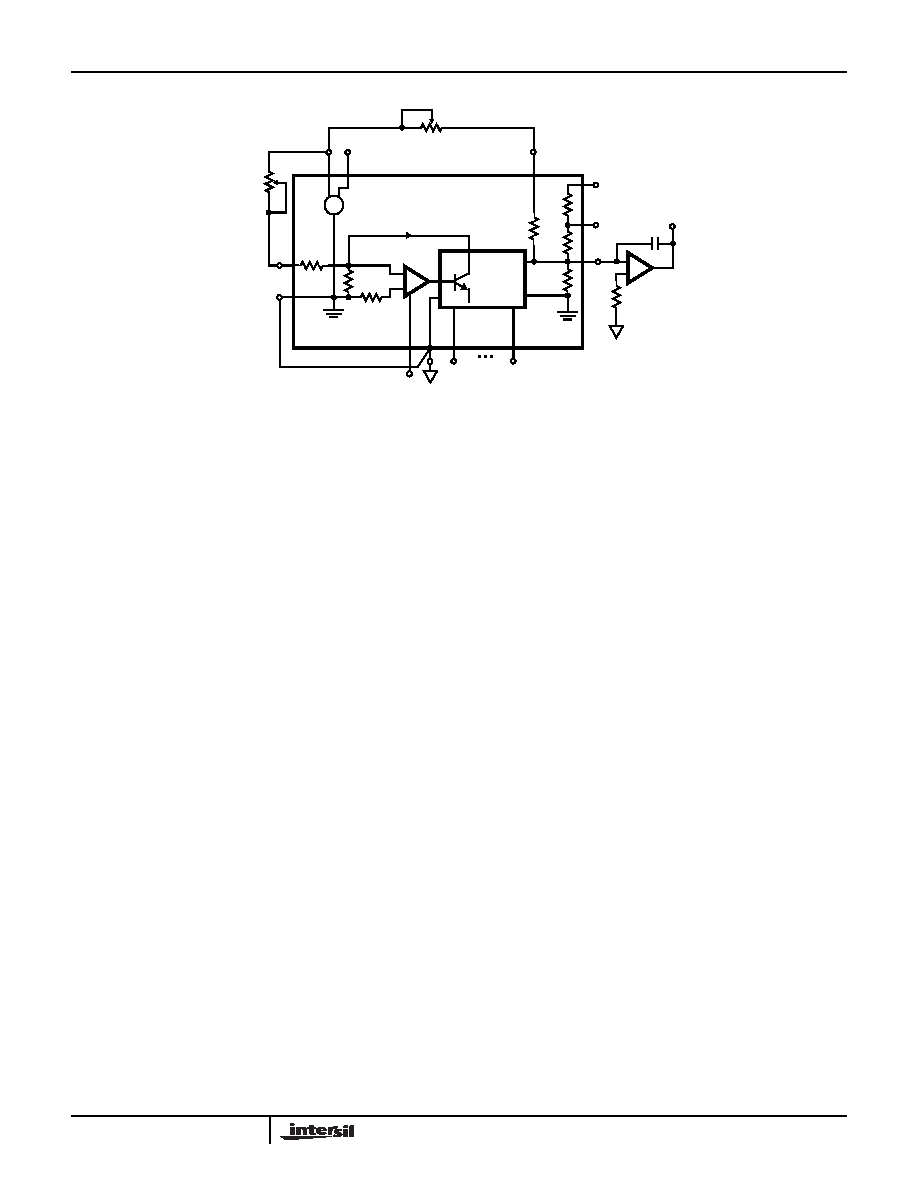

REF OUT

x CODE)

(4 x I REF

IO

3.5K

3K

CODE

INPUT

DAC

2.5K

5K

9

DAC

OUT

C

9.95K

5K

10

11

20V SPAN

10V SPAN

VO

R(SEE

0.5mA

I REF

HI-565A

19.95K

+

-

43

6

5

8

BIP.

OFF.

VCC

712

24

13

MSB

LSB

REF

GND

REF

IN

100

10V

-VEE

PWR

GND

R4

100

R3

TABLE 2)

+

-

+

-

FIGURE 2. BIPOLAR VOLTAGE OUTPUT

HI-565A

相关PDF资料 |

PDF描述 |

|---|---|

| HI1171JCB-T | CONV D/A 8BIT 40MSPS HS 24-SOIC |

| HI1175JCB-T | CONV A/D 8BIT 20MSPS 24-SOIC |

| HI1178JCQ | CONV D/A 8BIT TRPL 40MHZ 48-PQFP |

| HI3-674AKN-5 | IC ADC 12BIT 67KSPS 28-SBDIP |

| HI3-7159A-5Z | IC ADC 5-1/2 DIGIT 28-PDIP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| HI1-565AKD-5 | 制造商:Rochester Electronics LLC 功能描述:24 CDIP, 0+75, +15V,12-BIT D/A CONVERTER W/REF - Bulk 制造商:Harris Corporation 功能描述: 制造商:Intersil Corporation 功能描述: |

| HI1-565ASD/883 | 制造商:Intersil Corporation 功能描述:DAC SGL R-2R 12-BIT 24PIN SBDIP - Rail/Tube 制造商:Rochester Electronics LLC 功能描述:DAC 12BIT 6.7MHZ 0.25LSB 24CDIP /883 - Bulk |

| HI1-565ASD-2 | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:High Speed, Monolithic D/A Converter with Reference |

| HI1-565ASD-8 | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| HI1-565ATD/883 | 制造商:Rochester Electronics LLC 功能描述:24 CDIP, -55+125,+15V,12-BIT D/A CONVERTER W/REF - Bulk 制造商:Harris Corporation 功能描述: |

发布紧急采购,3分钟左右您将得到回复。