参数资料

| 型号: | HIP6004BCVZ-T |

| 厂商: | Intersil |

| 文件页数: | 6/15页 |

| 文件大小: | 0K |

| 描述: | IC CTRLR PWM VOLTAGE MON 20TSSOP |

| 标准包装: | 2,500 |

| 应用: | 控制器,Intel Pentium?,II,Pro |

| 输入电压: | 5V,12V |

| 输出数: | 1 |

| 输出电压: | 1.3 V ~ 3.5 V |

| 工作温度: | 0°C ~ 70°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 20-TSSOP(0.173",4.40mm 宽) |

| 供应商设备封装: | 20-TSSOP |

| 包装: | 带卷 (TR) |

�� �

�

�

�HIP6004B�

�GND� (Pin� 11)�

�Signal� ground� for� the� IC.� All� voltage� levels� are� measured�

�with� respect� to� this� pin.�

�PGOOD� (Pin� 12)�

�PGOOD� is� an� open� collector� output� used� to� indicate� the�

�status� of� the� converter� output� voltage.� This� pin� is� pulled� low�

�when� the� converter� output� is� not� within� ±� 10%� of� the�

�DACOUT� reference� voltage.� Exception� to� this� behavior� is� the�

�‘11111’� VID� pin� combination� which� disables� the� converter;� in�

�this� case� PGOOD� asserts� a� high� level.�

�PHASE� (Pin� 13)�

�Connect� the� PHASE� pin� to� the� upper� MOSFET� source.� This�

�pin� is� used� to� monitor� the� voltage� drop� across� the� MOSFET�

�for� over-current� protection.� This� pin� also� provides� the� return�

�path� for� the� upper� gate� drive.�

�UGATE� (Pin� 14)�

�Connect� UGATE� to� the� upper� MOSFET� gate.� This� pin�

�provides� the� gate� drive� for� the� upper� MOSFET.�

�BOOT� (Pin� 15)�

�This� pin� provides� bias� voltage� to� the� upper� MOSFET� driver.�

�A� bootstrap� circuit� may� be� used� to� create� a� BOOT� voltage�

�suitable� to� drive� a� standard� N-Channel� MOSFET.�

�PGND� (Pin� 16)�

�This� is� the� power� ground� connection.� Tie� the� lower� MOSFET�

�source� to� this� pin.�

�LGATE� (Pin� 17)�

�Connect� LGATE� to� the� lower� MOSFET� gate.� This� pin�

�provides� the� gate� drive� for� the� lower� MOSFET.�

�V� CC� (Pin� 18)�

�Provide� a� 12V� bias� supply� for� the� chip� to� this� pin.�

�OVP� (Pin� 19)�

�The� OVP� pin� can� be� used� to� drive� an� external� SCR� in� the�

�event� of� an� overvoltage� condition.� Output� rising� 15%� more�

�than� the� DAC-set� voltage� triggers� a� high� output� on� this� pin�

�and� disables� PWM� gate� drive� circuitry.�

�RT� (Pin� 20)�

�This� pin� provides� oscillator� switching� frequency� adjustment.�

�By� placing� a� resistor� (R� T� )� from� this� pin� to� GND,� the� nominal�

�200kHz� switching� frequency� is� increased� according� to� the�

�following� equation:�

�Functional� Description�

�Initialization�

�The� HIP6004B� automatically� initializes� upon� receipt� of� power.�

�Special� sequencing� of� the� input� supplies� is� not� necessary.� The�

�Power-On� Reset� (POR)� function� continually� monitors� the� input�

�supply� voltages.� The� POR� monitors� the� bias� voltage� at� the� V� CC�

�pin� and� the� input� voltage� (V� IN� )� on� the� OCSET� pin.� The� level� on�

�OCSET� is� equal� to� V� IN� less� a� fixed� voltage� drop� (see� over-�

�current� protection).� The� POR� function� initiates� soft� start�

�operation� after� both� input� supply� voltages� exceed� their� POR�

�thresholds.� For� operation� with� a� single� +12V� power� source,� V� IN�

�and� V� CC� are� equivalent� and� the� +12V� power� source� must�

�exceed� the� rising� V� CC� threshold� before� POR� initiates� operation.�

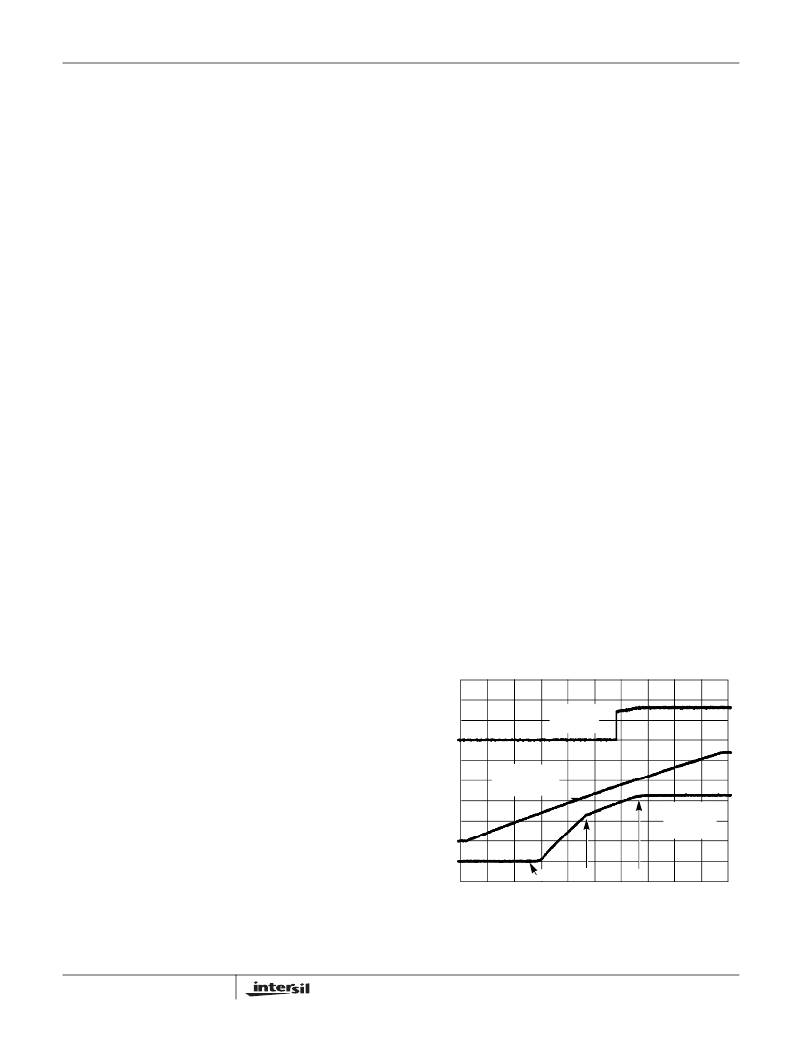

�Soft� Start�

�The� POR� function� initiates� the� soft� start� sequence.� An� internal�

�10μA� current� source� charges� an� external� capacitor� (C� SS� )� on�

�the� SS� pin� to� 4V.� Soft� start� clamps� the� error� amplifier� output�

�(COMP� pin)� and� reference� input� (+� terminal� of� error� amp)� to� the�

�SS� pin� voltage.� Figure� 3� shows� the� soft� start� interval� with�

�C� SS� =� 0.1μF.� Initially� the� clamp� on� the� error� amplifier� (COMP�

�pin)� controls� the� converter’s� output� voltage.� At� t� 1� in� Figure� 3,�

�the� SS� voltage� reaches� the� valley� of� the� oscillator’s� triangle�

�wave.� The� oscillator’s� triangular� waveform� is� compared� to� the�

�ramping� error� amplifier� voltage.� This� generates� PHASE� pulses�

�of� increasing� width� that� charge� the� output� capacitor(s).� This�

�interval� of� increasing� pulse� width� continues� to� t� 2� .� With� sufficient�

�output� voltage,� the� clamp� on� the� reference� input� controls� the�

�output� voltage.� This� is� the� interval� between� t� 2� and� t� 3� in� Figure� 3.�

�At� t� 3� the� SS� voltage� exceeds� the� DACOUT� voltage� and� the�

�output� voltage� is� in� regulation.� This� method� provides� a� rapid�

�and� controlled� output� voltage� rise.� The� PGOOD� signal� toggles�

�‘high’� when� the� output� voltage� (V� SEN� pin)� is� within� ±� 5%� of�

�DACOUT.� The� 2%� hysteresis� built� into� the� power� good�

�comparators� prevents� PGOOD� oscillation� due� to� nominal�

�output� voltage� ripple.�

�PGOOD�

�(2V/DIV)�

�0V�

�SOFT-START�

�(1V/DIV)�

�OUTPUT�

�Fs� ≈� 200kHz� +� ---------------------�

�6�

�5� x� 10�

�R� T� (� k� ?� )�

�(R� T� to� GND)�

�0V�

�VOLTAGE�

�(1V/DIV)�

�0V�

�Conversely,� connecting� a� pull-up� resistor� (R� T� )� from� this� pin�

�t� 1�

�t� 2�

�t� 3�

�to� V� CC� reduces� the� switching� frequency� according� to� the�

�following� equation:�

�TIME� (5ms/DIV)�

�FIGURE� 3.� SOFT� START� INTERVAL�

�Fs� ≈� 200kHz� –� ---------------------�

�7�

�4� x� 10�

�R� T� (� k� ?� )�

�(R� T� to� 12V)�

�6�

�相关PDF资料 |

PDF描述 |

|---|---|

| ABM06DTAT-S664 | CONN EDGECARD 12POS R/A .156 SLD |

| ISL6568CRZ-TKR5184 | IC CTRLR PWM 2PHASE BUCK 32-QFN |

| LT1963AET#06PBF | IC REG LDO ADJ 1.5A TO220-5 |

| GSA31DTKN-S288 | CONN EDGECARD 62POS .125 EXTEND |

| LT1120CS8#PBF | IC REG LDO ADJ 125MA 8SOIC |

相关代理商/技术参数 |

参数描述 |

|---|---|

| HIP6004CB | 制造商:Rochester Electronics LLC 功能描述:SYNC BUCK PWM W/5 BIT DAC 20 SOIC - Bulk |

| HIP6004CB WAF | 制造商:Harris Corporation 功能描述: |

| HIP6004CBR4543 | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| HIP6004CB-T | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| HIP6004CBTS | 制造商:HARRIS 功能描述:* |

发布紧急采购,3分钟左右您将得到回复。