- 您现在的位置:买卖IC网 > PDF目录370643 > HMP8112EVAL2 (Harris Corporation) NTSC/PAL Video Decoder PDF资料下载

参数资料

| 型号: | HMP8112EVAL2 |

| 厂商: | Harris Corporation |

| 英文描述: | NTSC/PAL Video Decoder |

| 中文描述: | NTSC / PAL视频解码器 |

| 文件页数: | 12/40页 |

| 文件大小: | 563K |

| 代理商: | HMP8112EVAL2 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页当前第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页

12

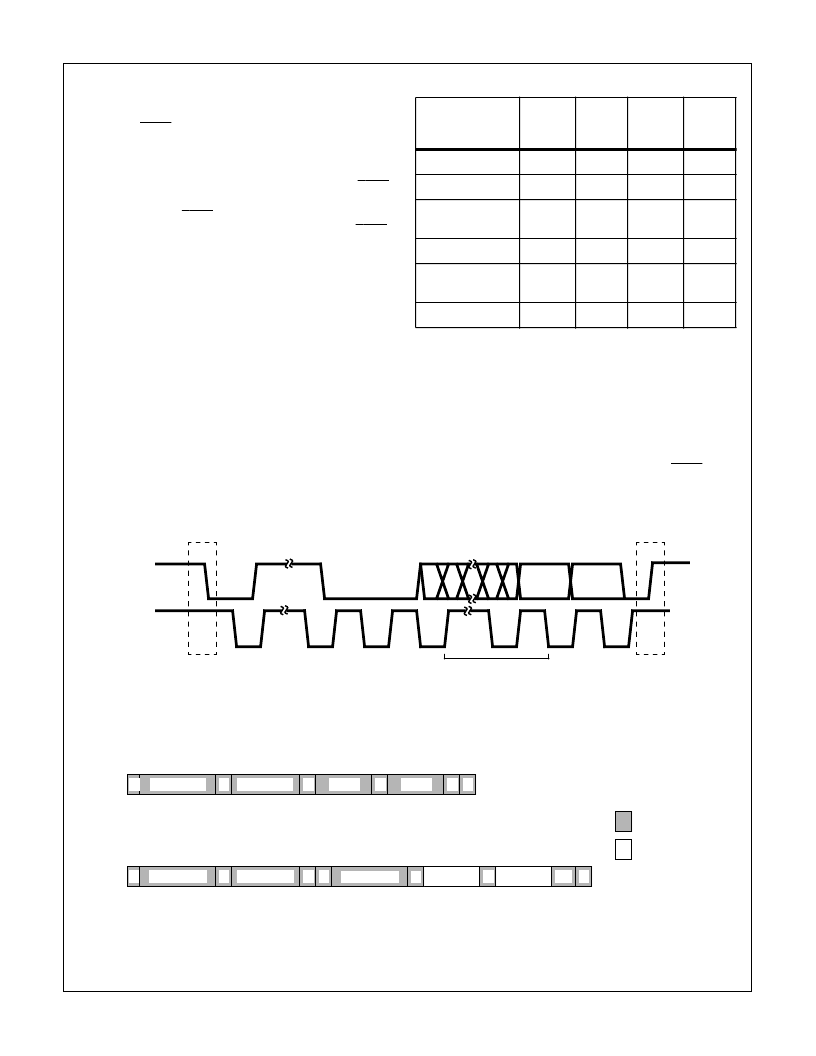

CLK frequency and Table 5 shows the number of data points

per video line to expect for a given standard. Data is output as

4:2:2 subsampled data in a Y-Cb/Y-Cr 16-bit sequence. The

Data Valid (DVLD) flag is asserted when video data is present

on the 16-bit output port of the HMP8112 (Y[7:0], CbCr[7:0]).

The ACTIVE flag is asserted when the active video portion of

the horizontal scan line is present on the data output port. See

Figure 15 for Synchronous Pixel Transfer Mode timing. DVLD is

asserted every time the output sample rate converter has a

valid output. When DVLD and ACTIVE are used together the

visual portion of the image can be captured. When DVLD is

used alone all valid data during the Horizontal, Vertical and Ref-

erence Burst Timing are available. ACTIVE is asserted from

lines 22 through 262.5 and lines 285.5 through 525 for NTSC

(and PAL M). Active is asserted from lines 23.5 through 310

and lines 336 through 623.5 for PAL (B, D, G, H, I, N, Comb N).

The CLK can be run on a 20MHz - 30MHz clock source. Data

will be output (on average) at the Output Data Rate shown in

Table 5 for a given standard. Data is clocked out synchronous

to CLK and will come in bursts. To smooth out the data rate to

a regular rate a CLK of 2X the average output data rate can

be used. In the 16-bit pixel transfer, data is sequenced on the

CbCr[7:0] data bus, starting with Cb and then Cr.

For Burst Mode output format the Y[7:0] output bus is used

to transfer all YCbCr data in 8-bit format. The data is also

4:2:2 subsampled but will only contain the active video por-

tion of the line. The HMP8112 uses an internal 32 deep fifo

to handle latencies between the output sample rate and the

CLK frequency. In this mode, the data is clocked out at the

CLK rate and only clock frequencies of 24.5454MHz, 27MHz

and 29.5MHz can be used. In 8-bit data mode, the data is

sequenced on the Y[7:0] bus in Cb, Y, Cr, Y format. ACTIVE

is asserted as soon as the mode is selected. DVLD when

asserted indicates a valid active pixel is available. Pixels dur-

ing the horizontal and vertical blanking are not available.

Only the active portions of the video line are output.

TABLE 5. OUTPUT MODE STANDARDS

STANDARD

OUTPUT

DATA

RATE

ACTIVE

PIXELS/

LINE

TOTAL

PIXELS/

LINE

TOTAL

LINES/

FIELD

NTSC Square Pixel

12.27MHz

640

780

262.5

NTSC CCIR 601

13.5MHz

720

858

262.5

PAL B, D, G, H, I, N,

COMB N, CCIR601

13.5MHz

720

864

312.5

PAL M CCIR 601

13.5MHz

720

858

262.5

PAL B, D, G, H, I, N

Square Pixel

14.74MHz

768

944

312.5

PAL M Square Pixel 14.74MHz

640

780

312.5

SDA

SCL

START

CONDITION

S

1-7

ADDRESS

8

R/W

9

ACK

1-7

DATA

8

9

ACK

STOP

CONDITION

P

FIGURE 13. I

2

C SERIAL TIMING FLOW

S = START CYCLE

P = STOP CYCLE

A = ACKNOWLEDGE

NA = NO ACKNOWLEDGE

FROM MASTER

FROM HMP8112

0x88

DATA WRITE

DATA

DATA

0x88

DATA READ

REGISTER

POINTED

TO BY

SUBADDR

REGISTER

POINTED

TO BY

SUBADDR

0x89

1000 100 (R/W)

1000 100 (R/W)

FIGURE 14. REGISTER WRITE PROGRAMMING FLOW

S

CHIP ADDR

A

SUB ADDR

A

DATA

DATA

A

A

P

NA

A

A

CHIP ADDR

S

A

SUB ADDR

A

CHIP ADDR

S

P

HMP8112

相关PDF资料 |

PDF描述 |

|---|---|

| HMP8156EVAL2 | NTSC/PAL Video Decoder |

| HMP8156EVAL1 | NTSC/PAL Encoders |

| HMP8156EVAL2 | NTSC/PAL Encoders |

| HMP8156 | NTSC/PAL Encoder |

| HMP8156ACN | NTSC/PAL Encoders |

相关代理商/技术参数 |

参数描述 |

|---|---|

| HMP8115 | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:NTSC/PAL Video Decoder |

| HMP8115CN | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:NTSC/PAL Video Decoder |

| HMP8116 | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:NTSC/PAL Video Decoder |

| HMP8116CN | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:NTSC/PAL Video Decoder |

| HMP8117 | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:NTSC/PAL Video Decoder |

发布紧急采购,3分钟左右您将得到回复。