- 您现在的位置:买卖IC网 > PDF目录370740 > HY5DV651622TC-G55 DDR Synchronous DRAM PDF资料下载

参数资料

| 型号: | HY5DV651622TC-G55 |

| 英文描述: | DDR Synchronous DRAM |

| 中文描述: | DDR同步DRAM |

| 文件页数: | 15/27页 |

| 文件大小: | 273K |

| 代理商: | HY5DV651622TC-G55 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页当前第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页

Rev. 0.3/May. 02

15

HY5DV281622AT

POWER-UP SEQUENCE AND DEVICE INITIALIZATION

DDR SDRAMs must be powered up and initialized in a predefined manner. Operational procedures other than those

specified may result in undefined operation. Power must first be applied to V

DD

, then to V

DDQ

, and finally to V

REF

(and

to the system V

TT

). V

TT

must be applied after V

DDQ

to avoid device latch-up, which may cause permanent damage to

the device. V

REF

can be applied anytime after V

DDQ

, but is expected to be nominally coincident with V

TT

. Except for

CKE, inputs are not recognized as valid until after V

REF

is applied. CKE is an SSTL_2 input, but will detect an LVCMOS

LOW level after V

DD

is applied. Maintaining an LVCMOS LOW level on CKE during power-up is required to guarantee

that the DQ and DQS outputs will be in the High-Z state, where they will remain until driven in normal operation (by a

read access). After all power supply and reference voltages are stable, and the clock is stable, the DDR SDRAM

requires a 200us delay prior to applying an executable command.

Once the 200us delay has been satisfied, a DESELECT or NOP command should be applied, and CKE should be

brought HIGH. Following the NOP command, a PRECHARGE ALL command should be applied. Next a EXTENDED

MODE REGISTER SET command should be issued for the Extended Mode Register, to enable the DLL, then a MODE

REGISTER SET command should be issued for the Mode Register, to reset the DLL, and to program the operating

parameters. 200 clock cycles are required between the DLL reset and any command. During the 200 cycles of CK, for

DLL locking, executable commands are disallowed (a DESELECT or NOP command must be applied). After the 200

clock cycles, a PRECHARGE ALL command should be applied, placing the device in the all banks idle state.

Once in the idle state, two AUTO REFRESH cycles must be performed. Additionally, a MODE REGISTER SET command

for the Mode Register with the reset DLL bit deactivated (i.e. to program operating parameters without resetting the

DLL) must be performed. Following these cycles, the DDR SDRAM is ready for normal operation.

1.

Apply power - V

DD

, V

DDQ

, V

TT

, V

REF

in the following power up sequencing and attempt to maintain CKE at LVC-

MOS low state. (All the other input pins may be undefined.)

V

DD

and V

DDQ

are driven from a single power converter output.

V

TT

is limited to 1.44V (reflecting VDDQ(max)/2 + 50mV VREF variation + 40mV VTT variation.

V

REF

tracks V

DDQ

/2.

A minimum resistance of 42 Ohms (22 ohm series resistor + 22 ohm parallel resistor - 5% tolerance) limits the

input current from the V

TT

supply into any pin.

If the above criteria cannot be met by the system design, then the following sequencing and voltage relation-

ship must be adhered to during power up.

2.

Start clock and maintain stable clock for a minimum of 200usec.

3.

After stable power and clock, apply NOP condition and take CKE high.

4.

Issue Extended Mode Register Set (EMRS) to enable DLL.

5.

Issue Mode Register Set (MRS) to reset DLL and set device to idle state with bit A8=High. (An additional 200

cycles of clock are required for locking DLL)

6.

Issue Precharge commands for all banks of the device.

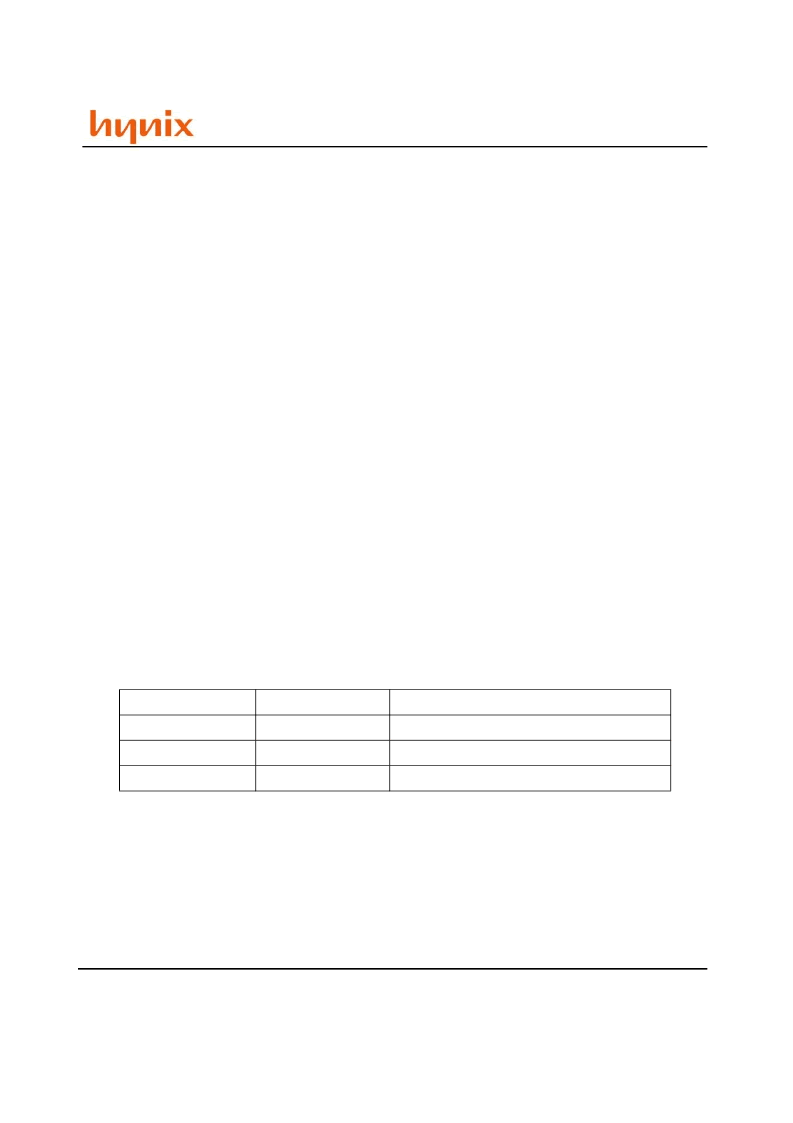

Votage description

Sequencing

Voltage relationship to avoid latch-up

V

DDQ

After or with V

DD

< V

DD

+ 0.3V

V

TT

After or with V

DDQ

< V

DDQ

+ 0.3V

V

REF

After or with V

DDQ

< V

DDQ

+ 0.3V

相关PDF资料 |

PDF描述 |

|---|---|

| HY5DV651622TC-G6 | DDR Synchronous DRAM |

| HY5DV651622TC-G7 | DDR Synchronous DRAM |

| HY5DV651622T-G55 | DDR Synchronous DRAM |

| HY5DV651622T-G6 | DDR Synchronous DRAM |

| HY5DV651622T-G7 | DDR Synchronous DRAM |

相关代理商/技术参数 |

参数描述 |

|---|---|

| HY5DV651622TC-G6 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:DDR Synchronous DRAM |

| HY5DV651622TC-G7 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:DDR Synchronous DRAM |

| HY5DV651622T-G55 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:DDR Synchronous DRAM |

| HY5DV651622T-G6 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:DDR Synchronous DRAM |

| HY5DV651622T-G7 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:DDR Synchronous DRAM |

发布紧急采购,3分钟左右您将得到回复。