- 您现在的位置:买卖IC网 > PDF目录224000 > HYS72D64020GR-7-X (INFINEON TECHNOLOGIES AG) 64M X 72 DDR DRAM MODULE, 0.75 ns, DMA184 PDF资料下载

参数资料

| 型号: | HYS72D64020GR-7-X |

| 厂商: | INFINEON TECHNOLOGIES AG |

| 元件分类: | DRAM |

| 英文描述: | 64M X 72 DDR DRAM MODULE, 0.75 ns, DMA184 |

| 封装: | DIMM-184 |

| 文件页数: | 3/23页 |

| 文件大小: | 277K |

| 代理商: | HYS72D64020GR-7-X |

HYS 72Dxx0x0GR

Registered DDR-I SDRAM-Modules

INFINEON Technologies

11

2.01

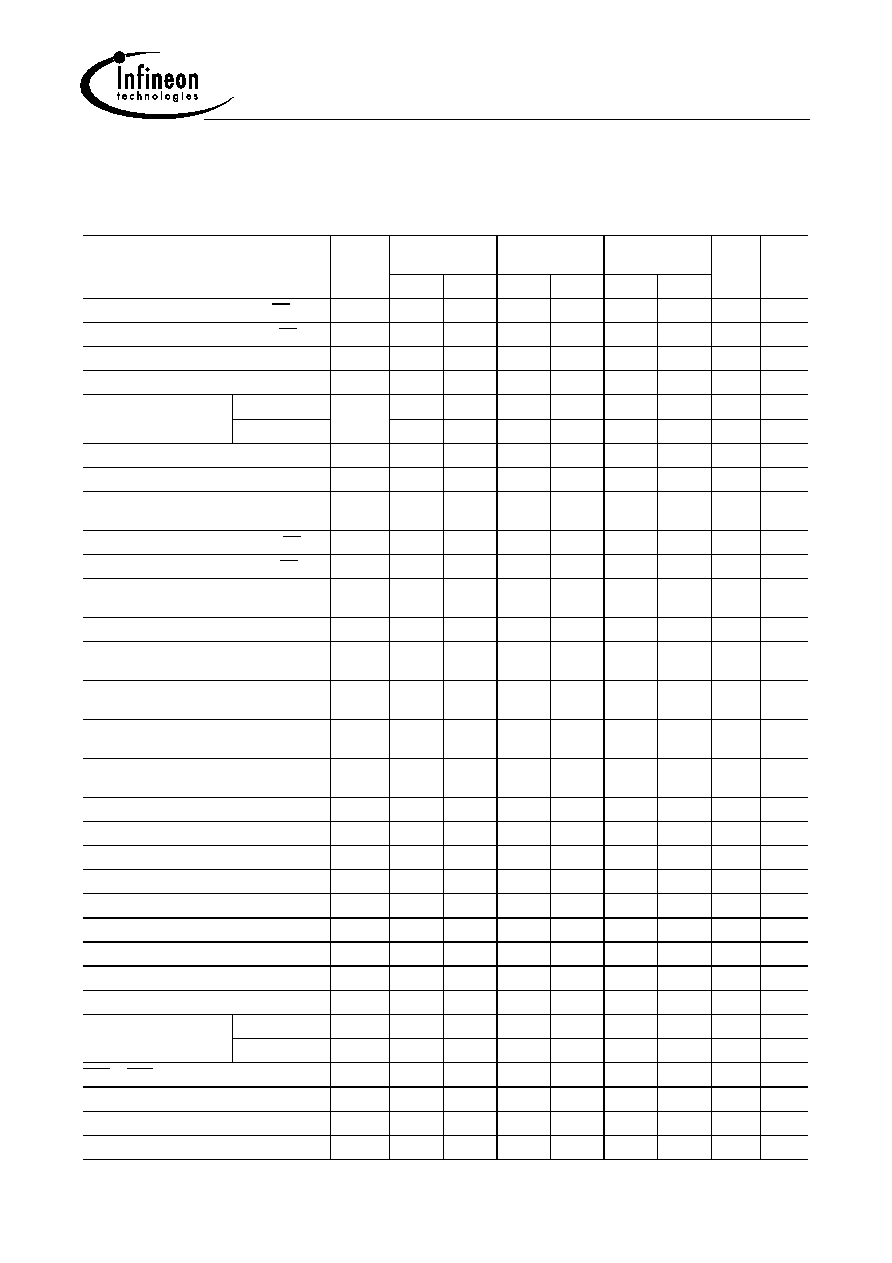

AC Characteristics (for reference only)

(values apply to the SDRAM component and do not include register, PLL, or card wiring)

(

T

A =0 to +70 °C, VDD =2.5 V±0.2 V)

Parameter

Symbol

-7

DDR266A

-7.5

DDR266B

-8

DDR200

Unit

Notes

min.

max.

min.

max.

min.

max.

DQ Output Access Time from CK/CK

t

AC

– 0.75

+ 0.75

– 0.75

+ 0.75

– 0.8

+ 0.8

ns

–

DQS Output access Time from CK/CK

t

DQSCK

– 0.75

+ 0.75

– 0.75

+ 0.75

– 0.8

+ 0.8

ns

–

CLK High Level Width

t

CH

0.45

0.55

0.45

0.55

0.45

0.55

tCK

–

CLK Low Level Width

t

CL

0.45

0.55

0.45

0.55

0.45

0.55

tCK

–

Clock Period

CL = 2

t

CK

7.5

1210

12

1012ns

1)

CL = 2.5

712

7.5

12

812

ns

–

DQ and DM Input Hold Time

t

DH

0.5

–

0.5

–

0.6

–

ns

–

DQ and DM Input Setup Time

t

DS

0.5

–

0.5

–

0.6

–

ns

–

DQ and DM Input Pulse Width

(for each input)

t

DIPW

1.75

–

1.75

–

2

–

ns

–

Data-Out High-impedance from CK/CK

t

HZ

– 0.75

+ 0.75

– 0.75

+ 0.75

– 0.8

+ 0.8

ns

–

Data-Out Low-impedance from CK/CK

t

LZ

– 0.75

+ 0.75

– 0.75

+ 0.75

– 0.8

+ 0.8

ns

–

Write Command to First DQS Latching

Transition

t

DQSS

0.75

1.25

0.75

1.25

0.75

1.25

t

CK

–

DQS-DQ Skew

t

DQSQ

–

+0.5

–

+0.5

–

+0.6

ns

–

QH Data-Out Hold Time from DQS

t

QH

tHP-

0.75

–

tHP-

0.75

–

tHP-1.0 –

ns

2)

DQS input low (high) pulse width

(write cycle)

t

DQSL;H

0.35

–

0.35

–

0.35

–

t

CK

DQS falling edge to CK setup time

(write cycle)

t

DSS

0.2

–

0.2

–

0.2

–

t

CK

–

DQS falling edge hold time from CK

(write cycle)

t

DSH

0.2

–

0.2

–

0.2

–

t

CK

Mode register set command cycle time

t

MRD

14

–

15

–

16

–

ns

–

Write Preamble Setup Time

t

WPRES

0

–

0

–

0

–

ns

–

Write Postamble

t

WPST

0.40.6

0.4

0.6

t

CK

–

Write Preamble

t

WPRE

0.25

–

0.25

–

0.25

–

t

CK

Address and control input setup time

t

IS

0.9

–

0.9

–

1.2

–

ns

3)

Address and control input hold time

t

IH

0.9

–

0.9

–

1.2

–

ns

3)

Read Preamble

t

RPRE

0.91.1

0.9

1.1

t

CK

–

Read Postamble

t

RPST

0.40.6

0.4

0.6

t

CK

–

Row Active Time

t

RAS

45

120K

45

120k

50

120K

ns

–

Row Cycle Time

R/W Operation

t

RC

65

–

65

–

70

–

ns

–

Auto Refresh

t

RFC

75

–

75

–

80

–

ns

1)

RAS to CAS Delay

t

RCD

20

–

20

–

20

–

ns

–

Row Precharge Time

t

RP

20

–

20

–

20

–

ns

–

Active bank A to Active bank B command

t

RRD

15

–

15

–

15

–

ns

–

Write Recovery Time

t

WR

15

–

15

–

15

–

ns

–

相关PDF资料 |

PDF描述 |

|---|---|

| HYS72D64020GR-7.5-X | 64M X 72 DDR DRAM MODULE, 0.75 ns, DMA184 |

| HYS72T128000EU-2.5-C2 | 128M X 72 DDR DRAM MODULE, 0.4 ns, DMA240 |

| HYS72T64000EP-3.7-B2 | 64M X 72 DDR DRAM MODULE, DMA240 |

| HZ20-1 | 19.25 V, 0.5 W, SILICON, UNIDIRECTIONAL VOLTAGE REGULATOR DIODE, DO-35 |

| HZ6B1L | 5.65 V, 0.4 W, SILICON, UNIDIRECTIONAL VOLTAGE REGULATOR DIODE, DO-35 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| HYS72D64020GR-8-A | 制造商:INFINEON 制造商全称:Infineon Technologies AG 功能描述:2.5 V 184-pin Registered DDR-I SDRAM Modules |

| HYS72D64020GR-8-B | 制造商:INFINEON 制造商全称:Infineon Technologies AG 功能描述:2.5 V 184-pin Registered DDR-I SDRAM Modules |

| HYS72D64020GU-7-A | 制造商:未知厂家 制造商全称:未知厂家 功能描述:?512MB (64Mx72) PC2100 2-bank? |

| HYS72D64020GU-7-B | 制造商:INFINEON 制造商全称:Infineon Technologies AG 功能描述:184-Pin Unbuffered Dual-In-Line Memory Modules |

| HYS72D64020GU-7F-B | 制造商:INFINEON 制造商全称:Infineon Technologies AG 功能描述:184-Pin Unbuffered Dual-In-Line Memory Modules |

发布紧急采购,3分钟左右您将得到回复。