- 您现在的位置:买卖IC网 > PDF目录65529 > ICS507M-02ILFT 185 MHz, OTHER CLOCK GENERATOR, PDSO16 PDF资料下载

参数资料

| 型号: | ICS507M-02ILFT |

| 元件分类: | 时钟产生/分配 |

| 英文描述: | 185 MHz, OTHER CLOCK GENERATOR, PDSO16 |

| 封装: | 0.150 INCH, SOIC-16 |

| 文件页数: | 3/5页 |

| 文件大小: | 72K |

| 代理商: | ICS507M-02ILFT |

ICS507-01/02

PECL Clock Synthesizer

MDS 507 G

3

Revision 022002

Integrated Circuit Systems, Inc. 525 Race Street San Jose CA 95126 (408)295-9800tel www.icst.com

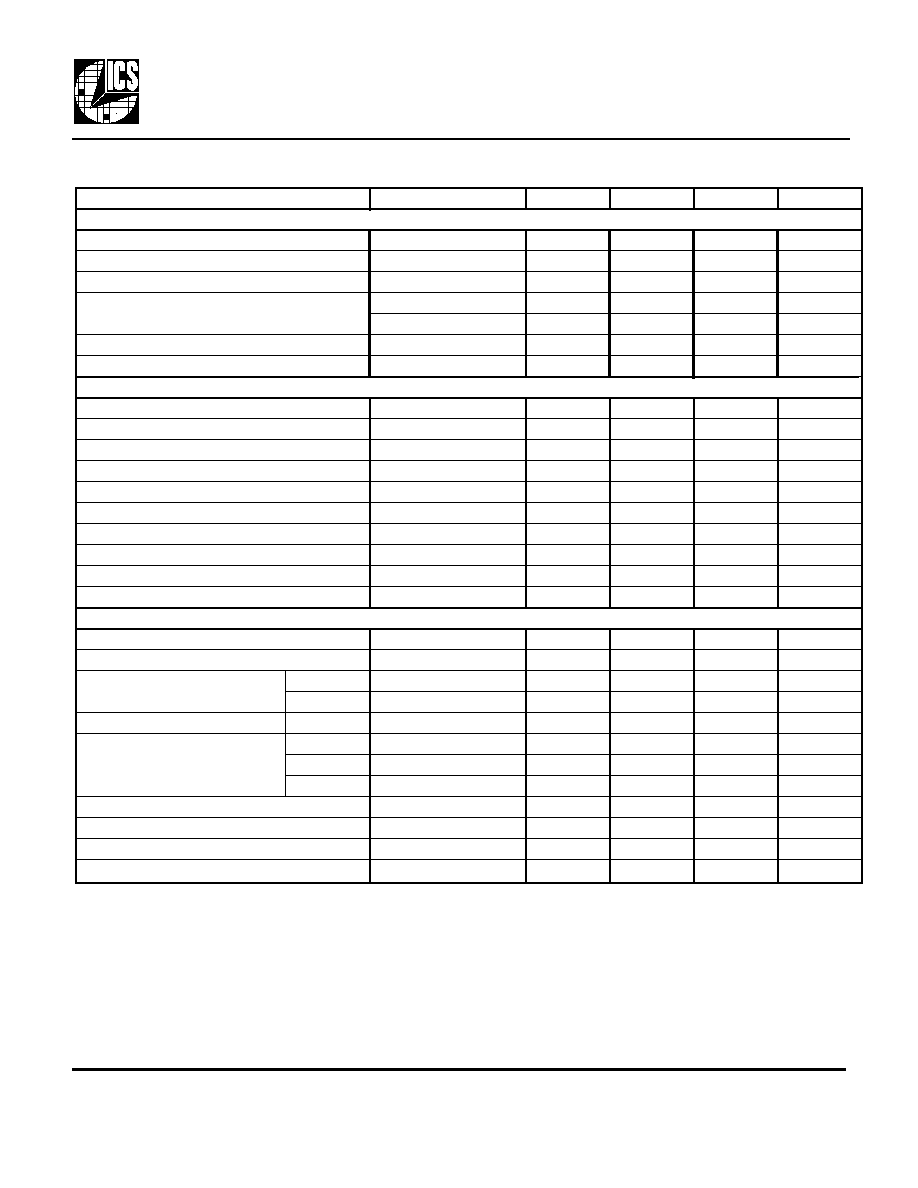

Parameter

Conditions

Minimum

Typical

Maximum

Units

ABSOLUTE MAXIMUM RATINGS (stresses beyond these can permanently damage the device)

Supply Voltage, VDD

Referenced to GND

7

V

Inputs

Referenced to GND

-0.5

VDD+0.5

V

Clock Output

Referenced to GND

-0.5

VDD+0.5

V

Ambient Operating Temperature

ICS507M-0x

0

70

°C

ICS507M-0xI

-40

85

°C

Soldering Temperature

Max of 20 seconds

260

°C

Storage temperature

-65

150

°C

DC CHARACTERISTICS (VDD = 5.0 V unless otherwise noted)

Operating Voltage, VDD

3.0

5.5

V

Input High Voltage, VIH

ICLK only

VDD/2 + 1

VDD/2

V

Input Low Voltage, VIL

ICLK only

VDD/2

VDD/2-1

V

Input High Voltage, VIH

S0, S1

VDD-0.5

V

Input Low Voltage, VIL

S0, S1

0.5

V

Output High Voltage, VOH

Note 2

VDD-1.2

V

Output Low Voltage, VOL

Note 2

VDD-2.0

V

IDD Operating Supply Current, note 3

No Load, 155.52MHz

63

mA

Internal Crystal Capacitance, X1 and X2

Pins 1, 8

26

pF

Input Capacitance

S0, S1

5

pF

AC CHARACTERISTICS (VDD = 3.3, 5.0 V unless otherwise noted)

Input Crystal Frequency

5

27

MHz

Input Clock Frequency

5

52

MHz

Output Frequency, ICS507-01

0 to 70°C VDD = 5.0 V

10

200

MHz

0 to 70°C VDD = 3.3 V

10

156

MHz

Output Frequency, ICS507-01I

-40 to 85°C VDD = 3.3 V or 5.0 V

10

125

MHz

Output Frequency, ICS507-02I

0 to 70°C VDD = 5.0 V

125

200

MHz

Note 5

0 to 70°C VDD = 3.3 V

125

200

MHz

-40 to 85°C VDD = 3.3 V or 5.0 V

125

185

MHz

Output Clock Duty Cycle

48

52

%

PLL Bandwidth

10

kHz

Absolute Clock Period Jitter

Deviation from mean

±75

ps

One Sigma Clock Period Jitter

20

ps

Electrical Specifications

Notes: 1) All typical values are at 5.0 V and 25°C unless otherwise noted.

2) VOH and VOL can be set by the external resistor values on the PECL outputs.

3) IDD includes the current through the external resistors, which can be modified.

4) The phase relationship between input and output can change at power up. For a fixed phase

relationship, see one of the ICS zero delay buffers.

5) Except S1=0, S0=0 setting (This setting specific to 16 MHz in, 155.52 MHz out).

相关PDF资料 |

PDF描述 |

|---|---|

| ICS507M-02IT | 185 MHz, OTHER CLOCK GENERATOR, PDSO16 |

| ICS507M-02IT | 185 MHz, OTHER CLOCK GENERATOR, PDSO16 |

| ICS511MI | 160 MHz, OTHER CLOCK GENERATOR, PDSO8 |

| ICS511MILF | 160 MHz, OTHER CLOCK GENERATOR, PDSO8 |

| ICS512MLFT | 200 MHz, OTHER CLOCK GENERATOR, PDSO8 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ICS507M-02IT | 制造商:ICS 制造商全称:ICS 功能描述:PECL Clock Synthesizer |

| ICS507-XX | 制造商:ICS 制造商全称:ICS 功能描述:PECL Clock Synthesizer |

| ICS508 | 制造商:ICS 制造商全称:ICS 功能描述:PECL to CMOS Converter |

| ICS508-DPK | 制造商:ICS 制造商全称:ICS 功能描述:PECL to CMOS Converter |

| ICS508-DWF | 制造商:ICS 制造商全称:ICS 功能描述:PECL to CMOS Converter |

发布紧急采购,3分钟左右您将得到回复。