- 您现在的位置:买卖IC网 > PDF目录67110 > ICS672M-01T (INTEGRATED DEVICE TECHNOLOGY INC) 672 SERIES, PLL BASED CLOCK DRIVER, 4 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO16 PDF资料下载

参数资料

| 型号: | ICS672M-01T |

| 厂商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分类: | 时钟及定时 |

| 英文描述: | 672 SERIES, PLL BASED CLOCK DRIVER, 4 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO16 |

| 封装: | 0.150 INCH, SOIC-16 |

| 文件页数: | 3/8页 |

| 文件大小: | 190K |

| 代理商: | ICS672M-01T |

ICS672-01/02

QUADRACLOCK QUADRATURE DELAY BUFFER

ZERO DELAY BUFFER

IDT / ICS QUADRACLOCK QUADRATURE DELAY BUFFER

3

ICS672-01/02 REV G 092506

External Components

The ICS672-01/02 requires a minimum number of external components for proper operation. Decoupling capacitors

of 0.01F should be connected between VDD and GND on pins 11 and 12, and VDD and GND on pins 13 and 12,

and VDDIO and GND on pins 5 and 6, as close to the device as possible. A series termination resistor of 33

may

be used close to each clock output pin to reduce reflections.

Operation and Applications

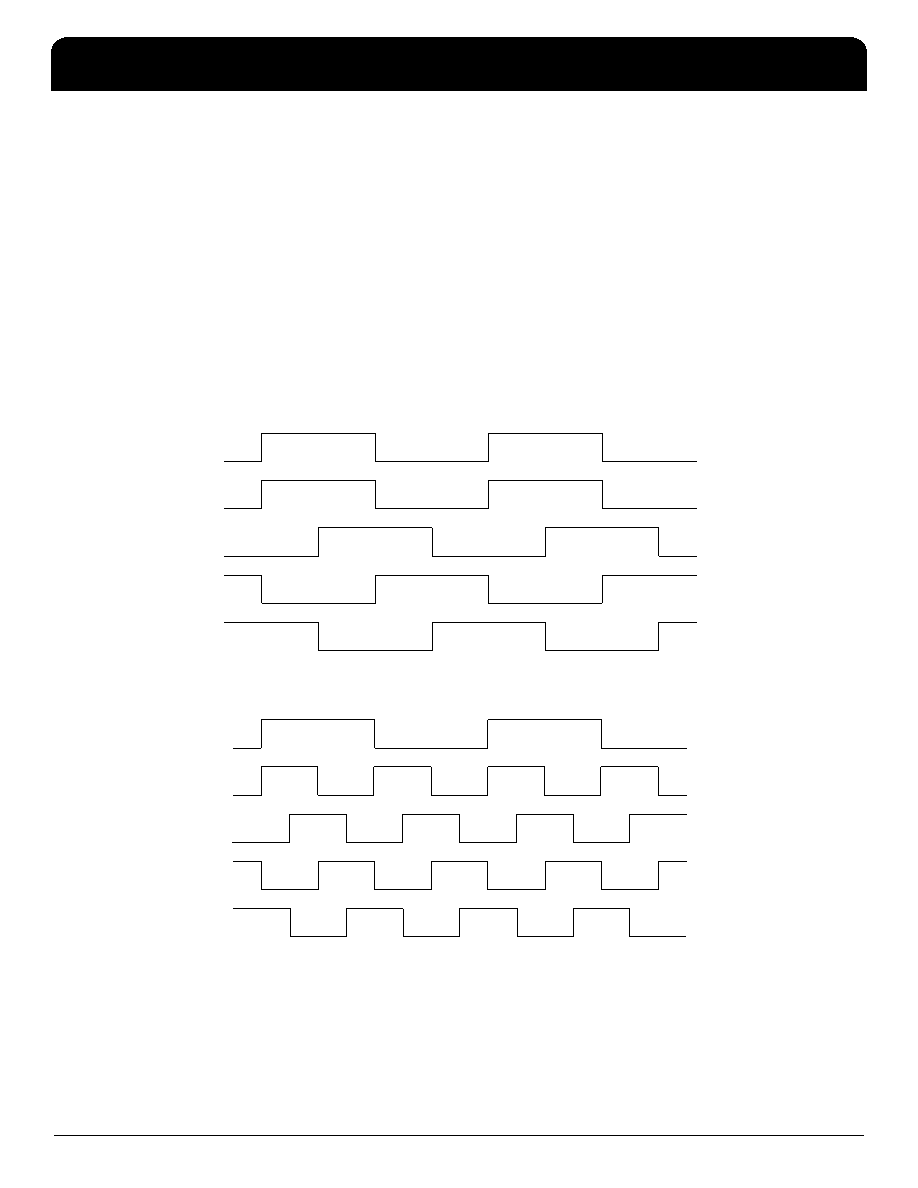

The ICS672-01/02 each provide a total of five output clocks with multiple phase shifts relative to the input clock

(ICLK). Phase shifts of 0° (CLK0), 90° (CLK90), 180° (CLK180), and 270° (CLK270) are provided, plus one

feedback clock (FBCLK). All output clocks will be a multiple of the input clock, as determined by the table on page

2. Refer to the illustrations in Figure 1 and Figure 2.

FBCLK is connected to the feedback input (FBIN) to provide a zero delay through the ICS672-01/02. FBCLK has a

0° phase shift from ICLK.

ICLK

CLK0,

FBCLK

CLK90

CLK180

CLK270

Figure 1. Phase alignment of input and output clocks (x1 multiplier)

ICLK

CLK0,

FBCLK

CLK90

CLK180

CLK270

Figure 2. Phase alignment of input and output clocks (x2 multiplier)

相关PDF资料 |

PDF描述 |

|---|---|

| ICS672MI-02LF | 672 SERIES, PLL BASED CLOCK DRIVER, 4 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO16 |

| ICS672M-02LFT | 672 SERIES, PLL BASED CLOCK DRIVER, 4 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO16 |

| ICS672M-02 | 672 SERIES, PLL BASED CLOCK DRIVER, 4 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO16 |

| ICS672M-01LFT | 672 SERIES, PLL BASED CLOCK DRIVER, 4 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO16 |

| ICS672MI-02LFT | 672 SERIES, PLL BASED CLOCK DRIVER, 4 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO16 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ICS672M-02 | 功能描述:IC DELAY BUFFER QUADRACLK 16SOIC RoHS:否 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:- 产品变化通告:Product Discontinuation 04/May/2011 标准包装:96 系列:- 类型:时钟倍频器,零延迟缓冲器 PLL:带旁路 输入:LVTTL 输出:LVTTL 电路数:1 比率 - 输入:输出:1:8 差分 - 输入:输出:无/无 频率 - 最大:133.3MHz 除法器/乘法器:是/无 电源电压:3 V ~ 3.6 V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:16-TSSOP(0.173",4.40mm 宽) 供应商设备封装:16-TSSOP 包装:管件 其它名称:23S08-5HPGG |

| ICS672M-02I | 功能描述:IC DELAY BUFFER QUADRACLK 16SOIC RoHS:否 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:- 产品变化通告:Product Discontinuation 04/May/2011 标准包装:96 系列:- 类型:时钟倍频器,零延迟缓冲器 PLL:带旁路 输入:LVTTL 输出:LVTTL 电路数:1 比率 - 输入:输出:1:8 差分 - 输入:输出:无/无 频率 - 最大:133.3MHz 除法器/乘法器:是/无 电源电压:3 V ~ 3.6 V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:16-TSSOP(0.173",4.40mm 宽) 供应商设备封装:16-TSSOP 包装:管件 其它名称:23S08-5HPGG |

| ICS672M-02ILF | 功能描述:IC DELAY BUFFER QUADRACLK 16SOIC RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:- 标准包装:1,000 系列:- 类型:时钟/频率合成器,扇出分配 PLL:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 除法器/乘法器:- 电源电压:- 工作温度:- 安装类型:表面贴装 封装/外壳:56-VFQFN 裸露焊盘 供应商设备封装:56-VFQFP-EP(8x8) 包装:带卷 (TR) 其它名称:844S012AKI-01LFT |

| ICS672M-02ILFT | 功能描述:IC DELAY BUFFER QUADRACLK 16SOIC RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:- 标准包装:1,000 系列:- 类型:时钟/频率合成器,扇出分配 PLL:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 除法器/乘法器:- 电源电压:- 工作温度:- 安装类型:表面贴装 封装/外壳:56-VFQFN 裸露焊盘 供应商设备封装:56-VFQFP-EP(8x8) 包装:带卷 (TR) 其它名称:844S012AKI-01LFT |

| ICS672M-02IT | 功能描述:IC DELAY BUFFER QUADRACLK 16SOIC RoHS:否 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:- 产品变化通告:Product Discontinuation 04/May/2011 标准包装:96 系列:- 类型:时钟倍频器,零延迟缓冲器 PLL:带旁路 输入:LVTTL 输出:LVTTL 电路数:1 比率 - 输入:输出:1:8 差分 - 输入:输出:无/无 频率 - 最大:133.3MHz 除法器/乘法器:是/无 电源电压:3 V ~ 3.6 V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:16-TSSOP(0.173",4.40mm 宽) 供应商设备封装:16-TSSOP 包装:管件 其它名称:23S08-5HPGG |

发布紧急采购,3分钟左右您将得到回复。