- 您现在的位置:买卖IC网 > PDF目录67690 > ICS8430S07AKILFT (INTEGRATED DEVICE TECHNOLOGY INC) 133.333 MHz, OTHER CLOCK GENERATOR, QCC32 PDF资料下载

参数资料

| 型号: | ICS8430S07AKILFT |

| 厂商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分类: | 时钟产生/分配 |

| 英文描述: | 133.333 MHz, OTHER CLOCK GENERATOR, QCC32 |

| 封装: | 5 X 5 MM, 0.925 MM HEIGHT, ROHS COMPLIANT, MO-220VHHD-2/-4, VFQFN-32 |

| 文件页数: | 17/23页 |

| 文件大小: | 1792K |

| 代理商: | ICS8430S07AKILFT |

ICS8430S07I

CLOCK GENERATOR FOR CAVIUM PROCESSORS

PRELIMINARY

IDT / ICS CLOCK GENERATOR

3

ICS8430S07AKI REV. A DECEMBER 4, 2007

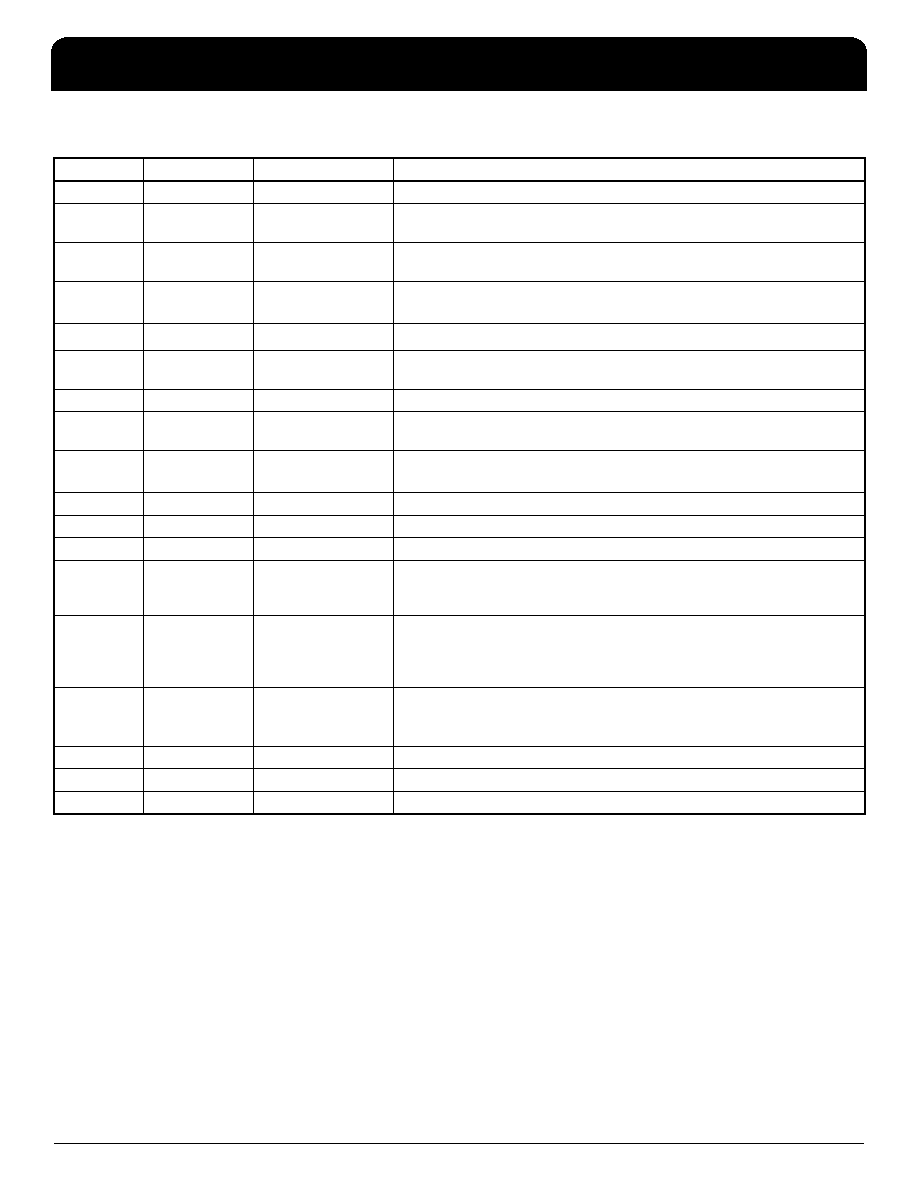

Table 1. Pin Descriptions

NOTE: Pullup and Pulldown refer to internal input resistors. See Table 2, Pin Characteristics, for typical values.

Number

Name

Type

Description

1, 15

VDD

Power

Core supply pins.

2

nPLL_SEL

Input

Pulldown

PLL bypass. When LOW, selects PLL (PLL Enable). When HIGH, deselects

the reference clock (PLL Bypass). LVCMOS/LVTTL interface levels.

3, 4

XTAL_IN,

XTAL_OUT

Input

Parallel resonant crystal interface. XTAL_OUT is the output, XTAL_IN is the

input.

5

nXTAL_SEL

Input

Pulldown

Selects XTAL inputs when LOW. Selects differential clock (CLK, nCLK) input

when HIGH. LVCMOS/LVTTL interface levels.

6

CLK

Input

Pulldown

Non-inverting differential clock input.

7

nCLK

Input

Pullup/

Pulldown

Inverting differential clock input. Internal resistor bias to VDD/2.

8, 20, 21, 27

GND

Power

Power supply ground.

9, 10

PCI_SEL1,

PCI_SEL0

Input

Pulldown

Selects the PCI/PCI-X reference clock output frequency. See Table 3C.

LVCMOS/LVTTL interface levels.

11, 12

DDR_SEL1,

DDR_SEL0

Input

Pulldown

Selects the DDR reference clock output frequency. See Table 3B.

LVCMOS/LVTTL interface levels.

13, 14

nQA, QA

Output

Differential output pair. LVPECL interface levels.

16

VDDA

Power

Analog supply pin.

17

VDDO_B

Power

Bank B output supply pin. 3.3 V or 2.5V supply.

18, 23, 26,

29,

30, 31

QB, QC, QD,

QREF2,

QREF1, QREF0

Output

Single-ended outputs. LVCMOS/LVTTL interface levels.

19

MR/nOE_REF

Input

Pulldown

Active HIGH Master Reset. Active LOW output enable. When logic HIGH, the

internal dividers are reset and the QREF[2:0] outputs are in high impedance

(HI-Z). When logic LOW, the internal dividers and the outputs are enabled.

LVCMOS/ LVTTL interface levels.

22

CORE_SEL

Input

Pulldown

Selects the processor core clock output frequency. The output frequency is

50MHz when LOW, and 33.333MHz when HIGH. See Table 3A.

LVCMOS/LVTTL interface levels.

24

VDDO_C

Power

Bank C output supply pin. 3.3 V or 2.5V supply.

25

VDDO_D

Power

Bank D output supply pin. 3.3 V or 2.5V supply.

28, 32

VDDO_REF

Power

REF bank output supply pins. 3.3 V or 2.5V supply.

相关PDF资料 |

PDF描述 |

|---|---|

| ICS843101AG-312 | 312.5 MHz, OTHER CLOCK GENERATOR, PDSO16 |

| ICS843101AGI-312T | 312.5 MHz, OTHER CLOCK GENERATOR, PDSO16 |

| ICS843101AGI-312LFT | 312.5 MHz, OTHER CLOCK GENERATOR, PDSO16 |

| ICS843101AGI-312LF | 312.5 MHz, OTHER CLOCK GENERATOR, PDSO16 |

| ICS843101IAG-100LFT | 100 MHz, OTHER CLOCK GENERATOR, PDSO16 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ICS8430S07I | 制造商:IDT 制造商全称:Integrated Device Technology 功能描述:Clock Generator for Cavium Processors |

| ICS8430S10AYILF | 功能描述:IC CLK GENERATOR PLL 48TQFP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:- 标准包装:1,500 系列:- 类型:时钟缓冲器/驱动器 PLL:是 主要目的:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 电源电压:3.3V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:28-SSOP(0.209",5.30mm 宽) 供应商设备封装:28-SSOP 包装:带卷 (TR) 其它名称:93786AFT |

| ICS8430S10AYILFT | 功能描述:IC CLK GENERATOR PLL 48TQFP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:- 标准包装:1,500 系列:- 类型:时钟缓冲器/驱动器 PLL:是 主要目的:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 电源电压:3.3V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:28-SSOP(0.209",5.30mm 宽) 供应商设备封装:28-SSOP 包装:带卷 (TR) 其它名称:93786AFT |

| ICS8430S10BYI-02LF | 功能描述:IC CLK GENERATOR PLL 48TQFP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:- 标准包装:1,500 系列:- 类型:时钟缓冲器/驱动器 PLL:是 主要目的:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 电源电压:3.3V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:28-SSOP(0.209",5.30mm 宽) 供应商设备封装:28-SSOP 包装:带卷 (TR) 其它名称:93786AFT |

| ICS8430S10BYI-02LFT | 功能描述:IC CLK GENERATOR PLL 48TQFP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:- 标准包装:1,500 系列:- 类型:时钟缓冲器/驱动器 PLL:是 主要目的:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 电源电压:3.3V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:28-SSOP(0.209",5.30mm 宽) 供应商设备封装:28-SSOP 包装:带卷 (TR) 其它名称:93786AFT |

发布紧急采购,3分钟左右您将得到回复。