- 您现在的位置:买卖IC网 > PDF目录1998 > ICS844S42BKILF (IDT, Integrated Device Technology Inc)IC SYNTHESIZER RF FREQ 56-VFQFPN PDF资料下载

参数资料

| 型号: | ICS844S42BKILF |

| 厂商: | IDT, Integrated Device Technology Inc |

| 文件页数: | 10/27页 |

| 文件大小: | 0K |

| 描述: | IC SYNTHESIZER RF FREQ 56-VFQFPN |

| 标准包装: | 260 |

| 系列: | HiPerClockS™ |

| 类型: | 频率合成器 |

| PLL: | 带旁路 |

| 输入: | LVCMOS,LVTTL,晶体 |

| 输出: | LVDS,LVPECL |

| 电路数: | 1 |

| 比率 - 输入:输出: | 2:2 |

| 差分 - 输入:输出: | 无/是 |

| 频率 - 最大: | 2.592GHz |

| 除法器/乘法器: | 是/无 |

| 电源电压: | 3.135 V ~ 3.465 V |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 56-VFQFN 裸露焊盘 |

| 供应商设备封装: | 56-VFQFP-EP(8x8) |

| 包装: | 托盘 |

| 其它名称: | 844S42BKILF |

第1页第2页第3页第4页第5页第6页第7页第8页第9页当前第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页

ICS844S42BKI REVISION A FEBRUARY 21, 2012

18

2012 Integrated Device Technology, Inc.

ICS844S42I Data Sheet

DUAL OUTPUT RF FREQUENCY SYNTHESIZER

3.3V LVDS Driver Termination

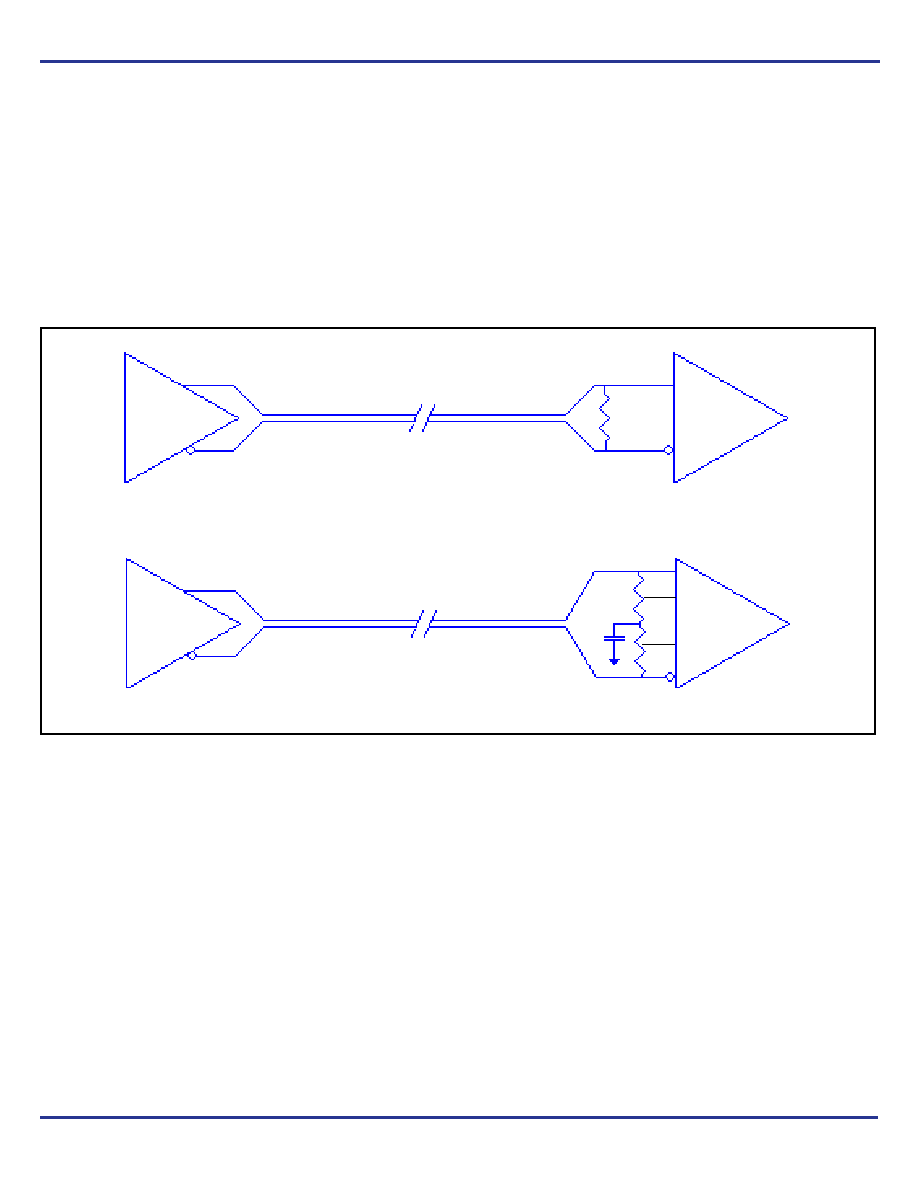

For a general LVDS interface, the recommended value for the

termination impedance (ZT) is between 90 and 132. The actual

value should be selected to match the differential impedance (Z0) of

your transmission line. A typical point-to-point LVDS design uses a

100

parallel resistor at the receiver and a 100 differential

transmission-line environment. In order to avoid any

transmission-line reflection issues, the components should be

surface mounted and must be placed as close to the receiver as

possible. IDT offers a full line of LVDS compliant devices with two

types of output structures: current source and voltage source. The

standard termination schematic as shown in Figure 5A can be used

with either type of output structure. Figure 5B, which can also be used

with both output types, is an optional termination with center tap

capacitance to help filter common mode noise. The capacitor value

should be approximately 50pF. If using a non-standard termination, it

is recommended to contact IDT and confirm if the output structure is

current source or voltage source type. In addition, since these

outputs are LVDS compatible, the input receiver’s amplitude and

common-mode input range should be verified for compatibility with

the output.

Figure 5. Typical LVDS Driver Termination

LVDS

Driver

LVDS

Driver

LVDS

Receiver

LVDS

Receiver

ZT

C

ZO ZT

ZT

2

ZT

2

Figure 5A. Standard Termination

Figure 5B. Optional Termination

相关PDF资料 |

PDF描述 |

|---|---|

| ICS86004BG-01LF | IC CLK BUFFER ZD 1:4 16-TSSOP |

| ICS8634BY-01LFT | IC BUFFER ZD 1-5 LVPECL 32-LQFP |

| ICS8701AY-01LF | IC CLK GEN POLARITY CTRL 48-LQFP |

| ICS8701CYLF | IC CLK GENERATOR /1 /2 48-LQFP |

| ICS870931ARI-01LF | IC CLK GENERATOR LVCMOS 20QSOP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ICS844S42BKILFT | 功能描述:IC SYNTHESIZER RF FREQ 56-VFQFPN RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:HiPerClockS™ 标准包装:1,000 系列:- 类型:时钟/频率合成器,扇出分配 PLL:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 除法器/乘法器:- 电源电压:- 工作温度:- 安装类型:表面贴装 封装/外壳:56-VFQFN 裸露焊盘 供应商设备封装:56-VFQFP-EP(8x8) 包装:带卷 (TR) 其它名称:844S012AKI-01LFT |

| ICS845252AKILF | 功能描述:IC CLK GENERATOR CML 32VFQFN RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:HiPerClockS™, FemtoClock™ 标准包装:1,000 系列:- 类型:时钟/频率合成器,扇出分配 PLL:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 除法器/乘法器:- 电源电压:- 工作温度:- 安装类型:表面贴装 封装/外壳:56-VFQFN 裸露焊盘 供应商设备封装:56-VFQFP-EP(8x8) 包装:带卷 (TR) 其它名称:844S012AKI-01LFT |

| ICS845252AKILFT | 功能描述:IC CLK GENERATOR CML 32VFQFN RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:HiPerClockS™, FemtoClock™ 标准包装:1,000 系列:- 类型:时钟/频率合成器,扇出分配 PLL:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 除法器/乘法器:- 电源电压:- 工作温度:- 安装类型:表面贴装 封装/外壳:56-VFQFN 裸露焊盘 供应商设备封装:56-VFQFP-EP(8x8) 包装:带卷 (TR) 其它名称:844S012AKI-01LFT |

| ICS845254AKILF | 功能描述:IC CLK GENERATOR CML 32VFQFN RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:HiPerClockS™, FemtoClock™ 标准包装:1,000 系列:- 类型:时钟/频率合成器,扇出分配 PLL:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 除法器/乘法器:- 电源电压:- 工作温度:- 安装类型:表面贴装 封装/外壳:56-VFQFN 裸露焊盘 供应商设备封装:56-VFQFP-EP(8x8) 包装:带卷 (TR) 其它名称:844S012AKI-01LFT |

| ICS845254AKILFT | 功能描述:IC CLK GENERATOR CML 32VFQFN RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:HiPerClockS™, FemtoClock™ 标准包装:1,000 系列:- 类型:时钟/频率合成器,扇出分配 PLL:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 除法器/乘法器:- 电源电压:- 工作温度:- 安装类型:表面贴装 封装/外壳:56-VFQFN 裸露焊盘 供应商设备封装:56-VFQFP-EP(8x8) 包装:带卷 (TR) 其它名称:844S012AKI-01LFT |

发布紧急采购,3分钟左右您将得到回复。