- 您现在的位置:买卖IC网 > PDF目录1998 > ICS870931ARI-01LF (IDT, Integrated Device Technology Inc)IC CLK GENERATOR LVCMOS 20QSOP PDF资料下载

参数资料

| 型号: | ICS870931ARI-01LF |

| 厂商: | IDT, Integrated Device Technology Inc |

| 文件页数: | 7/13页 |

| 文件大小: | 0K |

| 描述: | IC CLK GENERATOR LVCMOS 20QSOP |

| 标准包装: | 55 |

| 系列: | HiPerClockS™ |

| 类型: | * |

| PLL: | 带旁路 |

| 输入: | LVCMOS,LVTTL |

| 输出: | LVCMOS,LVTTL |

| 电路数: | 1 |

| 比率 - 输入:输出: | 1:6 |

| 差分 - 输入:输出: | 无/无 |

| 频率 - 最大: | 80MHz |

| 除法器/乘法器: | 是/是 |

| 电源电压: | 3 V ~ 3.6 V |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 20-SSOP(0.154",3.90mm 宽) |

| 供应商设备封装: | 20-QSOP |

| 包装: | 管件 |

ICS870931ARI-01 REVISION A JUNE 11, 2009

3

2009 Integrated Device Technology, Inc.

ICS870931I-01 Data Sheet

LVCMOS CLOCK GENERATOR

Device Configuration

The ICS870931I-01 requires a connection to one of the clock outputs

to the FEEDBACK input to close the PLL feedback path. The

selection of the output (output divider) for PLL feedback will impact

the device configuration and input to output frequency ratio and

frequency ranges. See Table 3D for details.

Function Tables

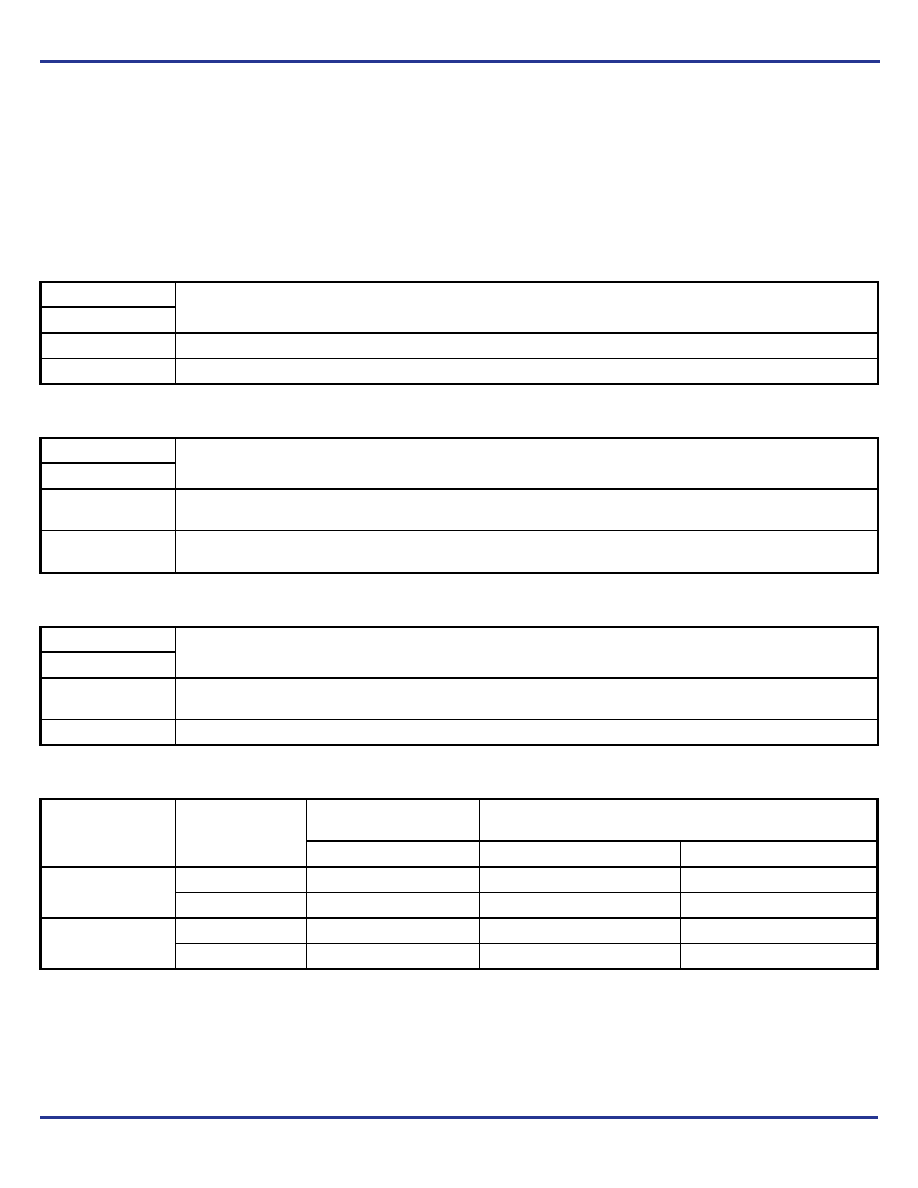

Table 3A. OE/nRST Mode Configuration Table

Table 3B. FREQ_SEL Mode Configuration Table

Table 3C. PLL_EN Mode Configuration Table

Table 3D. Frequency Configuration Table

Input

Operation

OE/nRST

0

Device is reset and the outputs Q0:Q4 and Q/2 are in high-impedance state. This control is asynchronous.

1

Outputs are enabled.

Input

Operation

FREQ_SEL

0

The VCO output is frequency-divided by 2. This setting allows for a lower input frequency range.

See also table 3D for available frequency ranges.

1

The VCO output is frequency-divided by 1. This setting allows for a higher input frequency range.

See also table 3D for available frequency ranges.

Input

Operation

PLL_EN

0

The PLL is bypassed. The input reference clock is routed to the output dividers for low-frequency board test purpose.

The PLL-related AC specifications do not apply in PLL bypass mode.

1

The PLL is enabled and locks to the input reference signal.

Outputs Used for

PLL Feedback

FREQ_SEL

Input Frequency Range

(MHz)

Output Frequency Range (MHz) and

Output-to-Input Frequency Multiplication Factor

SYNC

Q[0:4]

Q/2

Q0, Q1, Q2,

Q3 or Q4

0

5 - 40

5 - 40 (1x)

2.5 - 20 (0.5x)

1

10 - 80

10 - 80 (1x)

5 - 40 (0.5x)

Q/2

0

2.5 - 20

5 - 40 (2x)

2.5 - 20 (1x)

1

5 - 40

10 - 80 (2x)

5 - 40 (1x)

相关PDF资料 |

PDF描述 |

|---|---|

| ICS87158AFLF | IC CLOCK GEN 1-6 HCSL 48-SSOP |

| ICS87159AGLFT | IC CLOCK GEN 1-8 LVCMOS 56-TSSOP |

| ICS8731CY-01LF | IC CLOCK ULT/ZD BUFFER 48-LQFP |

| ICS8732AY-01LF | IC CLK GEN LV 3.3V LVPECL 52LQFP |

| ICS87332AMI-01LFT | IC CLK GEN ECL/LVPECL 8-SOIC |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ICS870931ARI-01LFT | 功能描述:IC CLK GENERATOR LVCMOS 20QSOP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:HiPerClockS™ 标准包装:1,000 系列:- 类型:时钟/频率合成器,扇出分配 PLL:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 除法器/乘法器:- 电源电压:- 工作温度:- 安装类型:表面贴装 封装/外壳:56-VFQFN 裸露焊盘 供应商设备封装:56-VFQFP-EP(8x8) 包装:带卷 (TR) 其它名称:844S012AKI-01LFT |

| ICS870931ARI-01T | 制造商:Integrated Device Technology Inc 功能描述:IC CLK GENERATOR LVCMOS 20QSOP |

| ICS870S204BGLF | 功能描述:IC CLK BUFF DIVIDER 2:4 20-TSSOP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟缓冲器,驱动器 系列:- 标准包装:74 系列:- 类型:扇出缓冲器(分配) 电路数:1 比率 - 输入:输出:1:10 差分 - 输入:输出:是/是 输入:HCSL, LVCMOS, LVDS, LVPECL, LVTTL 输出:HCSL,LVDS 频率 - 最大:400MHz 电源电压:3 V ~ 3.6 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:32-VFQFN 裸露焊盘 供应商设备封装:32-QFN(5x5) 包装:管件 |

| ICS870S204BGLFT | 功能描述:IC CLK BUFF DIVIDER 2:4 20-TSSOP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟缓冲器,驱动器 系列:- 标准包装:74 系列:- 类型:扇出缓冲器(分配) 电路数:1 比率 - 输入:输出:1:10 差分 - 输入:输出:是/是 输入:HCSL, LVCMOS, LVDS, LVPECL, LVTTL 输出:HCSL,LVDS 频率 - 最大:400MHz 电源电压:3 V ~ 3.6 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:32-VFQFN 裸露焊盘 供应商设备封装:32-QFN(5x5) 包装:管件 |

| ICS870S208AKLF | 功能描述:IC CLK BUFF DIVIDER 2:8 32VFQFPN RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟缓冲器,驱动器 系列:- 标准包装:74 系列:- 类型:扇出缓冲器(分配) 电路数:1 比率 - 输入:输出:1:10 差分 - 输入:输出:是/是 输入:HCSL, LVCMOS, LVDS, LVPECL, LVTTL 输出:HCSL,LVDS 频率 - 最大:400MHz 电源电压:3 V ~ 3.6 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:32-VFQFN 裸露焊盘 供应商设备封装:32-QFN(5x5) 包装:管件 |

发布紧急采购,3分钟左右您将得到回复。