- 您现在的位置:买卖IC网 > PDF目录65534 > ICS9112YM-17-T PLL BASED CLOCK DRIVER, 8 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO16 PDF资料下载

参数资料

| 型号: | ICS9112YM-17-T |

| 元件分类: | 时钟及定时 |

| 英文描述: | PLL BASED CLOCK DRIVER, 8 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO16 |

| 封装: | 0.150 INCH, MS-012, SOIC-16 |

| 文件页数: | 6/8页 |

| 文件大小: | 108K |

| 代理商: | ICS9112YM-17-T |

6

ICS9112-17

0051J—02/05/04

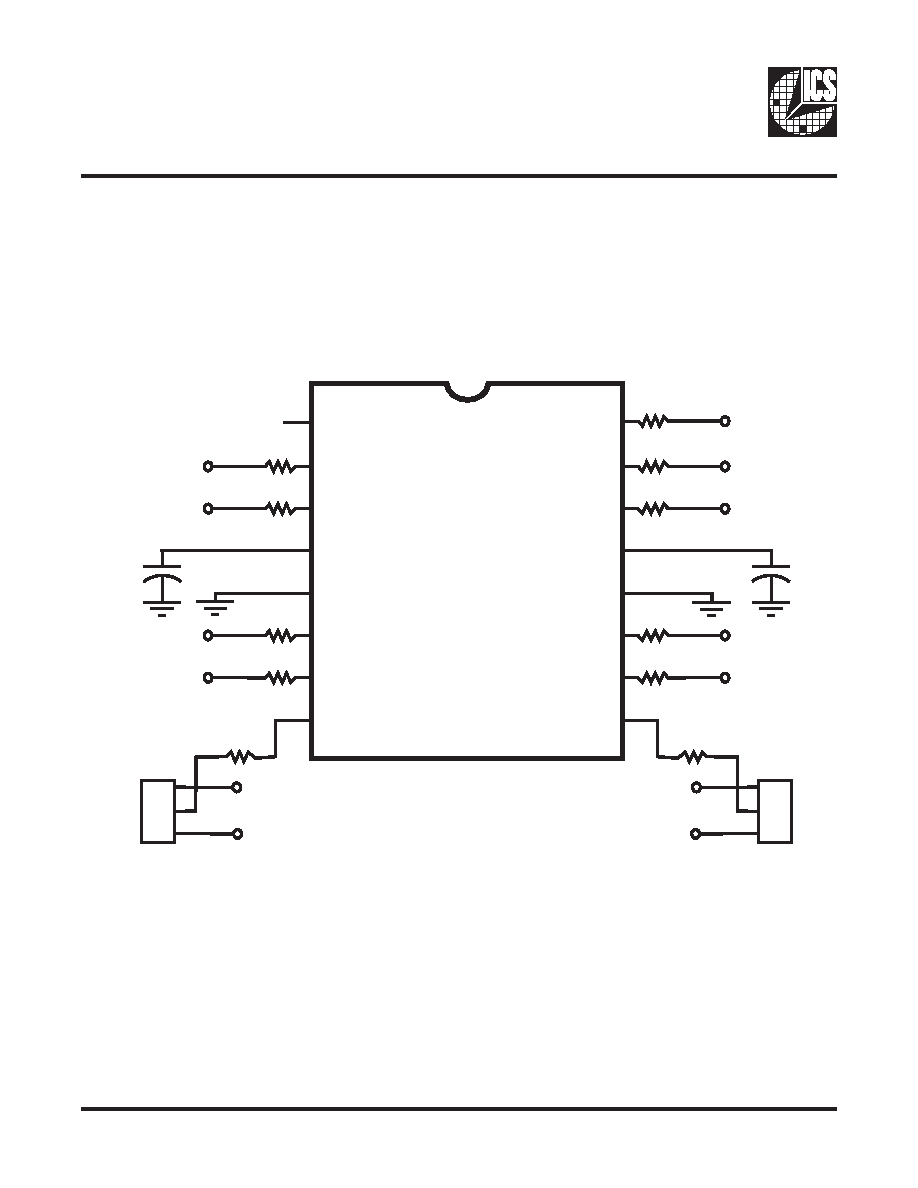

Application Suggestion:

ICS9112-17 is a mixed analog/digital product. The analog portion of the PLL is very sensitive to any random noise

generated by charging or discharging of internal or external capacitor on the power supply pins. This type of noise will

cause excess jitter to the outputs of ICS9112-17. Below is a recommended lay out to alleviate any addition noise. For

additional information on FT. layout, please refer to our AN07.The 0.1 uF capacitors should be connected as close as

possible to power pins (4 & 13). An Isolated power plane with a 2.2 uF capacitor to ground will enhance the power line

stability.

33

10K

0.1F

VDD

GND

33

10K

0.1F

VDD

GND

1

2

3

4

5

6

7

8

16

15

14

13

12

11

10

9

REF

CLKA1

CLKA2

VDD

GND

CLKB1

CLKB2

FS2

CLKOUT

CLKA4

CLKA3

VDD

GND

CLKB4

CLKB3

FS1

相关PDF资料 |

PDF描述 |

|---|---|

| ICS9112YF-17-T | PLL BASED CLOCK DRIVER, 8 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO16 |

| ICS9112YM-26LF-T | LOW SKEW CLOCK DRIVER, 4 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO8 |

| ICS9112YM-26LFT | 9112 SERIES, LOW SKEW CLOCK DRIVER, 4 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO8 |

| ICS9112YM-28LF-T | 9112 SERIES, LOW SKEW CLOCK DRIVER, 5 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO8 |

| ICS9112YM-28LF-T | 9112 SERIES, LOW SKEW CLOCK DRIVER, 5 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO8 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ICS9112YM-27-T | 制造商:ICS 制造商全称:ICS 功能描述:Low Skew PCI / PCI-X Buffer |

| ICS9112YM-28LF-T | 制造商:ICS 制造商全称:ICS 功能描述:Low Skew Output Buffer |

| ICS9117-01 | 制造商:ICS 制造商全称:ICS 功能描述:Frequency Generator for Modem Systems |

| ICS9117M-01 | 制造商:ICS 制造商全称:ICS 功能描述:Frequency Generator for Modem Systems |

| ICS9117M02 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Peripheral IC |

发布紧急采购,3分钟左右您将得到回复。