- 您现在的位置:买卖IC网 > PDF目录362809 > ICS952623YFT Programmable Timing Control Hub for Next Gen P4 processor PDF资料下载

参数资料

| 型号: | ICS952623YFT |

| 英文描述: | Programmable Timing Control Hub for Next Gen P4 processor |

| 中文描述: | 可编程定时控制中心,为下一代P4处理器 |

| 文件页数: | 18/27页 |

| 文件大小: | 329K |

| 代理商: | ICS952623YFT |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页当前第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页

18

Integrated

Circuit

Systems, Inc.

ICS952623

Advance Information

0758—02/08/05

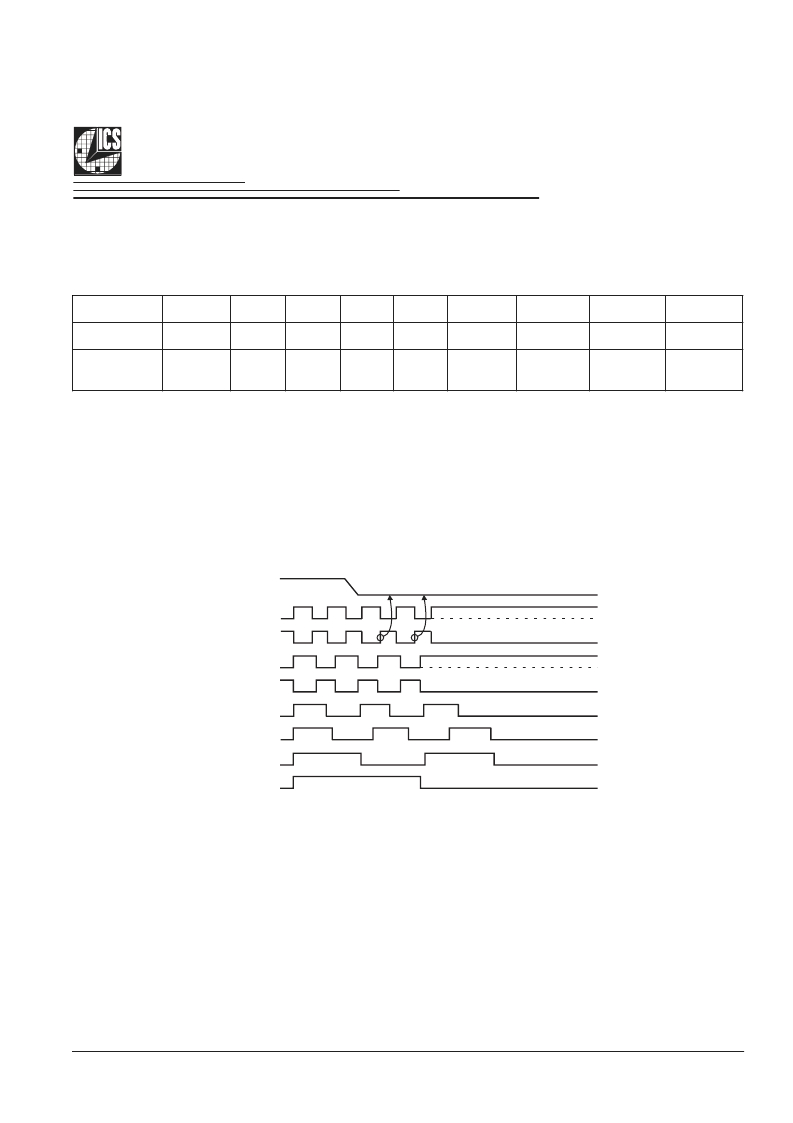

PD# is an asynchronous active low input used to shut off all clocks cleanly prior to clock power.

When PD# is asserted low all clocks will be driven low before turning off the VCO. In PD# de-assertion all clocks will start

without glitches.

PD#, Power Down

#

N

W

D

R

W

P

U

P

C

#

U

P

C

C

R

S

#

C

R

S

6

6

V

3

I

C

P

/

C

P

T

O

D

/

B

S

U

F

E

R

e

o

N

1

l

m

r

N

l

m

r

N

l

m

r

N

l

m

r

N

z

H

M

6

6

z

H

M

3

3

z

H

M

8

4

z

H

M

8

1

3

1

0

r

2

t

*

f

o

t

o

2

*

f

r

t

o

t

o

w

o

L

w

o

L

w

o

L

w

o

L

Notes:

1. Refer to tristate control of CPU and SRC clocks in section 7.7 for tristate timing and operation.

2. Refer to Control Registers in section 16 for CPU_Stop, SRC_Stop and PwrDwn SMBus tristate control addresses.

PD# should be sampled low by 2 consecutive CPU# rising edges before stopping clocks. All single ended clocks will be

held low on their next high to low transition.

All differential clocks will be held high on the next high to low transition of the complimentary clock. If the control register

determining to drive mode is set to 'tri-state', the differential pair will be stopped in tri-state mode, undriven.

When the drive mode but corresponding to the CPU or SRC clock of interest is set to '0' the true clock will be driven high at

2 x Iref and the complementary clock will be tristated. If the control register is programmed to '1' both clocks will be tristated.

PWRDWN#

CPU, 133MHz

CPU#, 133MHz

SRC, 100MHz

SRC#, 100MHz

3V66, 66MHz

USB, 48MHz

PCI, 33MHz

REF, 14.31818

PD# Assertion

相关PDF资料 |

PDF描述 |

|---|---|

| ICS952623YGT | Programmable Timing Control Hub for Next Gen P4 processor |

| ICS952623 | Programmable Timing Control Hub for Next Gen P4 processor |

| ICS952623YFT | Programmable Timing Control Hub for Next Gen P4 processor |

| ICS952623YGT | Programmable Timing Control Hub for Next Gen P4 processor |

| ICS95V847 | 2.5V Wide Range Frequency Clock Driver (45MHz - 233MHz) |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ICS952623YGT | 制造商:ICS 制造商全称:ICS 功能描述:Programmable Timing Control Hub for Next Gen P4 processor |

| ICS952702 | 制造商:ICS 制造商全称:ICS 功能描述:Programmable Timing Control Hub for K7 System |

| ICS952702YFLF-T | 制造商:ICS 制造商全称:ICS 功能描述:Programmable Timing Control Hub for K7 System |

| ICS952703 | 制造商:ICS 制造商全称:ICS 功能描述:Programmable Timing Control Hub for K7 System |

| ICS952703BF | 功能描述:IC TIMING CTRL HUB K7 48-SSOP RoHS:否 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:TCH™ 标准包装:28 系列:- 类型:时钟/频率发生器 PLL:是 主要目的:Intel CPU 服务器 输入:时钟 输出:LVCMOS 电路数:1 比率 - 输入:输出:3:22 差分 - 输入:输出:无/是 频率 - 最大:400MHz 电源电压:3.135 V ~ 3.465 V 工作温度:0°C ~ 85°C 安装类型:表面贴装 封装/外壳:64-TFSOP (0.240",6.10mm 宽) 供应商设备封装:64-TSSOP 包装:管件 |

发布紧急采购,3分钟左右您将得到回复。