- 您现在的位置:买卖IC网 > PDF目录362809 > ICS952623YFT Programmable Timing Control Hub for Next Gen P4 processor PDF资料下载

参数资料

| 型号: | ICS952623YFT |

| 英文描述: | Programmable Timing Control Hub for Next Gen P4 processor |

| 中文描述: | 可编程定时控制中心,为下一代P4处理器 |

| 文件页数: | 5/27页 |

| 文件大小: | 329K |

| 代理商: | ICS952623YFT |

第1页第2页第3页第4页当前第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页

5

Integrated

Circuit

Systems, Inc.

ICS952623

Advance Information

0758—02/08/05

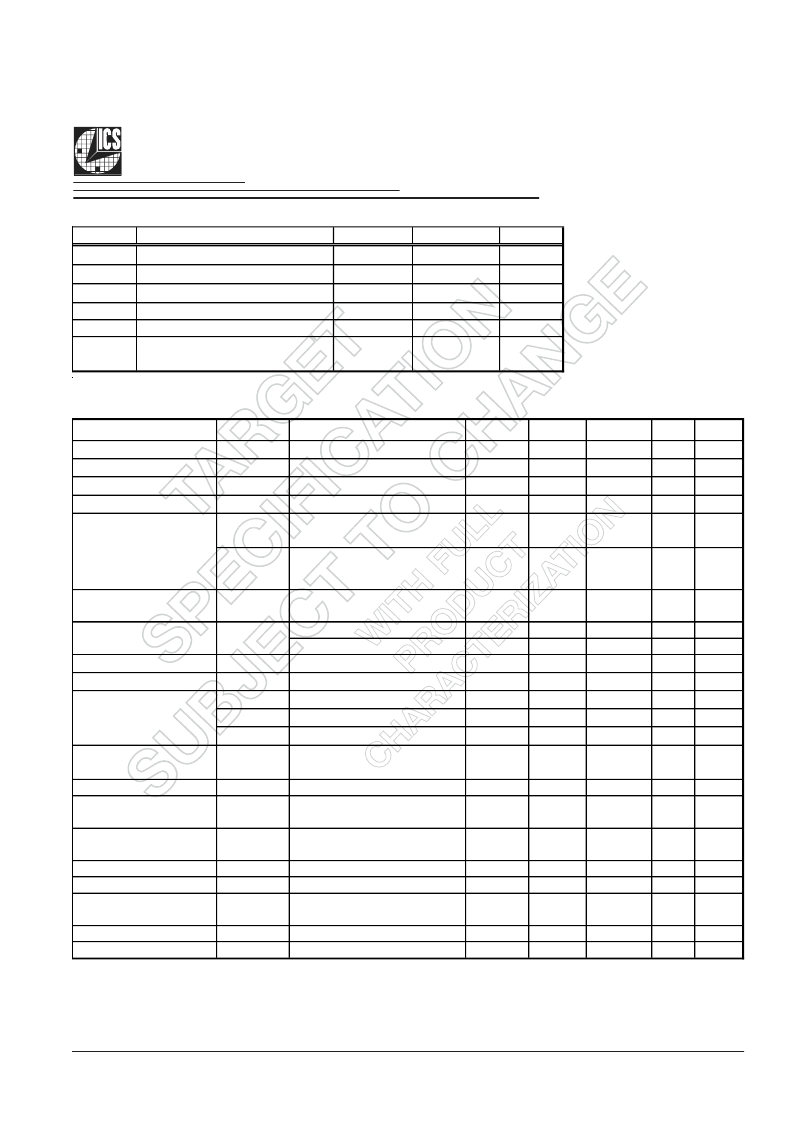

Absolute Max

Symbol

VDD_A

VDD_In

Ts

Tambient

Tcase

Parameter

Min

Max

Units

V

V

°

C

°C

°C

3.3V Core Supply Voltage

3.3V Logic Input Supply Voltage

Storage Temperature

Ambient Operating Temp

Case Temperature

Input ESD protection

human body model

V

DD

+ 0.5V

V

DD

+ 0.5V

150

70

115

GND - 0.5

-65

0

ESD prot

2000

V

Electrical Characteristics - Input/Supply/Common Output Parameters

T

A

= 0 - 70°C; Supply Voltage V

DD

= 3.3 V +/-5%

PARAMETER

SYMBOL

Input High Voltage

V

IH

Input MID Voltage

V

MID

Input Low Voltage

V

IL

Input High Current

I

IH

V

IN

= 0 V; Inputs with no pull-

CONDITIONS

3.3 V +/-5%

3.3 V +/-5%

3.3 V +/-5%

V

IN

= V

DD

MIN

2

1

TYP

MAX

V

DD

+ 0.3

1.8

0.8

5

UNITS NOTES

V

V

V

uA

V

SS

- 0.3

-5

I

IL1

up resistors

-5

uA

I

IL2

V

IN

= 0 V; Inputs with pull-up

resistors

-200

uA

Operating Supply Current

I

DD3.3OP

Full Active, C

L

= Full load;

350

mA

all diff pairs driven

all differential pairs tri-stated

V

DD

= 3.3 V

35

12

mA

mA

MHz

nH

pF

pF

pF

Input Frequency

3

Pin Inductance

1

F

i

L

pin

C

IN

C

OUT

C

INX

14.31818

3

1

1

1

1

7

5

6

5

Logic Inputs

Output pin capacitance

X1 & X2 pins

From V

DD

Power-Up or de-

assertion of PD# to 1st clock

Triangular Modulation

SRC output enable after

PCI_Stop# de-assertion

CPU output enable after

PD# de-assertion

PD# fall time of

PD# rise time of

CPU output enable after

CPU_Stop# de-assertion

PD# fall time of

PD# rise time of

Clk Stabilization

1,2

T

STAB

1.8

ms

1,2

Modulation Frequency

30

33

kHz

1

Tdrive_SRC

15

ns

1

Tdrive_PD#

300

us

1

Tfall_Pd#

Trise_Pd#

5

5

ns

ns

1

2

Tdrive_CPU_Stop#

10

us

1

Tfall_CPU_Stop#

Trise_CPU_Stop#

1

Guaranteed by design, not 100% tested in production.

2

See timing diagrams for timing requirements.

3

Input frequency should be measured at the REF output pin and tuned to ideal 14.31818MHz to meet

ppm frequency accuracy on PLL outputs.

5

5

ns

ns

1

2

I

DD3.3PD

Input Capacitance

1

Input Low Current

Powerdown Current

相关PDF资料 |

PDF描述 |

|---|---|

| ICS952623YGT | Programmable Timing Control Hub for Next Gen P4 processor |

| ICS952623 | Programmable Timing Control Hub for Next Gen P4 processor |

| ICS952623YFT | Programmable Timing Control Hub for Next Gen P4 processor |

| ICS952623YGT | Programmable Timing Control Hub for Next Gen P4 processor |

| ICS95V847 | 2.5V Wide Range Frequency Clock Driver (45MHz - 233MHz) |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ICS952623YGT | 制造商:ICS 制造商全称:ICS 功能描述:Programmable Timing Control Hub for Next Gen P4 processor |

| ICS952702 | 制造商:ICS 制造商全称:ICS 功能描述:Programmable Timing Control Hub for K7 System |

| ICS952702YFLF-T | 制造商:ICS 制造商全称:ICS 功能描述:Programmable Timing Control Hub for K7 System |

| ICS952703 | 制造商:ICS 制造商全称:ICS 功能描述:Programmable Timing Control Hub for K7 System |

| ICS952703BF | 功能描述:IC TIMING CTRL HUB K7 48-SSOP RoHS:否 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:TCH™ 标准包装:28 系列:- 类型:时钟/频率发生器 PLL:是 主要目的:Intel CPU 服务器 输入:时钟 输出:LVCMOS 电路数:1 比率 - 输入:输出:3:22 差分 - 输入:输出:无/是 频率 - 最大:400MHz 电源电压:3.135 V ~ 3.465 V 工作温度:0°C ~ 85°C 安装类型:表面贴装 封装/外壳:64-TFSOP (0.240",6.10mm 宽) 供应商设备封装:64-TSSOP 包装:管件 |

发布紧急采购,3分钟左右您将得到回复。