- 您现在的位置:买卖IC网 > PDF目录1999 > ICS95V850AGT (IDT, Integrated Device Technology Inc)IC CLK DVR PLL 1:10 48TSSOP PDF资料下载

参数资料

| 型号: | ICS95V850AGT |

| 厂商: | IDT, Integrated Device Technology Inc |

| 文件页数: | 5/10页 |

| 文件大小: | 0K |

| 描述: | IC CLK DVR PLL 1:10 48TSSOP |

| 产品变化通告: | Product Discontinuation 09/Dec/2011 |

| 标准包装: | 1,000 |

| 类型: | 时钟缓冲器/驱动器,多路复用器 |

| PLL: | 是 |

| 主要目的: | 存储器,DDR |

| 输入: | LVCMOS,LVDS,LVPELL,LVTTL |

| 输出: | SSTL-2 |

| 电路数: | 1 |

| 比率 - 输入:输出: | 1:10 |

| 差分 - 输入:输出: | 是/是 |

| 频率 - 最大: | 210MHz |

| 电源电压: | 2.3 V ~ 2.7 V |

| 工作温度: | 0°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 48-TFSOP(0.240",6.10mm 宽) |

| 供应商设备封装: | 48-TSSOP |

| 包装: | 带卷 (TR) |

| 其它名称: | 95V850AGT |

4

ICS95V850

0458G—11/21/08

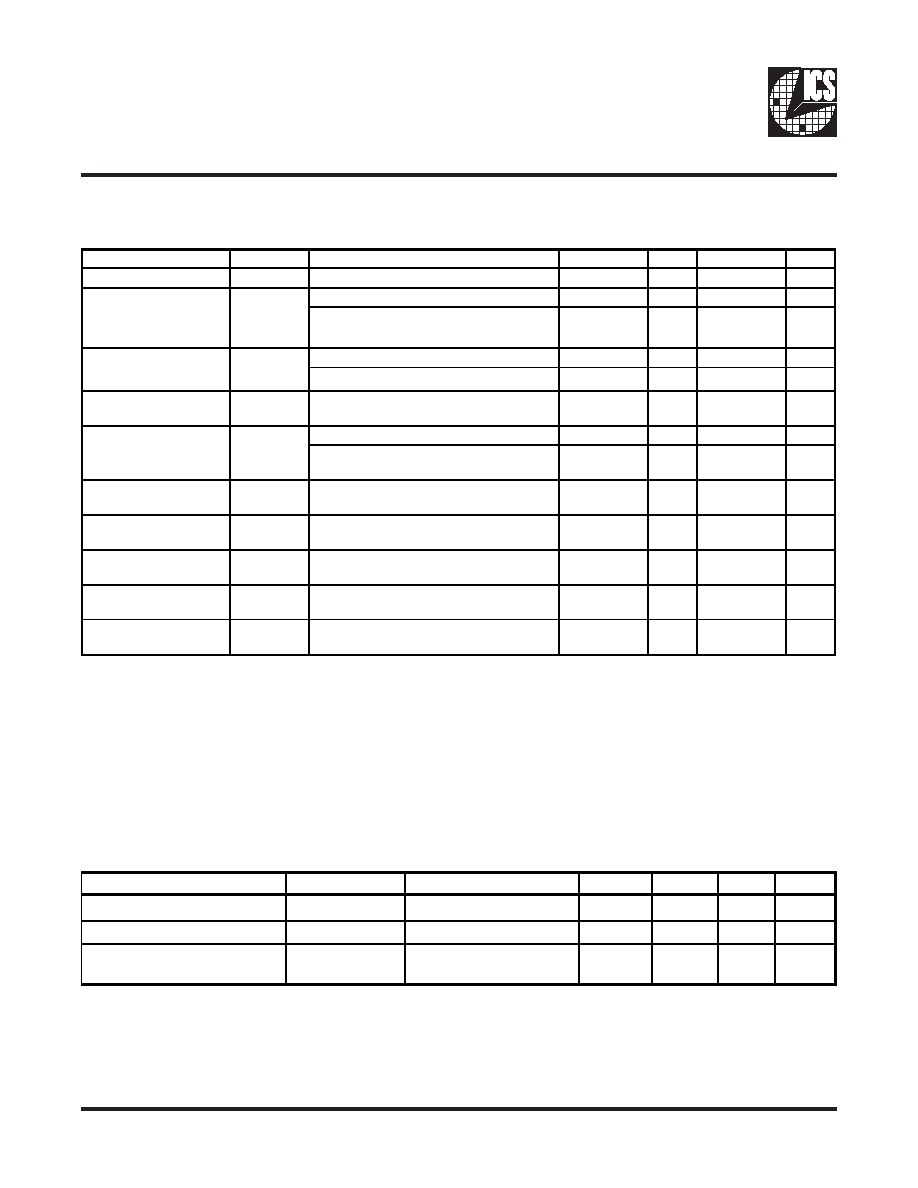

Timing Requirements

TA = 0 - 85°C; Supply Voltage AVDD, VDD = 2.5 V +/- 0.2V (unless otherwise stated)

PARAMETER

SYMBOL

CONDITIONS

MIN

TYP

MAX

UNITS

Operating clock frequency

freqop

66

210

MHz

Input clock duty cycle

dtin

40

60

%

CLK stabilization

TSTAB

15

s

Recommended Operating Condition (see note1)

TA = 0 - 85°C; Supply Voltage AVDD, VDD = 2.5 V +/- 0.2V (unless otherwise stated)

PARAMETER

SYMBOL

CONDITIONS

MIN

TYP

MAX

UNITS

Supply Voltage

VDD, AVDD

2.3

2.5

2.7

V

CLK_INT, CLK_INC, FB_INC

0.4

VDD/2 - 0.18

V

CLK_INT, CLK_INC (Universal Input)

-0.3

VDD - 0.4

V

CLK_INT, CLK_INC, FB_INC

VDD/2 + 0.18

2.1

V

CLK_INT, CLK_INC (Universal Input)

0.4

VDD + 0.3

V

DC input signal voltage

(note 2)

VIN

-0.3

VDD + 0.3

V

DC - CLK_INT, FB_INT

0.36

VDD + 0.6

V

AC - CLK_INT, FB_INT (Universal Input)

0.4

VDD + 0.6

V

Output differential cross-

voltage (note 4)

VOX

VDD/2 - 0.15

VDD/2 + 0.15

V

Input differential cross-

voltage (note 4)

VIX

(Universal Input)

0.45(VIH - VIL)

0.55(VIH - VIL)V

High level output

current

IOH

-6.4

mA

Low level output current

IOL

5.5

mA

Operating free-air

temperature

TA

085

°C

Differential input signal

voltage (note 3)

VID

Low level input voltage

VIL

High level input voltage

VIH

Notes:

1.

Unused inputs must be held high or low to prevent them from floating.

2.

DC input signal voltage specifies the allowable DC execution of differential input.

3.

Differential inputs signal voltages specifies the differential voltage [VTR-VCP]

required for switching, where VT is the true input level and VCP is the

complementary input level.

4.

Differential cross-point voltage is expected to track variations of VDD and is the

voltage at which the differential signal must be crossing.

相关PDF资料 |

PDF描述 |

|---|---|

| ICS95V857ALT | IC CLK DVR PLL 1:10 40TVSOP |

| ICS95V857CKLF8 | IC CLK DVR PLL 1:10 40VFQFN |

| ICS97U870AKT | IC CLK DVR PLL 1:10 40VFQFN |

| ICS97ULP877AHT | IC CLOCK DRIVER 1.8V LP 52-BGA |

| ICS97ULP877BKLFT | IC CLOCK DRIVER 1.8V LP 40VFQFPN |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ICS95V857 | 制造商:ICSI 制造商全称:Integrated Circuit Solution Inc 功能描述:2.5V Wide Range Frequency Clock Driver (45MHz - 233MHz) |

| ICS95V857_09 | 制造商:ICS 制造商全称:ICS 功能描述:2.5V Wide Range Frequency Clock Driver (45MHz - 233MHz) |

| ICS95V857AG | 功能描述:IC CLK DVR PLL 1:10 48TSSOP RoHS:否 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:- 标准包装:28 系列:- 类型:时钟/频率发生器 PLL:是 主要目的:Intel CPU 服务器 输入:时钟 输出:LVCMOS 电路数:1 比率 - 输入:输出:3:22 差分 - 输入:输出:无/是 频率 - 最大:400MHz 电源电压:3.135 V ~ 3.465 V 工作温度:0°C ~ 85°C 安装类型:表面贴装 封装/外壳:64-TFSOP (0.240",6.10mm 宽) 供应商设备封装:64-TSSOP 包装:管件 |

| ICS95V857AG-130LF-T | 制造商:ICSI 制造商全称:Integrated Circuit Solution Inc 功能描述:2.5V Wide Range Frequency Clock Driver (45MHz - 233MHz) |

| ICS95V857AGILF | 功能描述:IC CLK DVR PLL 1:10 48TSSOP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:- 标准包装:28 系列:- 类型:时钟/频率发生器 PLL:是 主要目的:Intel CPU 服务器 输入:时钟 输出:LVCMOS 电路数:1 比率 - 输入:输出:3:22 差分 - 输入:输出:无/是 频率 - 最大:400MHz 电源电压:3.135 V ~ 3.465 V 工作温度:0°C ~ 85°C 安装类型:表面贴装 封装/外壳:64-TFSOP (0.240",6.10mm 宽) 供应商设备封装:64-TSSOP 包装:管件 |

发布紧急采购,3分钟左右您将得到回复。