- 您现在的位置:买卖IC网 > PDF目录65536 > ICSSSTV16859YKLF (INTEGRATED DEVICE TECHNOLOGY INC) SSTV SERIES, POSITIVE EDGE TRIGGERED D FLIP-FLOP, TRUE OUTPUT, CQCC56 PDF资料下载

参数资料

| 型号: | ICSSSTV16859YKLF |

| 厂商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分类: | 锁存器 |

| 英文描述: | SSTV SERIES, POSITIVE EDGE TRIGGERED D FLIP-FLOP, TRUE OUTPUT, CQCC56 |

| 封装: | VFQFN-56 |

| 文件页数: | 8/8页 |

| 文件大小: | 91K |

| 代理商: | ICSSSTV16859YKLF |

8

ICSSSTV16859

0003G—05/21/02

Ordering Information

ICSSSTV16859yK

Designation for tape and reel packaging

Pattern Number (2 or 3 digit number for parts with ROM code

patterns)

Package Type

Revision Designator (will not correlate with datasheet revision)

Device Type (consists of 3 or 4 digit numbers)

Prefix

ICS, AV = Standard Device

Example:

ICS XXXX y K - PPP - T

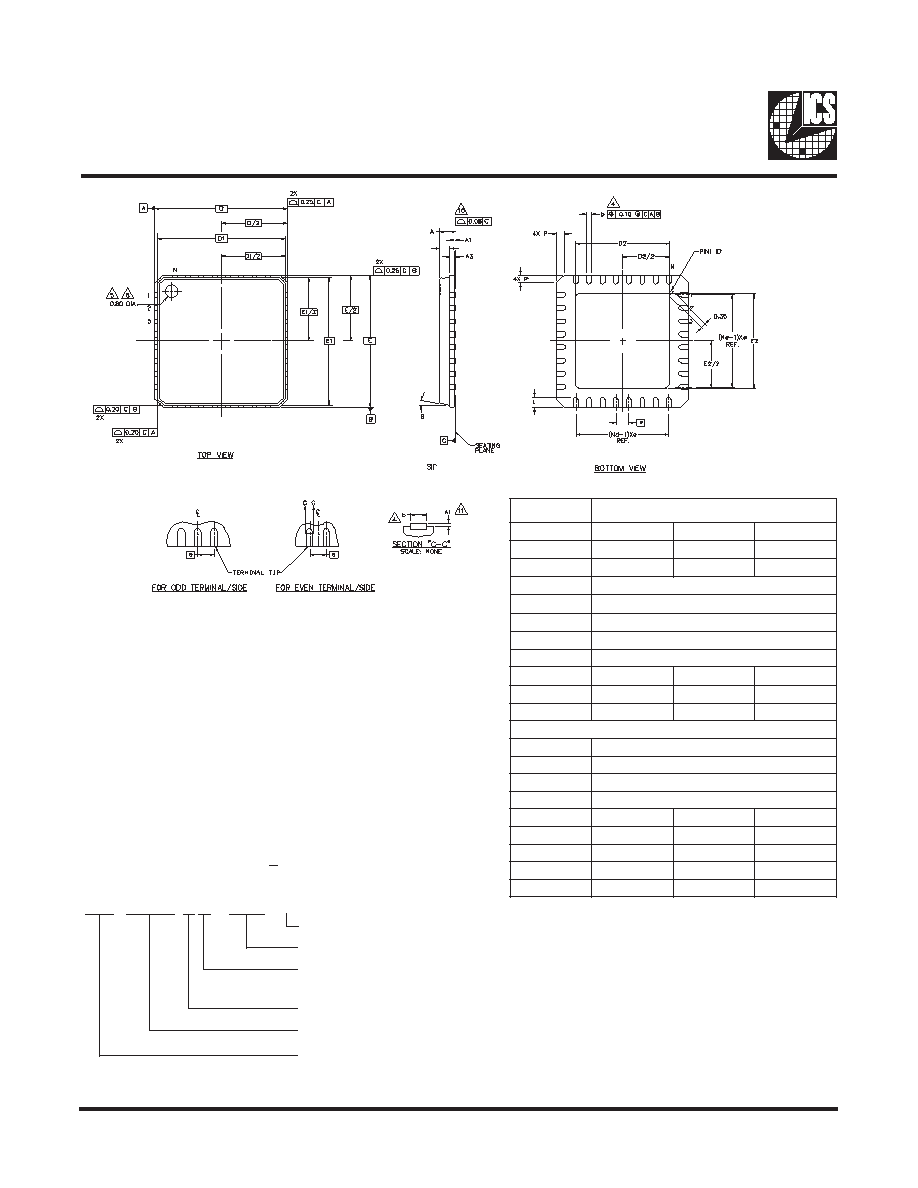

56 pin MLF2

l

o

b

m

y

Ss

n

o

i

s

n

e

m

i

D

n

o

m

o

C

A-

5

8

.

00

0

.

1

A0

0

.

01

0

.

05

0

.

0

2

A-

5

6

.

00

8

.

0

3

AC

S

B

0

2

.

0

DC

S

B

0

.

8

1

DC

S

B

5

7

.

7

EC

S

B

0

.

8

1

EC

S

B

5

7

.

7

Θ

2

1

P4

2

.

02

4

.

00

6

.

0

R3

1

.

07

1

.

03

2

.

0

D

n

o

i

t

a

r

a

V

h

c

t

i

P

eC

S

B

0

5

.

0

N6

5

d

N4

1

e

N4

1

L0

3

.

00

4

.

00

5

.

0

b8

1

.

03

2

.

00

3

.

0

Q0

0

.

00

2

.

05

4

.

0

2

D5

3

.

40

5

.

45

6

.

4

2

E5

0

.

50

2

.

55

3

.

5

相关PDF资料 |

PDF描述 |

|---|---|

| ICSSSTV32852AHLF | SSTV SERIES, POSITIVE EDGE TRIGGERED D FLIP-FLOP, TRUE OUTPUT, PBGA114 |

| ICSSSTVA16857YG-T | SSTV SERIES, POSITIVE EDGE TRIGGERED D FLIP-FLOP, TRUE OUTPUT, PDSO48 |

| ICSSSTVA16857YG-T | SSTV SERIES, POSITIVE EDGE TRIGGERED D FLIP-FLOP, TRUE OUTPUT, PDSO48 |

| ICSSSTVA16857YGLF-T | SSTV SERIES, POSITIVE EDGE TRIGGERED D FLIP-FLOP, TRUE OUTPUT, PDSO48 |

| ICSSSTVA32852CH-T | SSTV SERIES, POSITIVE EDGE TRIGGERED D FLIP-FLOP, TRUE OUTPUT, PBGA114 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ICSSSTV32852 | 制造商:ICS 制造商全称:ICS 功能描述:DDR 24-Bit to 48-Bit Registered Buffer |

| ICSSSTV32852YHT | 制造商:ICS 制造商全称:ICS 功能描述:DDR 24-Bit to 48-Bit Registered Buffer |

| ICSSSTVA16857 | 制造商:ICS 制造商全称:ICS 功能描述:DDR 14-Bit Registered Buffer |

| ICSSSTVA16857YGLF-T | 制造商:ICS 制造商全称:ICS 功能描述:DDR 14-Bit Registered Buffer |

| ICSSSTVA16859B | 制造商:ICS 制造商全称:ICS 功能描述:DDR 13-Bit to 26-Bit Registered Buffer |

发布紧急采购,3分钟左右您将得到回复。