- 您现在的位置:买卖IC网 > PDF目录67712 > IDT5T9955BFGI8 (INTEGRATED DEVICE TECHNOLOGY INC) 5T SERIES, PLL BASED CLOCK DRIVER, 8 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PBGA96 PDF资料下载

参数资料

| 型号: | IDT5T9955BFGI8 |

| 厂商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分类: | 时钟及定时 |

| 英文描述: | 5T SERIES, PLL BASED CLOCK DRIVER, 8 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PBGA96 |

| 封装: | GREEN, FBGA-96 |

| 文件页数: | 6/11页 |

| 文件大小: | 137K |

| 代理商: | IDT5T9955BFGI8 |

4

INDUSTRIALTEMPERATURERANGE

IDT5T9955

2.5V PROGRAMMABLE SKEW DUAL PLL CLOCK DRIVER TURBOCLOCK W

Output skew with respect to the REF input is adjustable to compensate

for PCB trace delays, backplane propagation delays or to accommodate

requirements for special timing relationships between clocked compo-

nents. Skew is selectable as a multiple of a time unit (tU) which ranges

from 782ps to 1.5625ns (see Programmable Skew Range and Resolu-

tion Table). There are nine skew configurations available for each out-

put pair. These configurations are chosen by the xnF1:0 control pins. In

order to minimize the number of control pins, 3-level inputs (HIGH-MID-

LOW) are used, they are intended for but not restricted to hard-wiring.

Undriven 3-level inputs default to the MID level. Where programmable

skew is not a requirement, the control pins can be left open for the zero

skew default setting. The Control Summary Table shows how to select

specific skew taps by using the xnF1:0 control pins.

PROGRAMMABLESKEW

EXTERNALFEEDBACK

By providing two separate external feedbacks, the IDT5T9955 gives

users flexibility with regard to skew adjustment. The xFB signal is com-

pared with the input REF signal at the phase detector in order to drive

the VCO. Phase differences cause the VCO of the PLL to adjust up-

wards or downwards accordingly.

NOTES:

1. The device may be operated outside recommended frequency ranges without damage, but functional operation is not guaranteed.

2. The level to be set on xFS is determined by the nominal operating frequency of the VCO and Time Unit Generator. The VCO frequency always appears at x1Q1:0, x2Q1:0, and

the higher outputs when they are operated in their undivided modes. The frequency appearing at the REF and xFB inputs will be FNOM when the output connected to xFB is

undivided and xDS[1:0] = MM. The frequency of the REF and xFB inputs will be FNOM /2 or FNOM /4 when the part is configured for frequency multiplication by using a divided

output as the xFB input and setting xDS[1:0] = MM. Using the xDS[1:0] inputs allows a different method for frequency multiplication (see Divide Selection Table).

3. Skew adjustment range assumes that a zero skew output is used for feedback. If a skewed xQ output is used for feedback, then adjustment range will be greater. For example

if a 4tU skewed output is used for feedback, all other outputs will be skewed –4tU in addition to whatever skew value is programmed for those outputs. ‘Max adjustment’ range

applies to output pairs 3 and 4 where ±6tU skew adjustment is possible and at the lowest FNOM value.

An internal loop filter moderates the response of the VCO to the

phase detector. The loop filter transfer function has been chosen to

provide minimal jitter (or frequency variation) while still providing accu-

rate responses to input frequency changes.

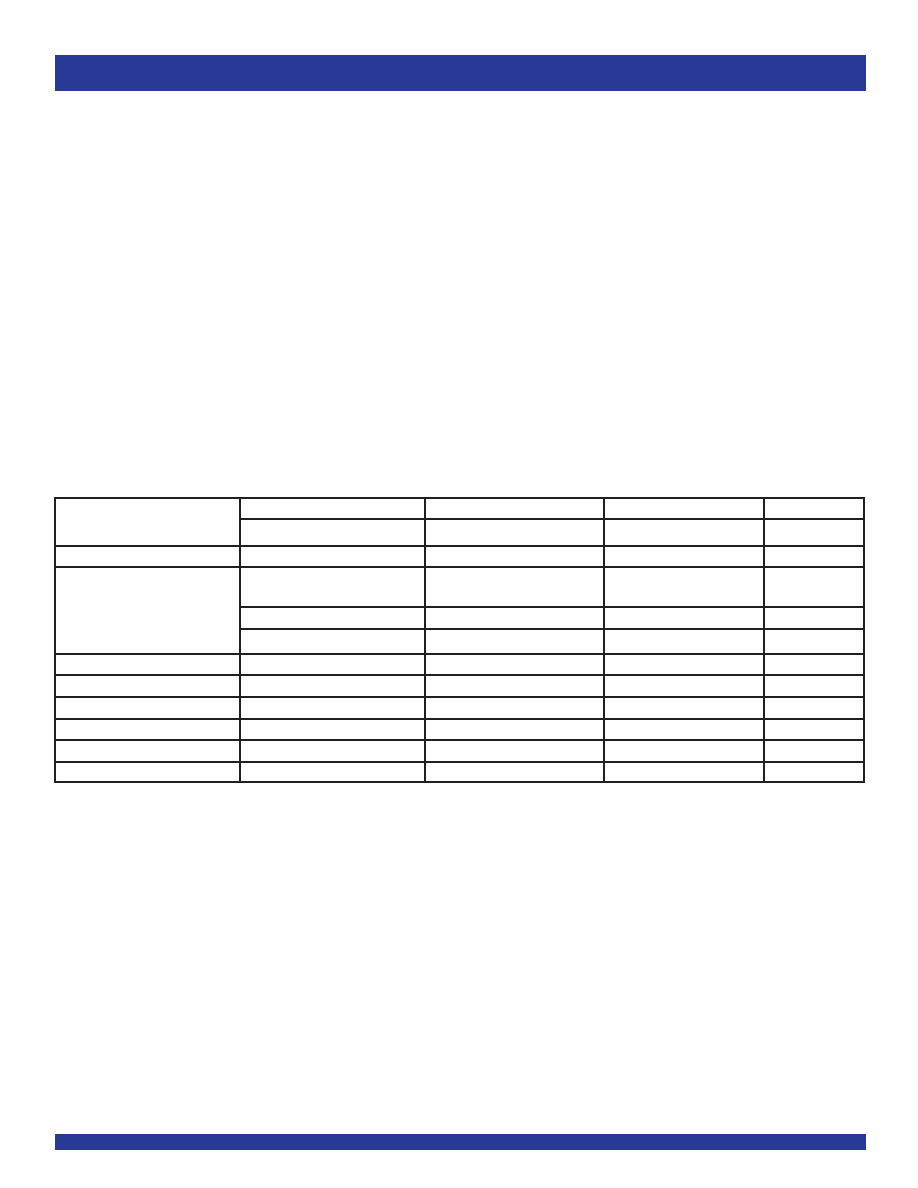

xFS = LOW

xFS = MID

xFS = HIGH

Comments

TimingUnitCalculation(tU)

1/(32 x FNOM)

1/(16 x FNOM)

1/(8 x FNOM)

VCOFrequencyRange(FNOM)(1,2)

24 to 40MHz

40 to 80MHz

80 to 160MHz

SkewAdjustmentRange(3)

Max Adjustment:

±7.8125ns

±9.375ns

ns

±67.5°

±135°

±270°

PhaseDegrees

±18.75%

±37.5%

±75%

% of Cycle Time

Example 1, FNOM = 25MHz

tU = 1.25ns

—

Example 2, FNOM = 37.5MHz

tU = 0.833ns

—

Example 3, FNOM = 50MHz

—

tU = 1.25ns

—

Example 4, FNOM = 75MHz

—

tU = 0.833ns

—

Example 5, FNOM = 100MHz

—

tU = 1.25ns

Example 6, FNOM = 150MHz

—

tU = 0.833ns

PROGRAMMABLE SKEW RANGE AND RESOLUTION TABLE

相关PDF资料 |

PDF描述 |

|---|---|

| IDT5V9888PFGI8 | 500 MHz, OTHER CLOCK GENERATOR, PQFP32 |

| IDT5V9888PFGI | 500 MHz, OTHER CLOCK GENERATOR, PQFP32 |

| IDT5V9955BFGI | 5V SERIES, PLL BASED CLOCK DRIVER, 8 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PBGA96 |

| IDT7216L20J8 | 16-BIT, DSP-MULTIPLIER, PQCC68 |

| IDT7216L25PQF | 16-BIT, DSP-MULTIPLIER, PQFP64 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| IDT5T995APPGI | 功能描述:IC CLK DRIVER 2.5V PLL 44-TQFP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:TurboClock™ II 标准包装:1,000 系列:- 类型:时钟/频率合成器,扇出分配 PLL:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 除法器/乘法器:- 电源电压:- 工作温度:- 安装类型:表面贴装 封装/外壳:56-VFQFN 裸露焊盘 供应商设备封装:56-VFQFP-EP(8x8) 包装:带卷 (TR) 其它名称:844S012AKI-01LFT |

| IDT5T995APPGI8 | 功能描述:IC CLK DRIVER 2.5V PLL 44-TQFP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:TurboClock™ II 标准包装:1,000 系列:- 类型:时钟/频率合成器,扇出分配 PLL:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 除法器/乘法器:- 电源电压:- 工作温度:- 安装类型:表面贴装 封装/外壳:56-VFQFN 裸露焊盘 供应商设备封装:56-VFQFP-EP(8x8) 包装:带卷 (TR) 其它名称:844S012AKI-01LFT |

| IDT5V19EE403NLGI | 制造商:Integrated Device Technology Inc 功能描述:IC CLOCK GENERATOR 24QFN |

| IDT5V19EE403NLGI8 | 制造商:Integrated Device Technology Inc 功能描述:IC CLK GEN VCXO PROGR 24QFN |

| IDT5V19EE404NLGI | 制造商:Integrated Device Technology Inc 功能描述:IC CLOCK GENERATOR 24QFN |

发布紧急采购,3分钟左右您将得到回复。