- 您现在的位置:买卖IC网 > PDF目录2076 > IDT5V49EE704NDGI8 (IDT, Integrated Device Technology Inc)IC PLL CLK GEN 200MHZ 28VFQFPN PDF资料下载

参数资料

| 型号: | IDT5V49EE704NDGI8 |

| 厂商: | IDT, Integrated Device Technology Inc |

| 文件页数: | 16/29页 |

| 文件大小: | 0K |

| 描述: | IC PLL CLK GEN 200MHZ 28VFQFPN |

| 产品培训模块: | VersaClock™ III Programmable Clocks |

| 特色产品: | VersaClock III Timing Devices |

| 标准包装: | 2,500 |

| 系列: | VersaClock™ III |

| 类型: | 时钟发生器,多路复用器 |

| PLL: | 带旁路 |

| 输入: | LVCMOS,LVTTL,晶体 |

| 输出: | LVCMOS,LVTTL |

| 电路数: | 1 |

| 比率 - 输入:输出: | 2:7 |

| 差分 - 输入:输出: | 无/无 |

| 频率 - 最大: | 200MHz |

| 除法器/乘法器: | 是/是 |

| 电源电压: | 3.135 V ~ 3.465 V |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 28-VFQFN 裸露焊盘 |

| 供应商设备封装: | 28-VFQFPN(4x4) |

| 包装: | 带卷 (TR) |

| 其它名称: | IDT5V49EE704DLGI8 IDT5V49EE704DLGI8-ND |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页当前第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页

IDT5V49EE704

EEPROM PROGRAMMABLE CLOCK GENERATOR

CLOCK SYNTHESIZER

IDT EEPROM PROGRAMMABLE CLOCK GENERATOR

23

IDT5V49EE704

REV M 092412

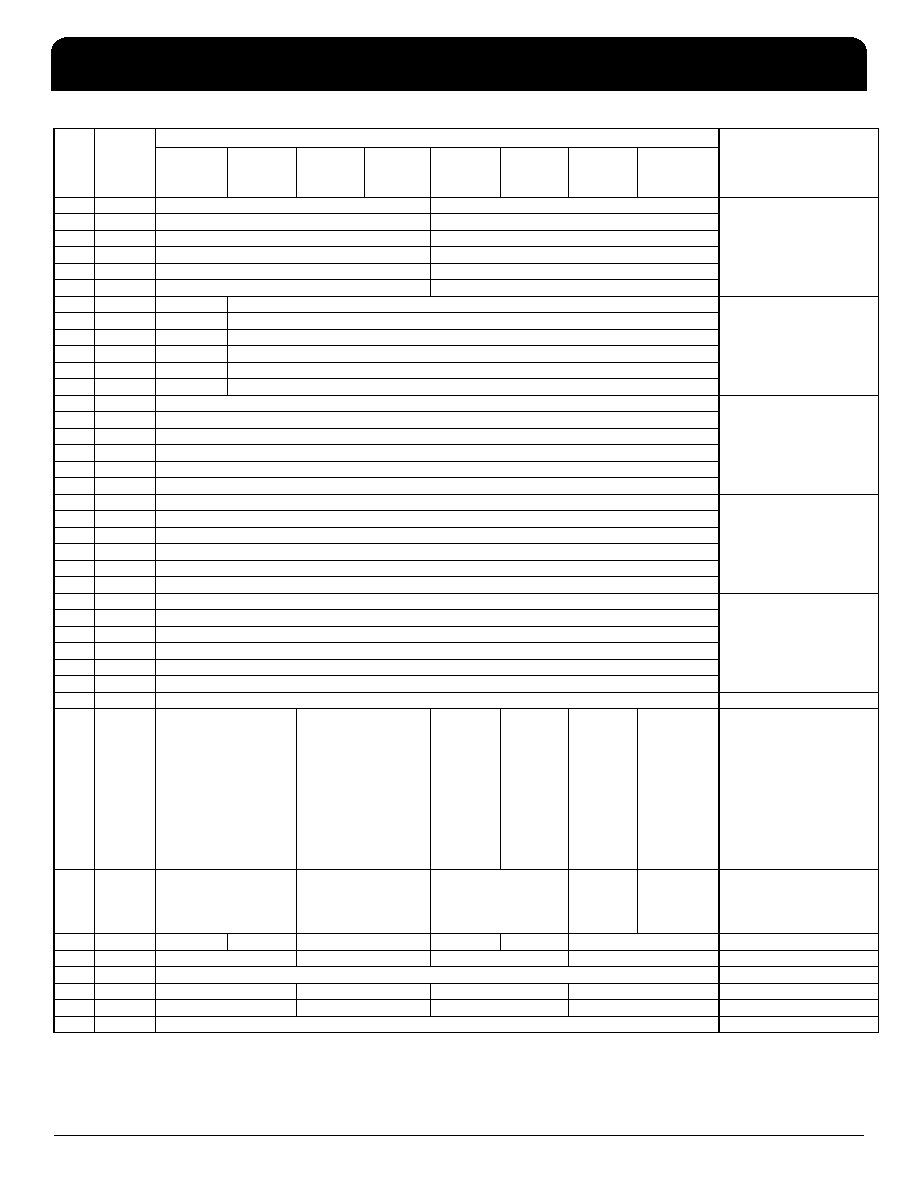

0x56

00

IP3[3:0]_CFG4

RZ3[3:0]_CFG4

PLL3 Loop Parameter

0x57

00

IP3[3:0]_CFG5

RZ3[3:0]_CFG5

0x58

00

IP3[3:0]_CFG0

RZ3[3:0]_CFG0

0x59

00

IP3[3:0]_CFG1

RZ3[3:0]_CFG1

0x5A

00

IP3[3:0]_CFG2

RZ3[3:0]_CFG2

0x5B

00

IP3[3:0]_CFG3

RZ3[3:0]_CFG3

0x5C

03

Reserved

D3[6:0]_CFG0

PLL3 Reference Divide and input

sel

D3[6:0] - 127 step Ref Div

D3 = 0 means power down.

0x5D

03

Reserved

D3[6:0]_CFG1

0x5E

03

Reserved

D3[6:0]_CFG2

0x5F

03

Reserved

D3[6:0]_CFG3

0x60

03

Reserved

D3[6:0]_CFG4

0x61

03

Reserved

D3[6:0]_CFG5

0x62

0C

N3[7:0]_CFG4

N - Feedback Divider

12 - 4095 (values of “0” through

“11” are not allowed)

0x63

0C

N3[7:0]_CFG5

0x64

0C

N3[7:0]_CFG0

0x65

0C

N3[7:0]_CFG1

0x66

0C

N3[7:0]_CFG2

0x67

0C

N3[7:0]_CFG3

0x68

00

SSVCO[7:0]_CFG0

SSVCO[7:0] - PLL3 Spread

Spectrum Loop Feedback

Counter

See Addr 0x80:0x85 for

SSVCO[15:8]

0x69

00

SSVCO[7:0]_CFG1

0x6A

00

SSVCO[7:0]_CFG2

0x6B

00

SSVCO[7:0]_CFG3

0x6C

00

SSVCO[7:0]_CFG4

0x6D

00

SSVCO[7:0]_CFG5

0x6E

00

SS_D3[7:0]_CFG4

SS_D[7:0] - PLL3 Spread

Spectrum Reference Divide

0x6F

00

SS_D3[7:0]_CFG5

0x70

00

SS_D3[7:0]_CFG0

0x71

00

SS_D3[7:0]_CFG1

0x72

00

SS_D3[7:0]_CFG2

0x73

00

SS_D3[7:0]_CFG3

0x74

01

Reserved

0x75

03

OEM0[1:0]

SLEW0[1:0]

INV0

Reserved

S1

S3

Output Controls

S1=1 - OUT1/OUT2 are from

DIV1/DIV2 respectively

S1=0 - Both from DIV2

S3 =1 - OUT3/OUT6 are from

DIV3/DIV6

S3=0 - Both from DIV6

SLEW - see AC Timing

OEM#–output enable mode

x0 - tristated

01 - park low

11 - park high

OEM0 controls OUT0 only

0x76

00

OEM1[1:0]

SLEW1[1:0]

INV1[1:0]

Reserved

Output Controls

INV1 [CLK1, CLK2]

[0] - normal

[1] - invert clock

OEM1 controls OUT1/OUT2

0x77

00

SLEW2[1:0]

Reserved

0x78

00

OEM3[1:0]

SLEW3[1:0]

INV3[1:0]

Reserved

OEM3 controls OUT3 and OUT6

0x79

00

Reserved

0x7A

00

OEM5[1:0]

SLEW5[1:0]

INV5[1:0]

Reserved

OEM5 controls OUT5 and OUT5b

0x7B

00

Reserved

SLEW6[1:0]

Reserved

0x7C

XX1

Reserved

Addr

Default

Register

Hex

Value

Bit #

Description

76

5

4

3

2

1

0

相关PDF资料 |

PDF描述 |

|---|---|

| IDT5V50013DCG | IC CLK GENERATOR LOW EMI 8-SOIC |

| IDT5V50015DCG | IC CLK GENERATOR LOW EMI 8SOIC |

| IDT5V551DCI8 | IC CLK BUFFER 1:4 160MHZ 8-SOIC |

| IDT5V9885TPFGI | IC CLOCK GEN PLL 500MHZ 32TQFP |

| IDT7202LA15SOI | IC FIFO ASYNCH 1KX9 15NS 28SOIC |

相关代理商/技术参数 |

参数描述 |

|---|---|

| IDT5V49EE901-064PGGI | 制造商:Integrated Device Technology Inc 功能描述:IC PLL CLK GEN 500MHZ 24VQFN |

| IDT5V49EE901-064PGGI8 | 制造商:Integrated Device Technology Inc 功能描述:IC PLL CLK GEN 500MHZ 24VQFN |

| IDT5V49EE901-EVB | 制造商:Integrated Device Technology Inc 功能描述:EVAL BOARD FOR IDT 5V49EE901 |

| IDT5V49EE901NLGI | 功能描述:IC PLL CLK GEN 200MHZ 32VFQFN RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:VersaClock™ III 标准包装:2,000 系列:- 类型:PLL 频率合成器 PLL:是 输入:晶体 输出:时钟 电路数:1 比率 - 输入:输出:1:1 差分 - 输入:输出:无/无 频率 - 最大:1GHz 除法器/乘法器:是/无 电源电压:4.5 V ~ 5.5 V 工作温度:-20°C ~ 85°C 安装类型:表面贴装 封装/外壳:16-LSSOP(0.175",4.40mm 宽) 供应商设备封装:16-SSOP 包装:带卷 (TR) 其它名称:NJW1504V-TE1-NDNJW1504V-TE1TR |

| IDT5V49EE901NLGI8 | 功能描述:IC PLL CLK GEN 200MHZ 32VFQFN RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:VersaClock™ III 标准包装:1,000 系列:- 类型:时钟/频率合成器,扇出分配 PLL:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 除法器/乘法器:- 电源电压:- 工作温度:- 安装类型:表面贴装 封装/外壳:56-VFQFN 裸露焊盘 供应商设备封装:56-VFQFP-EP(8x8) 包装:带卷 (TR) 其它名称:844S012AKI-01LFT |

发布紧急采购,3分钟左右您将得到回复。