- 您现在的位置:买卖IC网 > PDF目录2076 > IDT5V49EE704NDGI8 (IDT, Integrated Device Technology Inc)IC PLL CLK GEN 200MHZ 28VFQFPN PDF资料下载

参数资料

| 型号: | IDT5V49EE704NDGI8 |

| 厂商: | IDT, Integrated Device Technology Inc |

| 文件页数: | 5/29页 |

| 文件大小: | 0K |

| 描述: | IC PLL CLK GEN 200MHZ 28VFQFPN |

| 产品培训模块: | VersaClock™ III Programmable Clocks |

| 特色产品: | VersaClock III Timing Devices |

| 标准包装: | 2,500 |

| 系列: | VersaClock™ III |

| 类型: | 时钟发生器,多路复用器 |

| PLL: | 带旁路 |

| 输入: | LVCMOS,LVTTL,晶体 |

| 输出: | LVCMOS,LVTTL |

| 电路数: | 1 |

| 比率 - 输入:输出: | 2:7 |

| 差分 - 输入:输出: | 无/无 |

| 频率 - 最大: | 200MHz |

| 除法器/乘法器: | 是/是 |

| 电源电压: | 3.135 V ~ 3.465 V |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 28-VFQFN 裸露焊盘 |

| 供应商设备封装: | 28-VFQFPN(4x4) |

| 包装: | 带卷 (TR) |

| 其它名称: | IDT5V49EE704DLGI8 IDT5V49EE704DLGI8-ND |

第1页第2页第3页第4页当前第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页

IDT5V49EE704

EEPROM PROGRAMMABLE CLOCK GENERATOR

CLOCK SYNTHESIZER

IDT EEPROM PROGRAMMABLE CLOCK GENERATOR

13

IDT5V49EE704

REV M 092412

Programming the Device

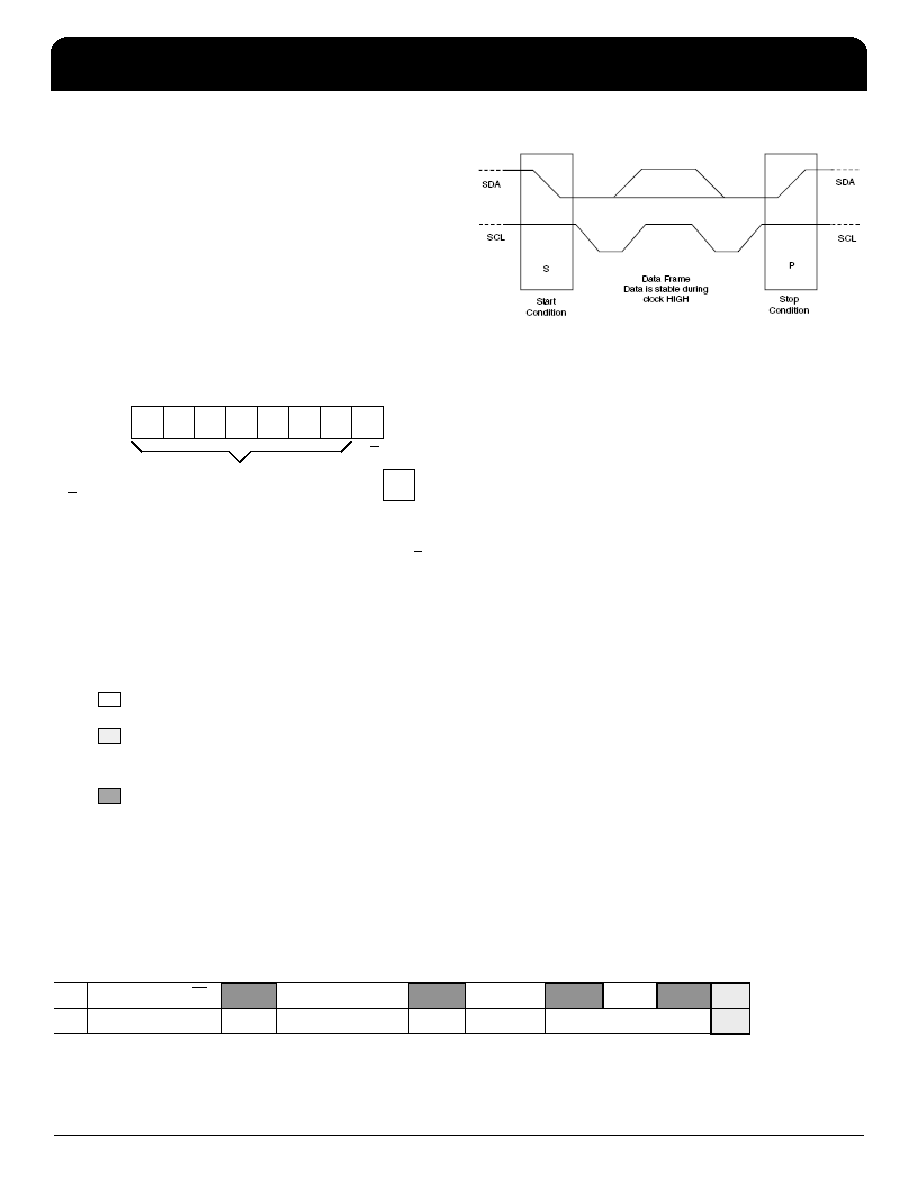

I2C may be used to program the IDT5V49EE704.

– Device (slave) address = 7'b1101010

I2C Programming

The IDT5V49EE704 is programmed through an I2C-Bus

serial interface, and is an I2C slave device. The read and

write transfer formats are supported. The first byte of data

after a write frame to the correct slave address is interpreted

as the register address; this address auto-increments after

each byte written or read.

The frame formats are shown in the following illustration.

Framing

First Byte Transmitted on I2C Bus

External I2C Interface Condition

Progwrite

Progwrite Command Frame

Writes can continue as long as a Stop condition is not sent and each byte will increment the register address.

1

0

1

0

1

0

1

MSB

LSB

R/W

ACK from Slave

R/W

0 – Slave will be written by master

1 – Slave will be read by master

The first byte transmitted by the Master is the Slave Address followed by the R/W bit.

The Slave acknowledges by sending a “1” bit.

7-bit slave address

KEY:

From Master to Slave

From Master to Slave, but can be omitted if followed by the correct sequence

Normally, data transfer is terminated by a STOP condition generated by the Master. However, if the Master still wishes to communicate on the bus, it can

generate a separate START condition, and address another Slave address without first generating a STOP condition.

From Slave to Master

SYMBOLS:

ACK - Acknowledge (SDAT LOW)

NACK – Not Acknowledge (SDAT HIGH)

SR – Repeated Start Condition

S – START Condition

P – STOP Condition

SAddress

R/W

ACK

Command Code

ACK

Register

ACK

Data

ACK

P

7-bits

0

1-bit

8-bits: xxxx xx00

1-bit

8-bits

1-bit

8-bits

1-bit

相关PDF资料 |

PDF描述 |

|---|---|

| IDT5V50013DCG | IC CLK GENERATOR LOW EMI 8-SOIC |

| IDT5V50015DCG | IC CLK GENERATOR LOW EMI 8SOIC |

| IDT5V551DCI8 | IC CLK BUFFER 1:4 160MHZ 8-SOIC |

| IDT5V9885TPFGI | IC CLOCK GEN PLL 500MHZ 32TQFP |

| IDT7202LA15SOI | IC FIFO ASYNCH 1KX9 15NS 28SOIC |

相关代理商/技术参数 |

参数描述 |

|---|---|

| IDT5V49EE901-064PGGI | 制造商:Integrated Device Technology Inc 功能描述:IC PLL CLK GEN 500MHZ 24VQFN |

| IDT5V49EE901-064PGGI8 | 制造商:Integrated Device Technology Inc 功能描述:IC PLL CLK GEN 500MHZ 24VQFN |

| IDT5V49EE901-EVB | 制造商:Integrated Device Technology Inc 功能描述:EVAL BOARD FOR IDT 5V49EE901 |

| IDT5V49EE901NLGI | 功能描述:IC PLL CLK GEN 200MHZ 32VFQFN RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:VersaClock™ III 标准包装:2,000 系列:- 类型:PLL 频率合成器 PLL:是 输入:晶体 输出:时钟 电路数:1 比率 - 输入:输出:1:1 差分 - 输入:输出:无/无 频率 - 最大:1GHz 除法器/乘法器:是/无 电源电压:4.5 V ~ 5.5 V 工作温度:-20°C ~ 85°C 安装类型:表面贴装 封装/外壳:16-LSSOP(0.175",4.40mm 宽) 供应商设备封装:16-SSOP 包装:带卷 (TR) 其它名称:NJW1504V-TE1-NDNJW1504V-TE1TR |

| IDT5V49EE901NLGI8 | 功能描述:IC PLL CLK GEN 200MHZ 32VFQFN RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:VersaClock™ III 标准包装:1,000 系列:- 类型:时钟/频率合成器,扇出分配 PLL:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 除法器/乘法器:- 电源电压:- 工作温度:- 安装类型:表面贴装 封装/外壳:56-VFQFN 裸露焊盘 供应商设备封装:56-VFQFP-EP(8x8) 包装:带卷 (TR) 其它名称:844S012AKI-01LFT |

发布紧急采购,3分钟左右您将得到回复。