- 您现在的位置:买卖IC网 > PDF目录3954 > IDT70V5378S100BG (IDT, Integrated Device Technology Inc)IC SRAM 576KBIT 100MHZ 272BGA PDF资料下载

参数资料

| 型号: | IDT70V5378S100BG |

| 厂商: | IDT, Integrated Device Technology Inc |

| 文件页数: | 24/29页 |

| 文件大小: | 0K |

| 描述: | IC SRAM 576KBIT 100MHZ 272BGA |

| 标准包装: | 40 |

| 格式 - 存储器: | RAM |

| 存储器类型: | SRAM - 四端口,同步 |

| 存储容量: | 576K(32K x 18) |

| 速度: | 100MHz |

| 接口: | 并联 |

| 电源电压: | 3.15 V ~ 3.45 V |

| 工作温度: | 0°C ~ 70°C |

| 封装/外壳: | 272-BBGA |

| 供应商设备封装: | 272-PBGA(27x27) |

| 包装: | 托盘 |

| 其它名称: | 70V5378S100BG |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页当前第24页第25页第26页第27页第28页第29页

�� �

�

�

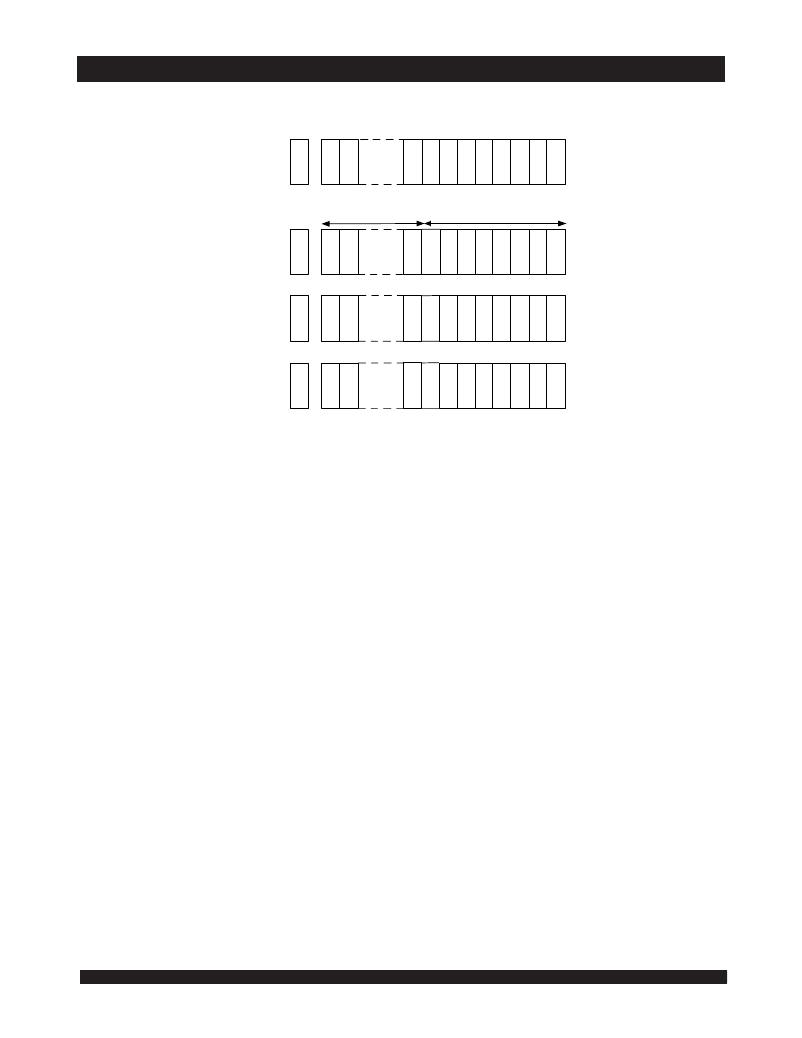

�IDT70V5388/78�

�3.3V� 64/32K� x� 18� Synchronous� FourPort?� Static� RAM�

�Counter-Mask� Register�

�CNTINT�

�Load�

�Industrial� and� Commercial� Temperature� Ranges�

�STEP� 1�

�Counter-Mask�

�Register� =� FF�

�H�

�0� 0�

�0's�

�0� 1� 1� 1� 1� 1� 1� 1� 1�

�A� 15� (2)� A� 14�

�A� 8� A� 7� A� 6� A� 5� A� 4� A� 3� A� 2� A� 1� A� 0�

�Load�

�Masked� Address�

�Counter� Address�

�STEP� 2�

�Address�

�Counter� =� FD�

�H�

�0� 0�

�0's�

�0� 1� 1� 1� 1� 1� 1� 0� 1�

�Max�

�A� 15� (2)� A� 14�

�A� 8� A� 7� A� 6� A� 5� A� 4� A� 3� A� 2� A� 1� A� 0�

�STEP� 3�

�Address�

�Register�

�H�

�X� X�

�X's�

�X� 1� 1� 1� 1� 1� 1� 1� 1�

�,�

�A� 15� (2)� A� 14�

�A� 8� A� 7� A� 6� A� 5� A� 4� A� 3� A� 2� A� 1� A� 0�

�STEP� 4�

�Max� +� 1�

�Address�

�Register�

�L�

�X� X�

�X's�

�X� 0� 0� 0� 0� 0� 0� 0� 0�

�A� 15� (2)� A� 14�

�A� 8� A� 7� A� 6� A� 5� A� 4� A� 3� A� 2� A� 1� A� 0�

�Figure� 5.� Programmable� Counter-Mask� Register� Operation� (1)�

�NOTE:�

�1.� The� "X's"� in� this� diagram� represent� the� upper� bits� of� the� counter.�

�2.� A� 15� is� a� NC� for� IDT70V5378.�

�5649� drw� 23�

�The� internal� address� counter� on� each� port� has� an�

�associated� Counter� Mask� Register� that� allows� for� configu-�

�ration� of� the� internal� address� counter� on� that� port.� Truth�

�Table� III� groups� the� operations� of� the� address� counter� with�

�those� of� the� counter� mask� register,� to� include� Master� Reset�

�and� applicable� readback� operations.�

�Each� bit� in� the� mask� register� controls� the� corre-�

�sponding� bit� in� the� internal� address� counter:� writing� a� “1”� to�

�a� bit� in� the� mask� register� allows� that� bit� to� increment� in�

�response� to� CNTINC� ,� while� writing� a� “0”� to� a� bit� masks� it� (i.e.,�

�locks� it� at� whatever� value� is� loaded� via� CNTLD� ).� The� mask�

�register� is� extremely� flexible:� every� bit� can� be� controlled�

�independently� of� every� other� bit.� The� counter� simply� concat-�

�enates� those� bits� that� have� not� been� masked,� giving� the�

�user� great� selectivity� in� determining� which� portions� of� the�

�memory� array� are� available� to� a� particular� port� for� burst�

�operations.�

�Figure� 5� illustrates� the� operation� of� the� Counter�

�Mask� Register� in� simply� constraining� a� port� to� a� selected�

�portion� of� the� array,� specifically� addresses� 0000h� to� 00FFh.�

�In� step� one,� the� mask� register� is� loaded� with� 00FFh� via� MKLD�

�(see� also� the� Load� and� Read� Mask� Register� timing� wave-�

�form� on� page� 19).� In� step� two,� a� starting� address� of� 00FD� is�

�asserted� for� the� start� point� of� a� burst,� and� the� CNTINC� control�

�is� enabled.� Step� three� indicates� the� address� counter�

�incrementing� to� 00FFh.� In� step� four,� the� internal� counter�

�determines� that� all� address� values� greater� than� 00FFh� have�

�been� masked,� and� so� it� increments� past� this� ‘max’� value� to�

�0000h.� As� a� result� of� reaching� 0000h� via� the� CNTINC�

�operation,� the� CNTINT� output� for� this� port� is� automatically�

�triggered� –� it� will� go� low� for� one� clock� cycle� and� then� reset.�

�The� example� depicted� in� Figure� 5� is� a� very� simple�

�one:� it� is� also� possible� to� mask� non-contiguous� bits,� such�

�as� loading� 5555h� in� the� mask� register.� As� stated� previously,�

�the� address� counter� simply� concatenates� all� bits� that� have�

�not� been� masked� and� continues� to� increment� those� bits� in�

�accordance� with� the� CNTINC� control:� in� this� fashion,� if� the�

�mask� register� is� set� at� 5555h� and� a� start� address� of� 0007h�

�is� asserted� via� CNTLD� ,� the� next� value� the� counter� will�

�increment� to� in� response� to� the� CNTINC� control� is� 0012h,�

�then� 0013h,� then� 0016h,� etc.�

�Besides� supporting� precise� control� of� which� por-�

�tions� of� the� array� are� available� to� a� particular� port� in� burst�

�operations,� the� independent� control� on� the� mask� register�

�bits� also� provides� excellent� flexibility� in� determining� the�

�value� by� which� the� counter� will� increment.� For� example,�

�setting� bit� 0� of� the� mask� register� to� “0”� masks� it� from� counter�

�operation,� effectively� configuring� that� port� to� count� by�

�increments� of� two.� This� can� be� very� useful� in� configuring� two�

�ports� to� work� in� combination,� effectively� creating� a� single�

�36-bit� port.� Thus,� Port� 1� can� be� configured� to� count� by� two�

�starting� on� even� addresses� (the� start� point� is� asserted� via�

�CNTLD� ),� and� Port� 2� can� be� configured� to� count� by� two�

�starting� on� odd� addresses� (again� via� CNTLD� ).� The� two� ports�

�together� will� operate� on� 36-bit� data� words,� storing� half� of�

�each� word� in� an� even-numbered� address,� the� other� half� in�

�an� odd-numbered� address.� Setting� bits� 1� and� 0� of� the� mask�

�register� on� a� given� port� to� “0”� configures� that� port� to� count�

�24�

�相关PDF资料 |

PDF描述 |

|---|---|

| MC7448HX1000LD | IC MPU RISC 32BIT 360-FCCBGA |

| MC68360ZQ25LR2 | IC MPU QUICC 25MHZ 357-PBGA |

| 346-012-520-804 | CARDEDGE 12POS DUAL .125 GREEN |

| 346-012-520-802 | CARDEDGE 12POS DUAL .125 GREEN |

| MC68360CZQ25LR2 | IC MPU QUICC 25MHZ 357-PBGA |

相关代理商/技术参数 |

参数描述 |

|---|---|

| IDT70V5378S100BG8 | 功能描述:IC SRAM 576KBIT 100MHZ 272BGA RoHS:否 类别:集成电路 (IC) >> 存储器 系列:- 标准包装:3,000 系列:- 格式 - 存储器:EEPROMs - 串行 存储器类型:EEPROM 存储容量:8K (1K x 8) 速度:400kHz 接口:I²C,2 线串口 电源电压:1.7 V ~ 5.5 V 工作温度:-40°C ~ 85°C 封装/外壳:8-SOIC(0.154",3.90mm 宽) 供应商设备封装:8-SOIC 包装:带卷 (TR) |

| IDT70V5378S133BC | 功能描述:IC SRAM 576KBIT 133MHZ 256BGA RoHS:否 类别:集成电路 (IC) >> 存储器 系列:- 标准包装:3,000 系列:- 格式 - 存储器:EEPROMs - 串行 存储器类型:EEPROM 存储容量:8K (1K x 8) 速度:400kHz 接口:I²C,2 线串口 电源电压:1.7 V ~ 5.5 V 工作温度:-40°C ~ 85°C 封装/外壳:8-SOIC(0.154",3.90mm 宽) 供应商设备封装:8-SOIC 包装:带卷 (TR) |

| IDT70V5378S133BC8 | 功能描述:IC SRAM 576KBIT 133MHZ 256BGA RoHS:否 类别:集成电路 (IC) >> 存储器 系列:- 标准包装:3,000 系列:- 格式 - 存储器:EEPROMs - 串行 存储器类型:EEPROM 存储容量:8K (1K x 8) 速度:400kHz 接口:I²C,2 线串口 电源电压:1.7 V ~ 5.5 V 工作温度:-40°C ~ 85°C 封装/外壳:8-SOIC(0.154",3.90mm 宽) 供应商设备封装:8-SOIC 包装:带卷 (TR) |

| IDT70V5378S133BG | 功能描述:IC SRAM 576KBIT 133MHZ 272BGA RoHS:否 类别:集成电路 (IC) >> 存储器 系列:- 标准包装:3,000 系列:- 格式 - 存储器:EEPROMs - 串行 存储器类型:EEPROM 存储容量:8K (1K x 8) 速度:400kHz 接口:I²C,2 线串口 电源电压:1.7 V ~ 5.5 V 工作温度:-40°C ~ 85°C 封装/外壳:8-SOIC(0.154",3.90mm 宽) 供应商设备封装:8-SOIC 包装:带卷 (TR) |

| IDT70V5378S133BG8 | 功能描述:IC SRAM 576KBIT 133MHZ 272BGA RoHS:否 类别:集成电路 (IC) >> 存储器 系列:- 标准包装:3,000 系列:- 格式 - 存储器:EEPROMs - 串行 存储器类型:EEPROM 存储容量:8K (1K x 8) 速度:400kHz 接口:I²C,2 线串口 电源电压:1.7 V ~ 5.5 V 工作温度:-40°C ~ 85°C 封装/外壳:8-SOIC(0.154",3.90mm 宽) 供应商设备封装:8-SOIC 包装:带卷 (TR) |

发布紧急采购,3分钟左右您将得到回复。