- 您现在的位置:买卖IC网 > PDF目录3967 > IDT70V658S10BF (IDT, Integrated Device Technology Inc)IC SRAM 2MBIT 10NS 208FBGA PDF资料下载

参数资料

| 型号: | IDT70V658S10BF |

| 厂商: | IDT, Integrated Device Technology Inc |

| 文件页数: | 20/24页 |

| 文件大小: | 0K |

| 描述: | IC SRAM 2MBIT 10NS 208FBGA |

| 标准包装: | 7 |

| 格式 - 存储器: | RAM |

| 存储器类型: | SRAM - 双端口,异步 |

| 存储容量: | 2M(64K x 36) |

| 速度: | 10ns |

| 接口: | 并联 |

| 电源电压: | 3.15 V ~ 3.45 V |

| 工作温度: | 0°C ~ 70°C |

| 封装/外壳: | 208-LFBGA |

| 供应商设备封装: | 208-CABGA(15x15) |

| 包装: | 托盘 |

| 其它名称: | 70V658S10BF |

�� �

�

�

�IDT70V659/58/57S�

�High-Speed� 3.3V� 128/64/32K� x� 36� Asynchronous� Dual-Port� Static� RAM�

�Industrial� and� Commercial� Temperature� Ranges�

�a� "don't� care".� Likewise,� the� right� port� interrupt� flag� (� INT� R� )� is� asserted� when�

�the� left� port� writes� to� memory� location� 1FFFF� (HEX)� (FFFF� for� IDT70V658�

�and� 7FFF� for� IDT70V657)� and� to� clear� the� interrupt� flag� (� INT� R� ),� the� right�

�port� must� read� the� memory� location� 1FFFF� (FFFF� for� IDT70V658� and�

�7FFF� for� IDT70V657).� The� message� (36� bits)� at� 1FFFE� (FFFE� for�

�IDT70V658� and� 7FFE� for� IDT70V657)or� 1FFFF� (FFFF� for� IDT70V658�

�and� 7FFF� for� IDT70V657)� is� user-defined� since� it� is� an� addressable�

�SRAM� location.� If� the� interrupt� function� is� not� used,� address� locations�

�1FFFE� (FFFE� for� IDT70V658� and� 7FFE� for� IDT70V657)� and� 1FFFF�

�(FFFF� for� IDT70V658� and� 7FFF� for� IDT70V657)� are� not� used� as� mail�

�boxes,� but� as� part� of� the� random� access� memory.� Refer� to� Truth� Table� III�

�for� the� interrupt� operation.�

�Busy� Logic�

�Busy� Logic� provides� a� hardware� indication� that� both� ports� of� the� RAM�

�have� accessed� the� same� location� at� the� same� time.� It� also� allows� one� of� the�

�two� accesses� to� proceed� and� signals� the� other� side� that� the� RAM� is� “Busy”.�

�The� BUSY� pin� can� then� be� used� to� stall� the� access� until� the� operation� on�

�the� other� side� is� completed.� If� a� write� operation� has� been� attempted� from�

�the� side� that� receives� a� BUSY� indication,� the� write� signal� is� gated� internally�

�to� prevent� the� write� from� proceeding.�

�The� use� of� BUSY� logic� is� not� required� or� desirable� for� all� applications.�

�In� some� cases� it� may� be� useful� to� logically� OR� the� BUSY� outputs� together�

�and� use� any� BUSY� indication� as� an� interrupt� source� to� flag� the� event� of�

�an� illegal� or� illogical� operation.� If� the� write� inhibit� function� of� BUSY� logic� is�

�not� desirable,� the� BUSY� logic� can� be� disabled� by� placing� the� part� in� slave�

�mode� with� the� M/� S� pin.� Once� in� slave� mode� the� BUSY� pin� operates� solely�

�as� a� write� inhibit� input� pin.� Normal� operation� can� be� programmed� by� tying�

�the� BUSY� pins� HIGH.� If� desired,� unintended� write� operations� can� be�

�prevented� to� a� port� by� tying� the� BUSY� pin� for� that� port� LOW.�

�The� BUSY� outputs� on� the� IDT70V659/58/57� RAM� in� master� mode,�

�are� push-pull� type� outputs� and� do� not� require� pull� up� resistors� to� operate.�

�If� these� RAMs� are� being� expanded� in� depth,� then� the� BUSY� indication�

�for� the� resulting� array� requires� the� use� of� an� external� AND� gate.�

�number� of� slaves� to� be� addressed� in� the� same� address� range� as� the� master�

�use� the� BUSY� signal� as� a� write� inhibit� signal.� Thus� on� the� IDT70V659/58/�

�57� RAM� the� BUSY� pin� is� an� output� if� the� part� is� used� as� a� master� (M/� S� pin�

�=� V� IH� ),� and� the� BUSY� pin� is� an� input� if� the� part� used� as� a� slave� (M/� S� pin�

�=� V� IL� )� as� shown� in� Figure� 3.�

�If� two� or� more� master� parts� were� used� when� expanding� in� width,� a� split�

�decision� could� result� with� one� master� indicating� BUSY� on� one� side� of� the�

�array� and� another� master� indicating� BUSY� on� one� other� side� of�

�the� array.� This� would� inhibit� the� write� operations� from� one� port� for� part� of�

�a� word� and� inhibit� the� write� operations� from� the� other� port� for� the� other� part�

�of� the� word.�

�The� BUSY� arbitration� on� a� master� is� based� on� the� chip� enable� and�

�address� signals� only.� It� ignores� whether� an� access� is� a� read� or� write.� In�

�a� master/slave� array,� both� address� and� chip� enable� must� be� valid� long�

�enough� for� a� BUSY� flag� to� be� output� from� the� master� before� the� actual� write�

�pulse� can� be� initiated� with� the� R/� W� signal.� Failure� to� observe� this� timing�

�can� result� in� a� glitched� internal� write� inhibit� signal� and� corrupted� data� in� the�

�slave.�

�Semaphores�

�The� IDT70V659/58/57� is� an� extremely� fast� Dual-Port� 128/64/32K� x�

�36� CMOS� Static� RAM� with� an� additional� 8� address� locations� dedicated� to�

�binary� semaphore� flags.� These� flags� allow� either� processor� on� the� left� or�

�right� side� of� the� Dual-Port� RAM� to� claim� a� privilege� over� the� other� processor�

�for� functions� defined� by� the� system� designer’s� software.� As� an� example,�

�the� semaphore� can� be� used� by� one� processor� to� inhibit� the� other� from�

�accessing� a� portion� of� the� Dual-Port� RAM� or� any� other� shared� resource.�

�The� Dual-Port� RAM� features� a� fast� access� time,� with� both� ports� being�

�completely� independent� of� each� other.� This� means� that� the� activity� on� the�

�left� port� in� no� way� slows� the� access� time� of� the� right� port.� Both� ports� are�

�identical� in� function� to� standard� CMOS� Static� RAM� and� can� be� read� from�

�or� written� to� at� the� same� time� with� the� only� possible� conflict� arising� from� the�

�simultaneous� writing� of,� or� a� simultaneous� READ/WRITE� of,� a� non-�

�semaphore� location.� Semaphores� are� protected� against� such� ambiguous�

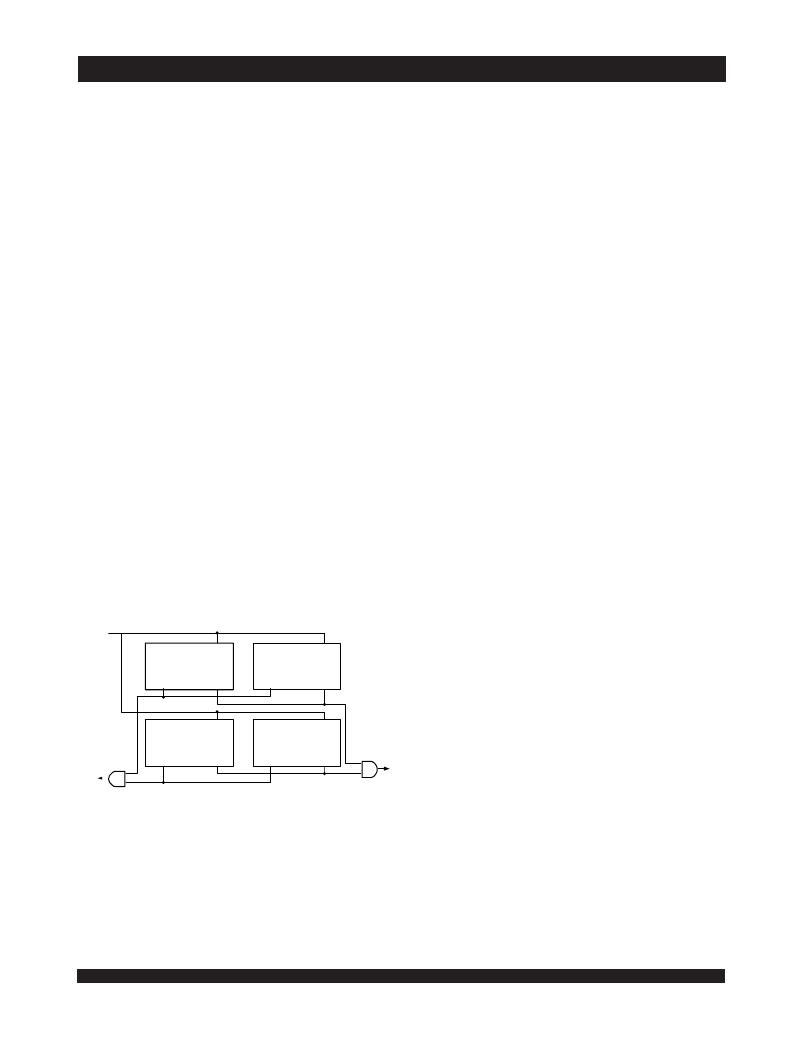

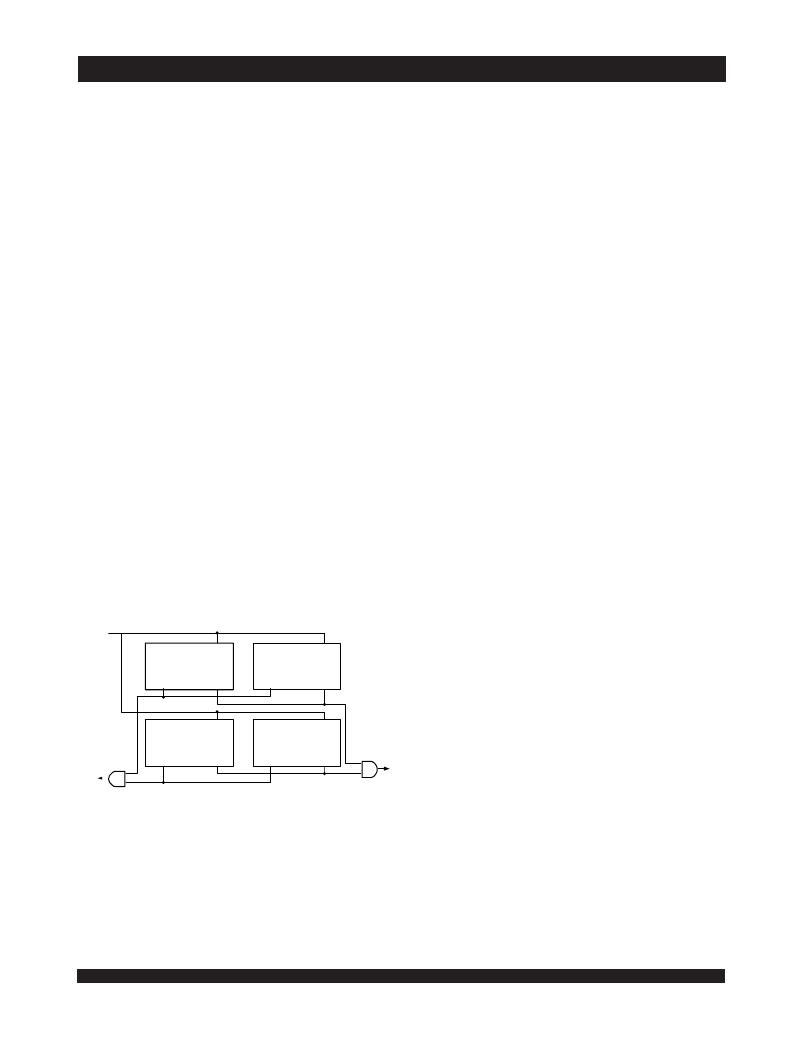

�A� 17(1,2)�

�MASTER� CE� 0�

�Dual� Port� RAM�

�BUSY� L� BUSY� R�

�SLAVE� CE� 0�

�Dual� Port� RAM�

�BUSY� L� BUSY� R�

�situations� and� may� be� used� by� the� system� program� to� avoid� any� conflicts�

�in� the� non-semaphore� portion� of� the� Dual-Port� RAM.� These� devices� have�

�an� automatic� power-down� feature� controlled� by� CE� ,� the� Dual-Port� RAM�

�enable,� and� SEM� ,� the� semaphore� enable.� The� CE� and� SEM� pins� control�

�on-chip� power� down� circuitry� that� permits� the� respective� port� to� go� into�

�standby� mode� when� not� selected.�

�Dual� Port� RAM�

�BUSY� L� BUSY� R�

�MASTER� CE� 1�

�SLAVE� CE� 1�

�Dual� Port� RAM�

�BUSY� L� BUSY� R�

�Systems� which� can� best� use� the� IDT70V659/58/57� contain� multiple�

�processors� or� controllers� and� are� typically� very� high-speed� systems�

�which� are� software� controlled� or� software� intensive.� These� systems�

�can� benefit� from� a� performance� increase� offered� by� the� IDT70V659/58/�

�4869� drw� 18�

�Figure� 3.� Busy� and� chip� enable� routing� for� both� width� and� depth�

�expansion� with� IDT70V659/58/57� RAMs.�

�.�

�57s� hardware� semaphores,� which� provide� a� lockout� mechanism� without�

�requiring� complex� programming.�

�Software� handshaking� between� processors� offers� the� maximum� in�

�NOTES:�

�1.� A� 16� for� IDT70V658.�

�2.� A� 15� for� IDT70V657.�

�Width� Expansion� with� Busy� Logic�

�Master/Slave� Arrays�

�When� expanding� an� IDT70V659/58/57� RAM� array� in� width� while�

�using� BUSY� logic,� one� master� part� is� used� to� decide� which� side� of� the� RAMs�

�array� will� receive� a� BUSY� indication,� and� to� output� that� indication.� Any�

�20�

�system� flexibility� by� permitting� shared� resources� to� be� allocated� in� varying�

�configurations.� The� IDT70V659/58/57� does� not� use� its� semaphore�

�flags� to� control� any� resources� through� hardware,� thus� allowing� the� system�

�designer� total� flexibility� in� system� architecture.�

�An� advantage� of� using� semaphores� rather� than� the� more� common�

�methods� of� hardware� arbitration� is� that� wait� states� are� never� incurred� in�

�either� processor.� This� can� prove� to� be� a� major� advantage� in� very� high-�

�speed� systems.�

�相关PDF资料 |

PDF描述 |

|---|---|

| MPC857DSLZQ66B | IC MPU PWRQUICC 66MHZ 357-PBGA |

| IDT70V639S10BF | IC SRAM 2.25MBIT 10NS 208FBGA |

| IDT70V658S15DR | IC SRAM 2MBIT 15NS 208QFP |

| MPC857DSLCZQ66B | IC MPU PWRQUICC 66MHZ 357-PBGA |

| IDT70V639S15PRF | IC SRAM 2.25MBIT 15NS 128TQFP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| IDT70V658S10BF8 | 功能描述:IC SRAM 2MBIT 10NS 208FBGA RoHS:否 类别:集成电路 (IC) >> 存储器 系列:- 标准包装:3,000 系列:- 格式 - 存储器:EEPROMs - 串行 存储器类型:EEPROM 存储容量:8K (1K x 8) 速度:400kHz 接口:I²C,2 线串口 电源电压:1.7 V ~ 5.5 V 工作温度:-40°C ~ 85°C 封装/外壳:8-SOIC(0.154",3.90mm 宽) 供应商设备封装:8-SOIC 包装:带卷 (TR) |

| IDT70V658S10BFG | 功能描述:IC SRAM 2MBIT 10NS 208FBGA RoHS:是 类别:集成电路 (IC) >> 存储器 系列:- 标准包装:3,000 系列:- 格式 - 存储器:EEPROMs - 串行 存储器类型:EEPROM 存储容量:8K (1K x 8) 速度:400kHz 接口:I²C,2 线串口 电源电压:1.7 V ~ 5.5 V 工作温度:-40°C ~ 85°C 封装/外壳:8-SOIC(0.154",3.90mm 宽) 供应商设备封装:8-SOIC 包装:带卷 (TR) |

| IDT70V658S10BFG8 | 功能描述:IC SRAM 2MBIT 10NS 208FBGA RoHS:是 类别:集成电路 (IC) >> 存储器 系列:- 标准包装:3,000 系列:- 格式 - 存储器:EEPROMs - 串行 存储器类型:EEPROM 存储容量:8K (1K x 8) 速度:400kHz 接口:I²C,2 线串口 电源电压:1.7 V ~ 5.5 V 工作温度:-40°C ~ 85°C 封装/外壳:8-SOIC(0.154",3.90mm 宽) 供应商设备封装:8-SOIC 包装:带卷 (TR) |

| IDT70V658S10DR | 功能描述:IC SRAM 2MBIT 10NS 208QFP RoHS:否 类别:集成电路 (IC) >> 存储器 系列:- 标准包装:3,000 系列:- 格式 - 存储器:EEPROMs - 串行 存储器类型:EEPROM 存储容量:8K (1K x 8) 速度:400kHz 接口:I²C,2 线串口 电源电压:1.7 V ~ 5.5 V 工作温度:-40°C ~ 85°C 封装/外壳:8-SOIC(0.154",3.90mm 宽) 供应商设备封装:8-SOIC 包装:带卷 (TR) |

| IDT70V658S10DRG | 功能描述:IC SRAM 2MBIT 10NS 208QFP RoHS:是 类别:集成电路 (IC) >> 存储器 系列:- 标准包装:3,000 系列:- 格式 - 存储器:EEPROMs - 串行 存储器类型:EEPROM 存储容量:8K (1K x 8) 速度:400kHz 接口:I²C,2 线串口 电源电压:1.7 V ~ 5.5 V 工作温度:-40°C ~ 85°C 封装/外壳:8-SOIC(0.154",3.90mm 宽) 供应商设备封装:8-SOIC 包装:带卷 (TR) |

发布紧急采购,3分钟左右您将得到回复。