- 您现在的位置:买卖IC网 > PDF目录3967 > IDT70V658S10BF (IDT, Integrated Device Technology Inc)IC SRAM 2MBIT 10NS 208FBGA PDF资料下载

参数资料

| 型号: | IDT70V658S10BF |

| 厂商: | IDT, Integrated Device Technology Inc |

| 文件页数: | 21/24页 |

| 文件大小: | 0K |

| 描述: | IC SRAM 2MBIT 10NS 208FBGA |

| 标准包装: | 7 |

| 格式 - 存储器: | RAM |

| 存储器类型: | SRAM - 双端口,异步 |

| 存储容量: | 2M(64K x 36) |

| 速度: | 10ns |

| 接口: | 并联 |

| 电源电压: | 3.15 V ~ 3.45 V |

| 工作温度: | 0°C ~ 70°C |

| 封装/外壳: | 208-LFBGA |

| 供应商设备封装: | 208-CABGA(15x15) |

| 包装: | 托盘 |

| 其它名称: | 70V658S10BF |

�� �

�

�

�IDT70V659/58/57S�

�High-Speed� 3.3V� 128/64/32K� x� 36� Asynchronous� Dual-Port� Static� RAM�

�Industrial� and� Commercial� Temperature� Ranges�

�How� the� Semaphore� Flags� Work�

�The� semaphore� logic� is� a� set� of� eight� latches� which� are� independent�

�of� the� Dual-Port� RAM.� These� latches� can� be� used� to� pass� a� flag,� or� token,�

�from� one� port� to� the� other� to� indicate� that� a� shared� resource�

�is� in� use.� The� semaphores� provide� a� hardware� assist� for� a� use� assignment�

�method� called� “Token� Passing� Allocation.”� In� this� method,� the� state� of� a�

�semaphore� latch� is� used� as� a� token� indicating� that� a� shared� resource� is�

�in� use.� If� the� left� processor� wants� to� use� this� resource,� it� requests� the� token�

�by� setting� the� latch.� This� processor� then� verifies� its� success� in� setting� the�

�latch� by� reading� it.� If� it� was� successful,� it� proceeds� to� assume� control� over�

�the� shared� resource.� If� it� was� not� successful� in� setting� the� latch,� it� determines�

�that� the� right� side� processorhas� set� the� latch� first,� has� the� token� and� is� using�

�the� shared� resource.� The� left� processor� can� then� either� repeatedly� request�

�that� semaphore’s� status� or� remove� its� request� for� that� semaphore� to�

�perform� another� task� and� occasionally� attempt� again� to� gain� control� of� the�

�token� via� the� set� and� test� sequence.� Once� the� right� side� has� relinquished�

�the� token,� the� left� side� should� succeed� in� gaining� control.�

�The� semaphore� flags� are� active� LOW.� A� token� is� requested� by� writing�

�a� zero� into� a� semaphore� latch� and� is� released� when� the� same� side� writes�

�a� one� to� that� latch.�

�The� eight� semaphore� flags� reside� within� the� IDT70V659/58/57� in� a�

�request� latch� will� contain� a� zero,� yet� the� semaphore� flag� will� appear� as� one,�

�a� fact� which� the� processor� will� verify� by� the� subsequent� read� (see� Table�

�V).� As� an� example,� assume� a� processor� writes� a� zero� to� the� left� port� at� a�

�free� semaphore� location.� On� used� instead,� system� contention� problems�

�could� have� occurred� during� the� gap� between� the� read� and� write� cycles.�

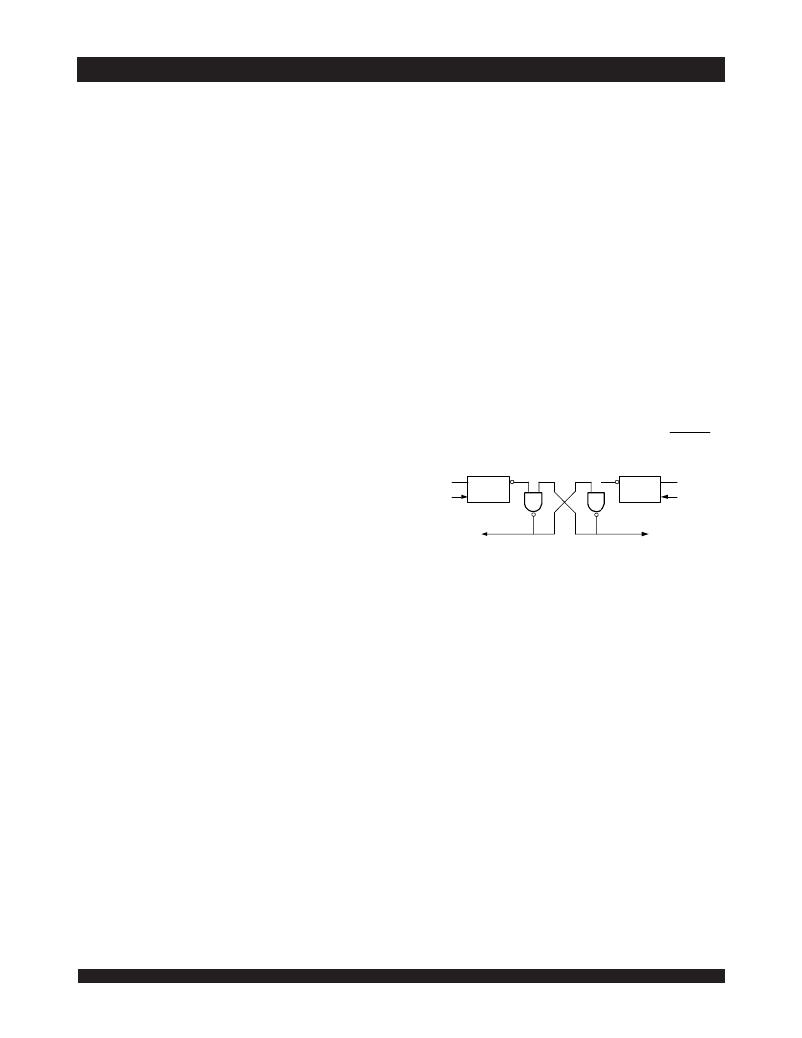

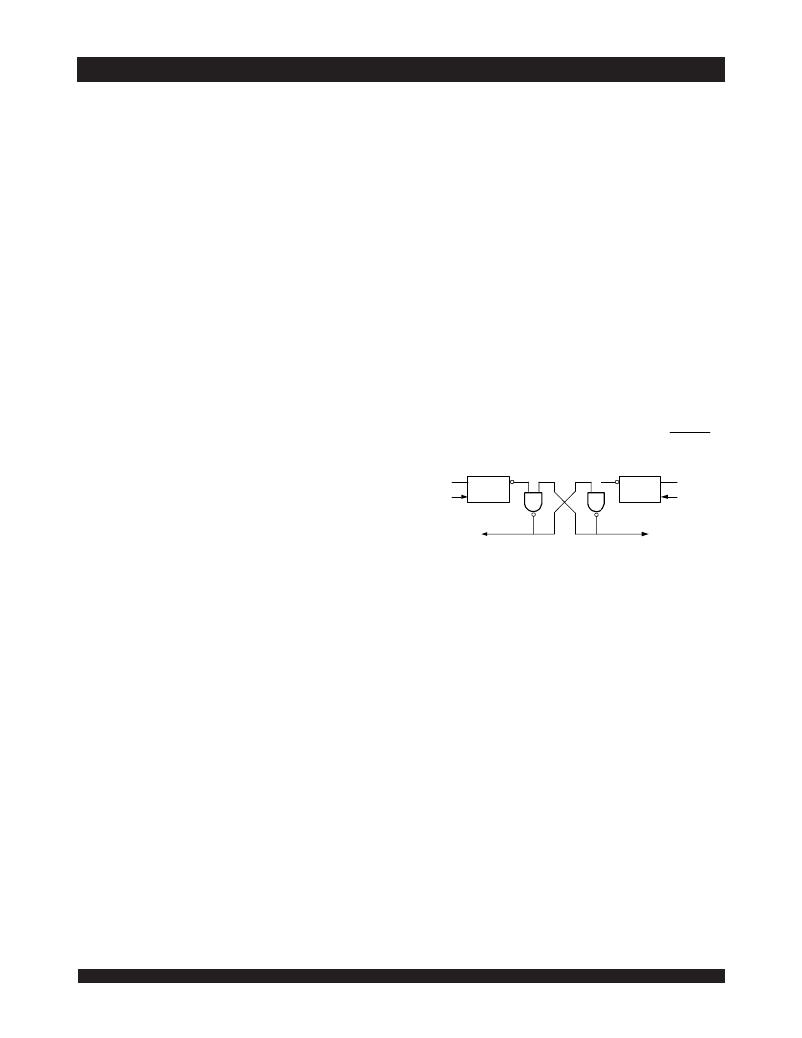

�It� is� important� to� note� that� a� failed� semaphore� request� must� be� followed�

�by� either� repeated� reads� or� by� writing� a� one� into� the� same� location.� The�

�reason� for� this� is� easily� understood� by� looking� at� the� simple� logic� diagram�

�of� the� semaphore� flag� in� Figure� 4.� Two� semaphore� request� latches� feed�

�into� a� semaphore� flag.� Whichever� latch� is� first� to� present� a� zero� to� the�

�semaphore� flag� will� force� its� side� of� the� semaphore� flag� LOW� and� the� other�

�side� HIGH.� This� condition� will� continue� until� a� one� is� written� to� the� same�

�semaphore� request� latch.� Should� the� other� side’s� semaphore� request� latch�

�have� been� written� to� a� zero� in� the� meantime,� the� semaphore� flag� will� flip�

�over� to� the� other� side� as� soon� as� a� one� is� written� into� the� first� side’s� request�

�latch.� The� second� side’s� flag� will� now� stay� LOW� until� its� semaphore� request�

�latch� is� written� to� a� one.� From� this� it� is� easy� to� understand� that,� if� a� semaphore�

�is� requested� and� the� processor� which� requested� it� no� longer� needs� the�

�resource,� the� entire� system� can� hang� up� until� a� one� is� written� into� that�

�semaphore� request� latch.�

�separate� memory� space� from� the� Dual-Port� RAM.� This� address� space� is�

�accessed� by� placing� a� low� input� on� the� SEM� pin� (which� acts� as� a� chip� select�

�for� the� semaphore� flags)� and� using� the� other� control� pins� (Address,� CE� ,�

�R/� W� and� BE� o)� as� they� would� be� used� in� accessing� a� standard� Static� RAM.�

�L� PORT�

�SEMAPHORE�

�REQUEST� FLIP� FLOP�

�R� PORT�

�SEMAPHORE�

�REQUEST� FLIP� FLOP�

�Each� of� the� flags� has� a� unique� address� which� can� be� accessed� by� either�

�D� 0�

�D�

�Q�

�Q�

�D�

�D� 0�

�side� through� address� pins� A� 0� –� A� 2� .� When� accessing� the� semaphores,� none�

�of� the� other� address� pins� has� any� effect.�

�When� writing� to� a� semaphore,� only� data� pin� D� 0� is� used.� If� a� low� level�

�is� written� into� an� unused� semaphore� location,� that� flag� will� be� set� to� a� zero�

�WRITE�

�SEMAPHORE�

�READ�

�WRITE�

�SEMAPHORE�

�READ�

�on� that� side� and� a� one� on� the� other� side� (see� Truth� Table� V).� That�

�semaphore� can� now� only� be� modified� by� the� side� showing� the� zero.� When�

�Figure� 4.� IDT70V659/58/57� Semaphore� Logic�

�4869� drw� 19�

�a� one� is� written� into� the� same� location� from� the� same� side,� the� flag� will� be�

�set� to� a� one� for� both� sides� (unless� a� semaphore� request� from� the� other� side�

�is� pending)� and� then� can� be� written� to� by� both� sides.� The� fact� that� the� side�

�which� is� able� to� write� a� zero� into� a� semaphore� subsequently� locks� out� writes�

�from� the� other� side� is� what� makes� semaphore� flags� useful� in� interprocessor�

�communications.� (A� thorough� discussion� on� the� use� of� this� feature� follows�

�shortly.)� A� zero� written� into� the� same� location� from� the� other� side� will� be�

�stored� in� the� semaphore� request� latch� for� that� side� until� the� semaphore� is�

�freed� by� the� first� side.�

�When� a� semaphore� flag� is� read,� its� value� is� spread� into� all� data� bits� so�

�that� a� flag� that� is� a� one� reads� as� a� one� in� all� data� bits� and� a� flag� containing�

�a� zero� reads� as� all� zeros.� The� read� value� is� latched� into� one� side’s� output�

�register� when� that� side's� semaphore� select� (� SEM� ,� BE� n)� and� output� enable�

�(� OE� )� signals� go� active.� This� serves� to� disallow� the� semaphore� from�

�changing� state� in� the� middle� of� a� read� cycle� due� to� a� write� cycle� from� the�

�other� side.� Because� of� this� latch,� a� repeated� read� of� a� semaphore� in� a� test�

�loop� must� cause� either� signal� (� SEM� or� OE� )� to� go� inactive� or� the� output� will�

�never� change.� However,� during� reads� BE� n� functions� only� as� an� output�

�for� semaphore.� It� does� not� have� any� influence� on� the� semaphore� control�

�logic.�

�A� sequence� WRITE/READ� must� be� used� by� the� semaphore� in� order�

�to� guarantee� that� no� system� level� contention� will� occur.� A� processor�

�requests� access� to� shared� resources� by� attempting� to� write� a� zero� into� a�

�semaphore� location.� If� the� semaphore� is� already� in� use,� the� semaphore�

�21�

�The� critical� case� of� semaphore� timing� is� when� both� sides� request� a�

�single� token� by� attempting� to� write� a� zero� into� it� at� the� same� time.� The�

�semaphore� logic� is� specially� designed� to� resolve� this� problem.� If� simulta-�

�neous� requests� are� made,� the� logic� guarantees� that� only� one� side� receives�

�the� token.� If� one� side� is� earlier� than� the� other� in� making� the� request,� the� first�

�side� to� make� the� request� will� receive� the� token.� If� both� requests� arrive� at�

�the� same� time,� the� assignment� will� be� arbitrarily� made� to� one� port� or� the�

�other.�

�One� caution� that� should� be� noted� when� using� semaphores� is� that�

�semaphores� alone� do� not� guarantee� that� access� to� a� resource� is� secure.�

�As� with� any� powerful� programming� technique,� if� semaphores� are� misused�

�or� misinterpreted,� a� software� error� can� easily� happen.�

�Initialization� of� the� semaphores� is� not� automatic� and� must� be� handled�

�via� the� initialization� program� at� power-up.� Since� any� semaphore� request�

�flag� which� contains� a� zero� must� be� reset� to� a� one,� all� semaphores� on� both�

�sides� should� have� a� one� written� into� them� at� initialization� from� both� sides�

�to� assure� that� they� will� be� free� when� needed.�

�相关PDF资料 |

PDF描述 |

|---|---|

| MPC857DSLZQ66B | IC MPU PWRQUICC 66MHZ 357-PBGA |

| IDT70V639S10BF | IC SRAM 2.25MBIT 10NS 208FBGA |

| IDT70V658S15DR | IC SRAM 2MBIT 15NS 208QFP |

| MPC857DSLCZQ66B | IC MPU PWRQUICC 66MHZ 357-PBGA |

| IDT70V639S15PRF | IC SRAM 2.25MBIT 15NS 128TQFP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| IDT70V658S10BF8 | 功能描述:IC SRAM 2MBIT 10NS 208FBGA RoHS:否 类别:集成电路 (IC) >> 存储器 系列:- 标准包装:3,000 系列:- 格式 - 存储器:EEPROMs - 串行 存储器类型:EEPROM 存储容量:8K (1K x 8) 速度:400kHz 接口:I²C,2 线串口 电源电压:1.7 V ~ 5.5 V 工作温度:-40°C ~ 85°C 封装/外壳:8-SOIC(0.154",3.90mm 宽) 供应商设备封装:8-SOIC 包装:带卷 (TR) |

| IDT70V658S10BFG | 功能描述:IC SRAM 2MBIT 10NS 208FBGA RoHS:是 类别:集成电路 (IC) >> 存储器 系列:- 标准包装:3,000 系列:- 格式 - 存储器:EEPROMs - 串行 存储器类型:EEPROM 存储容量:8K (1K x 8) 速度:400kHz 接口:I²C,2 线串口 电源电压:1.7 V ~ 5.5 V 工作温度:-40°C ~ 85°C 封装/外壳:8-SOIC(0.154",3.90mm 宽) 供应商设备封装:8-SOIC 包装:带卷 (TR) |

| IDT70V658S10BFG8 | 功能描述:IC SRAM 2MBIT 10NS 208FBGA RoHS:是 类别:集成电路 (IC) >> 存储器 系列:- 标准包装:3,000 系列:- 格式 - 存储器:EEPROMs - 串行 存储器类型:EEPROM 存储容量:8K (1K x 8) 速度:400kHz 接口:I²C,2 线串口 电源电压:1.7 V ~ 5.5 V 工作温度:-40°C ~ 85°C 封装/外壳:8-SOIC(0.154",3.90mm 宽) 供应商设备封装:8-SOIC 包装:带卷 (TR) |

| IDT70V658S10DR | 功能描述:IC SRAM 2MBIT 10NS 208QFP RoHS:否 类别:集成电路 (IC) >> 存储器 系列:- 标准包装:3,000 系列:- 格式 - 存储器:EEPROMs - 串行 存储器类型:EEPROM 存储容量:8K (1K x 8) 速度:400kHz 接口:I²C,2 线串口 电源电压:1.7 V ~ 5.5 V 工作温度:-40°C ~ 85°C 封装/外壳:8-SOIC(0.154",3.90mm 宽) 供应商设备封装:8-SOIC 包装:带卷 (TR) |

| IDT70V658S10DRG | 功能描述:IC SRAM 2MBIT 10NS 208QFP RoHS:是 类别:集成电路 (IC) >> 存储器 系列:- 标准包装:3,000 系列:- 格式 - 存储器:EEPROMs - 串行 存储器类型:EEPROM 存储容量:8K (1K x 8) 速度:400kHz 接口:I²C,2 线串口 电源电压:1.7 V ~ 5.5 V 工作温度:-40°C ~ 85°C 封装/外壳:8-SOIC(0.154",3.90mm 宽) 供应商设备封装:8-SOIC 包装:带卷 (TR) |

发布紧急采购,3分钟左右您将得到回复。