- 您现在的位置:买卖IC网 > PDF目录10015 > IDT72V3631L20PF8 (IDT, Integrated Device Technology Inc)IC SYNCFIFO 512X36 20NS 120-TQFP PDF资料下载

参数资料

| 型号: | IDT72V3631L20PF8 |

| 厂商: | IDT, Integrated Device Technology Inc |

| 文件页数: | 21/21页 |

| 文件大小: | 0K |

| 描述: | IC SYNCFIFO 512X36 20NS 120-TQFP |

| 标准包装: | 750 |

| 系列: | 72V |

| 功能: | 异步,同步 |

| 存储容量: | 18.4K(512 x 36) |

| 数据速率: | 520Mbs |

| 访问时间: | 20ns |

| 电源电压: | 3 V ~ 3.6 V |

| 工作温度: | 0°C ~ 70°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 120-LQFP |

| 供应商设备封装: | 120-TQFP(14x14) |

| 包装: | 带卷 (TR) |

| 其它名称: | 72V3631L20PF8 |

9

COMMERCIALTEMPERATURERANGE

IDT72V3631/72V3641/72V3651

3.3V CMOS SYNCFIFO 512 x 36, 1,024 x 36 and 2,048 x 36

is complete, the X and Y register values are loaded bitwise through the FS0/

SD input on each LOW-to-HIGH transition of CLKA that the FS1/

SENinputis

LOW. Thereare18-,20-,or22-bitwritesneededtocompletetheprogramming

for the IDT72V3631, IDT72V3641, or IDT72V3651, respectively. The first-bit

write stores the most significant bit of the Y register, and the last-bit write stores

theleastsignificantbitoftheXregister. Eachregistervaluecanbeprogrammed

from 1 to 508 (IDT72V3631), 1 to 1,020 (IDT72V3641), or 1 to 2,044

(IDT72V3651).

When the option to program the Offset registers serially is chosen, the Input

Ready (IR) flag remains LOW until all register bits are written. The IR flag is set

HIGHbytheLOW-to-HIGHtransitionofCLKAafterthelastbitisloadedtoallow

normal FIFO operation. The timing diagram for serial load of offset registers

can be found in Figure 4.

FIFO WRITE/READ OPERATION

Thestateoftheport-Adata(A0-A35)outputsiscontrolledbytheport-AChip

Select (

CSA) and the port-A Write/Read select (W/RA). TheA0-A35outputs

are in the high-impedance state when either

CSA or W/RA is HIGH. The A0-

A35 outputs are active when both

CSA and W/RA are LOW.

Data is loaded into the FIFO from the A0-A35 inputs on a LOW-to-HIGH

transition of CLKA when

CSA and the port-A Mailbox select (MBA) are LOW,

W/

RA, the port-A Enable (ENA), and the Input Ready (IR) flag are HIGH (see

Table 2). Writes to the FIFO are independent of any concurrent FIFO read.

For the Write Cycle Timing diagram, see Figure 5.

The port-B control signals are identical to those of port-A with the exception

thattheport-BWrite/Readselect(

W/RB)istheinverseoftheport-AWrite/Read

select (W/

RA). The state of the port-B data (B0-B35) outputs is controlled by

the port-B Chip Select (

CSB) and the port-B Write/Read select (W/RB). The

B0-B35 outputs are in the high-impedance state when either

CSB is HIGH or

W/RB is LOW. The B0-B35 outputs are active when CSB is LOW and W/RB

is HIGH.

DataisreadfromtheFIFOtoitsoutputregisteronaLOW-to-HIGHtransition

of CLKB when

CSBandtheport-BMailboxselect(MBB)areLOW,W/RB,the

port-B Enable (ENB), and the Output Ready (OR) flag are HIGH (see Table

3). Reads from the FIFO are independent of any concurrent FIFO writes. For

the Read Cycle Timing diagram, see Figure 6.

Thesetup-andhold-timeconstraintstotheportclocksfortheportChipSelects

andWrite/Readselectsareonlyforenablingwriteandreadoperationsandare

notrelatedtohigh-impedancecontrolofthedataoutputs. IfaportEnableisLOW

during a clock cycle, the port Chip Select and Write/Read select may change

states during the setup- and hold time window of the cycle.

WhentheORflagisLOW,thenextdatawordissenttotheFIFOoutputregister

automaticallybytheCLKBLOW-to-HIGHtransitionthatsetstheORflagHIGH.

WhenORisHIGH,anavailabledatawordisclockedtotheFIFOoutputregister

onlywhenaFIFOreadisselectedbytheport-BChipSelect(

CSB),Write/Read

select (

W/RB), Enable (ENB), and Mailbox select (MBB).

SIGNAL DESCRIPTION

RESET

The IDT72V3631/72V3641/72V3651 is reset by taking the Reset (

RST)

input LOW for at least four port-A Clock (CLKA) and four port-B (CLKB) LOW-

to-HIGHtransitions. TheResetinputmayswitchasynchronouslytotheclocks.

AresetinitializesthememoryreadandwritepointersandforcestheInputReady

(IR) flag LOW, the Output Ready (OR) flag LOW, the Almost-Empty (

AE)flag

LOW,andtheAlmost-Full(

AF)flagHIGH. Resettingthedevicealsoforcesthe

Mailbox Flags (

MBF1,MBF2)HIGH. AfteraFIFOisreset,itsInputReadyflag

is set HIGH after at least two clock cycles to begin normal operation. A FIFO

must be reset after power up before data is written to its memory. The relevant

FIFO Reset timing diagram can be found in Figure 2.

FIRST WORD FALL THROUGH MODE (FWFT)

These devices operate in the First Word Fall Through mode (FWFT). This

mode uses the Output Ready function (OR) to indicate whether or not there is

validdataatthedataoutputs(B0-B35).ItalsousestheInputReady(IR)function

to indicate whether or not the FIFO memory has any free space for writing. In

the FWFT mode, the first word written to an empty FIFO goes directly to data

outputs, no read request necessary. Subsequent words must be accessed by

performing a formal read operation.

ALMOST-EMPTYFLAGANDALMOST-FULLFLAGOFFSETPROGRAM-

MING

TworegistersinthesedevicesareusedtoholdtheoffsetvaluesfortheAlmost-

Empty and Almost-Full flags. The Almost-Empty (

AE) flag Offset register is

labeled X, and the Almost-Full (

AF)flagOffsetregisterislabeledY. TheOffset

register can be loaded with a value in three ways: one of two preset values are

loadedintotheOffsetregisters,parallelloadfromportA,orserialload. TheOffset

registerprogrammingmodeischosenbytheflagselect(FS1,FS0)inputsduring

a LOW-to-HIGH transition on the

RST input (See Table 1).

—

PRESET VALUES

If the preset value of 8 or 64 is chosen by the FS1 and FS0 inputs at the time

of a

RST LOW-to-HIGH transition according to Table 1, the preset value is

automatically loaded into the X and Y registers. No other device initialization is

necessarytobeginnormaloperation,andtheIRflagissetHIGHaftertwoLOW-

to-HIGHtransitionsonCLKA.ForthePresetvalueloadingtimingdiagram,see

Figure 2.

—

PARALLEL LOAD FROM PORT A

To program the X and Y registers from port A, the device is reset with FS0

and FS1 LOW during the LOW-to-HIGH transition of

RST. After this reset is

complete, the IR flag is set HIGH after two LOW-to-HIGH transitions on CLKA.

ThefirsttwowritestotheFIFOdonotstoredatainitsmemorybutloadtheOffset

registersintheorderY,X. EachOffsetregisteroftheIDT72V3631,IDT72V3641,

and IDT72V3651 uses port-A inputs (A8-A0), (A9-A0), and (A10-A0),

respectively. Thehighestnumberinputisusedasthemostsignificantbitofthe

binary number in each case. Each register value can be programmed from 1

to508(IDT72V3631),1to1,020(IDT72V3641),and1to2,044(IDT72V3651).

AfterbothOffsetregistersareprogrammedfromportA,subsequentFIFOwrites

store data in the RAM. The timing diagram for parallel load of offset registers

can be found in Figure 3.

—

SERIAL LOAD

To program the X and Y registers serially, the device is reset with FS0/SD

andFS1/

SENHIGHduringtheLOW-to-HIGHtransitionofRST. Afterthisreset

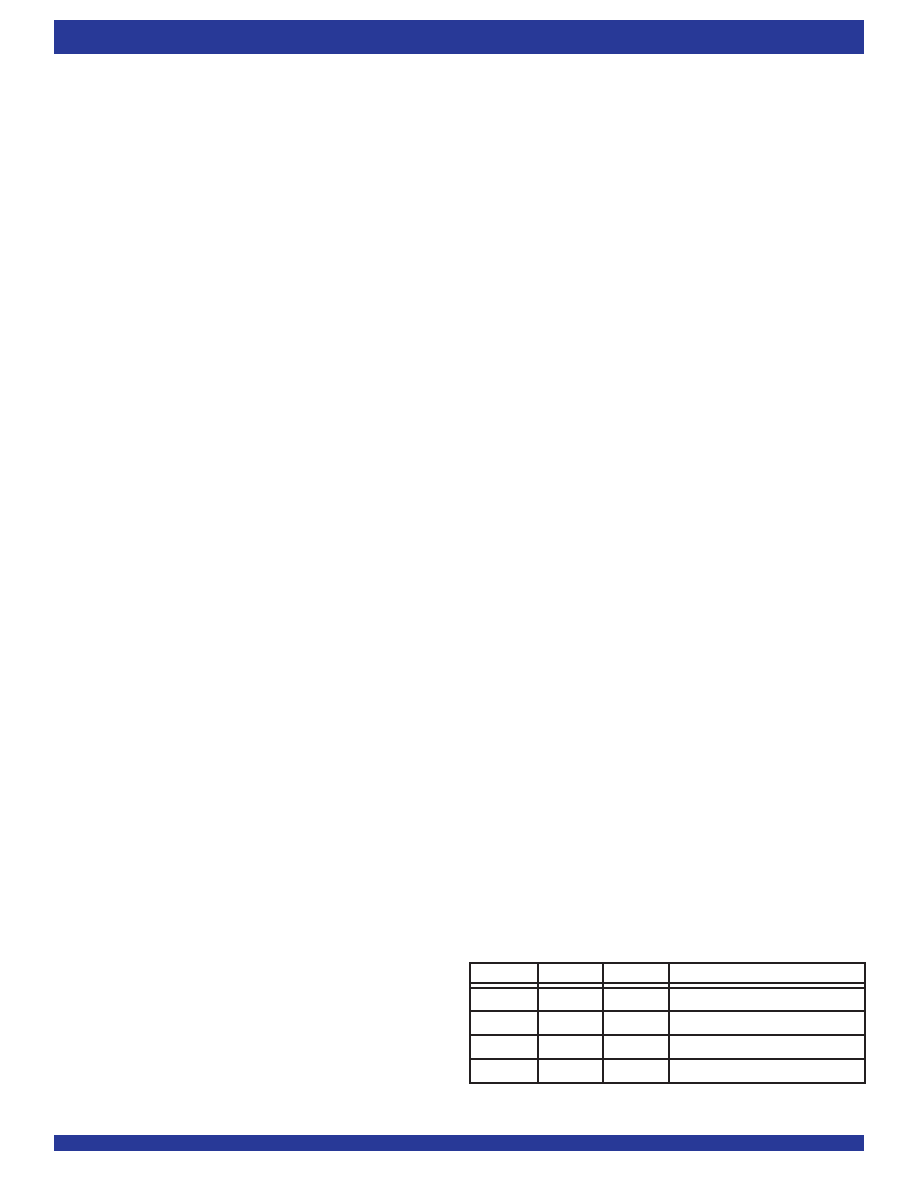

NOTE:

1. X register holds the offset for

AE; Y register holds the offset for AF.

FS1

FS0

RST

X and Y Registers (1)

HH

↑

Serial Load

HL

↑

64

LH

↑

8

LL

↑

Parallel Load From Port A

TABLE 1 —

—

— FLAG PROGRAMMING

相关PDF资料 |

PDF描述 |

|---|---|

| VI-21W-IU-F1 | CONVERTER MOD DC/DC 5.5V 200W |

| MS27467E17B55PC | CONN PLUG 55POS STRAIGHT W/PINS |

| VI-21V-IU-F1 | CONVERTER MOD DC/DC 5.8V 200W |

| IDT72V3622L10PF8 | IC BIFIFO 256X36X2 10NS 120-TQFP |

| MS27467E17B55PD | CONN PLUG 55POS STRAIGHT W/PINS |

相关代理商/技术参数 |

参数描述 |

|---|---|

| IDT72V3631L20PQF | 功能描述:IC SYNCFIFO 512X36 20NS 132-PQFP RoHS:否 类别:集成电路 (IC) >> 逻辑 - FIFO 系列:72V 标准包装:90 系列:7200 功能:同步 存储容量:288K(16K x 18) 数据速率:100MHz 访问时间:10ns 电源电压:4.5 V ~ 5.5 V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:64-LQFP 供应商设备封装:64-TQFP(14x14) 包装:托盘 其它名称:72271LA10PF |

| IDT72V3632L10PF | 功能描述:IC BIFIFO 512X36X2 10NS 120-TQFP RoHS:否 类别:集成电路 (IC) >> 逻辑 - FIFO 系列:72V 标准包装:90 系列:7200 功能:同步 存储容量:288K(16K x 18) 数据速率:100MHz 访问时间:10ns 电源电压:4.5 V ~ 5.5 V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:64-LQFP 供应商设备封装:64-TQFP(14x14) 包装:托盘 其它名称:72271LA10PF |

| IDT72V3632L10PF8 | 功能描述:IC BIFIFO 512X36X2 10NS 120-TQFP RoHS:否 类别:集成电路 (IC) >> 逻辑 - FIFO 系列:72V 标准包装:90 系列:7200 功能:同步 存储容量:288K(16K x 18) 数据速率:100MHz 访问时间:10ns 电源电压:4.5 V ~ 5.5 V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:64-LQFP 供应商设备封装:64-TQFP(14x14) 包装:托盘 其它名称:72271LA10PF |

| IDT72V3632L10PFG | 制造商:Integrated Device Technology Inc 功能描述:IC FIFO 512X36X2 SYNC 120TQFP |

| IDT72V3632L10PFG8 | 制造商:Integrated Device Technology Inc 功能描述:IC FIFO 512X36X2 SYNC 120TQFP |

发布紧急采购,3分钟左右您将得到回复。