- 您现在的位置:买卖IC网 > PDF目录10015 > IDT72V3632L15PF8 (IDT, Integrated Device Technology Inc)IC BIFIFO 512X36X2 15NS 120-TQFP PDF资料下载

参数资料

| 型号: | IDT72V3632L15PF8 |

| 厂商: | IDT, Integrated Device Technology Inc |

| 文件页数: | 25/29页 |

| 文件大小: | 0K |

| 描述: | IC BIFIFO 512X36X2 15NS 120-TQFP |

| 标准包装: | 750 |

| 系列: | 72V |

| 功能: | 异步,同步 |

| 存储容量: | 36.8K(512 x 36 x 2) |

| 数据速率: | 67MHz |

| 访问时间: | 15ns |

| 电源电压: | 3 V ~ 3.6 V |

| 工作温度: | 0°C ~ 70°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 120-LQFP |

| 供应商设备封装: | 120-TQFP(14x14) |

| 包装: | 带卷 (TR) |

| 其它名称: | 72V3632L15PF8 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页当前第25页第26页第27页第28页第29页

5

COMMERCIAL TEMPERATURERANGE

IDT72V3622/72V3632/72V3642 CMOS 3.3V SyncBiFIFOTM

256 x 36 x 2, 512 x 36 x 2, 1,024 x 36 x 2

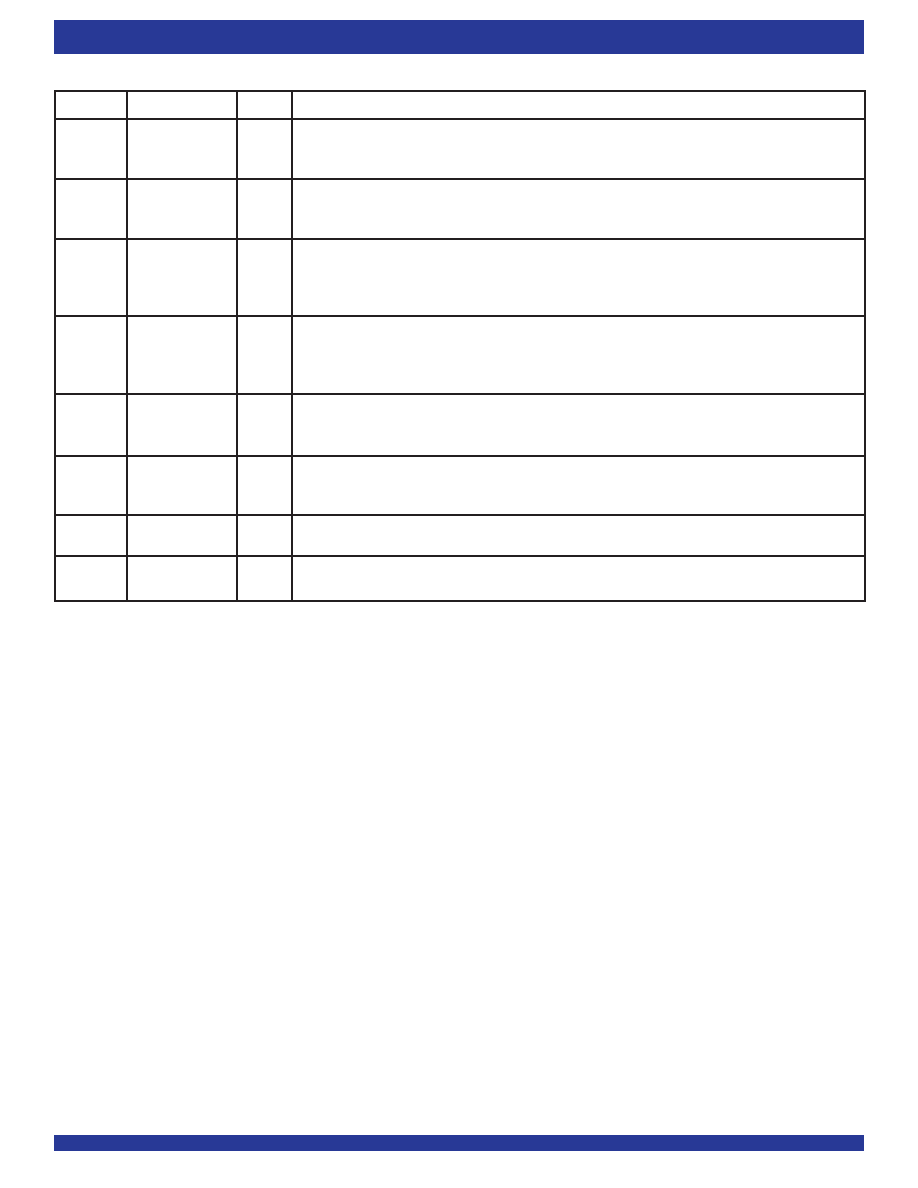

Symbol

Name

I/O

Description

MBA

Port A Mailbox

I

A HIGH level on MBA chooses a mailbox register for a port A read or write operation. When the

Select

A0-A35 outputs are active, a HIGH level on MBA selects data from the mail2 register for output and a

LOWlevelselectsFIFO2outputregisterdataforoutput.

MBB

Port B Mailbox

I

A HIGH level on MBB chooses a mailbox register for a port B read or write operation. When the

Select

B0-B35 outputs are active, a HIGH level on MBB selects data from the mail1 register or output and a

LOWlevelselectsFIFO1outputregisterdataforoutput.

MBF1

Mail1Register

O

MBF1 is set LOW by a LOW-to-HIGH transition of CLKA that writes data to the mail1 register.

Flag

Writes to the mail1 register are inhibited while MBF1 is LOW. MBF1 is set HIGH by a LOW-to-HIGH

transition of CLKB when a port B read is selected and MBB is HIGH. MBF1 is set HIGH when FIFO1

isreset.

MBF2

Mail2Register

O

MBF2 is set LOW by a LOW-to-HIGH transition of CLKB that writes data to the mail2 register. Writes

Flag

to the mail2 register are inhibited while MBF2 is LOW. MBF2 is set HIGH by a LOW-to-HIGH

transition of CLKA when a port A read is selected and MBA is HIGH. MBF2 is also set HIGH when

FIFO2 is reset.

RST1

FIFO1Reset

I

ToresetFIFO1,fourLOW-to-HIGHtransitionsofCLKAandfourLOW-to-HIGHtransitionsofCLKBmust

occur while RST1 is LOW. The LOW-to-HIGH transition of RST1 latches the status of FS0 and FS1 for

AFA and AEB offset selection. FIFO1 must be reset upon power up before data is written to its RAM.

RST2

FIFO2Reset

I

ToresetFIFO2,fourLOW-to-HIGHtransitionsofCLKAandfourLOW-to-HIGHtransitionsofCLKBmust

occur while RST2 is LOW. The LOW-to-HIGH transition of RST2 latches the status of FS0 and FS1 for

AFB and AEA offset selection. FIFO2 must be reset upon power up before data is written to its RAM.

W/RA

PortAWrite/

I

A HIGH selects a write operation and a LOW selects a read operation on port A for a LOW-to-HIGH

ReadSelect

transition of CLKA. The A0-A35 outputs are in the HIGH impedance state when W/RA is HIGH.

W/RB

PortBWrite/

I

A LOW selects a write operation and a HIGH selects a read operation on port B for a LOW-to-HIGH

ReadSelect

transition of CLKB. The B0-B35 outputs are in the HIGH impedance state when W/RB is LOW.

PIN DESCRIPTIONS (CONTINUED)

相关PDF资料 |

PDF描述 |

|---|---|

| VE-B33-MX-B1 | CONVERTER MOD DC/DC 24V 75W |

| VE-24W-IU-F2 | CONVERTER MOD DC/DC 5.5V 200W |

| ADM2587EBRWZ-REEL7 | IC TXRX RS485 ISOLATED 20SOIC |

| IDT72V3631L20PF8 | IC SYNCFIFO 512X36 20NS 120-TQFP |

| VI-21W-IU-F1 | CONVERTER MOD DC/DC 5.5V 200W |

相关代理商/技术参数 |

参数描述 |

|---|---|

| IDT72V3632L15PFGI | 制造商:Integrated Device Technology Inc 功能描述:IC FIFO 512X36X2 SYNC 120TQFP |

| IDT72V3632L15PFGI8 | 制造商:Integrated Device Technology Inc 功能描述:IC FIFO 512X36X2 SYNC 120TQFP |

| IDT72V3632L15PQF | 功能描述:IC BIFIFO 512X36X2 15NS 132-PQFP RoHS:否 类别:集成电路 (IC) >> 逻辑 - FIFO 系列:72V 标准包装:90 系列:7200 功能:同步 存储容量:288K(16K x 18) 数据速率:100MHz 访问时间:10ns 电源电压:4.5 V ~ 5.5 V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:64-LQFP 供应商设备封装:64-TQFP(14x14) 包装:托盘 其它名称:72271LA10PF |

| IDT72V3633L10PF | 功能描述:IC FIFO SYNC 512X36 10NS 128TQFP RoHS:否 类别:集成电路 (IC) >> 逻辑 - FIFO 系列:72V 标准包装:90 系列:7200 功能:同步 存储容量:288K(16K x 18) 数据速率:100MHz 访问时间:10ns 电源电压:4.5 V ~ 5.5 V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:64-LQFP 供应商设备封装:64-TQFP(14x14) 包装:托盘 其它名称:72271LA10PF |

| IDT72V3633L10PF8 | 功能描述:IC FIFO SYNC 512X36 10NS 128TQFP RoHS:否 类别:集成电路 (IC) >> 逻辑 - FIFO 系列:72V 标准包装:90 系列:7200 功能:同步 存储容量:288K(16K x 18) 数据速率:100MHz 访问时间:10ns 电源电压:4.5 V ~ 5.5 V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:64-LQFP 供应商设备封装:64-TQFP(14x14) 包装:托盘 其它名称:72271LA10PF |

发布紧急采购,3分钟左右您将得到回复。