- 您现在的位置:买卖IC网 > PDF目录9970 > IDT82V2048BB (IDT, Integrated Device Technology Inc)IC LIU T1/E1 8CH SHORT 160-BGA PDF资料下载

参数资料

| 型号: | IDT82V2048BB |

| 厂商: | IDT, Integrated Device Technology Inc |

| 文件页数: | 39/62页 |

| 文件大小: | 0K |

| 描述: | IC LIU T1/E1 8CH SHORT 160-BGA |

| 标准包装: | 14 |

| 类型: | 线路接口装置(LIU) |

| 规程: | E1 |

| 电源电压: | 3.13 V ~ 3.47 V |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 160-BGA |

| 供应商设备封装: | 160-PBGA(15x15) |

| 包装: | 托盘 |

| 其它名称: | 82V2048BB |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页当前第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页

44

IDT82V2048 OCTAL T1/E1 SHORT HAUL LINE INTERFACE UNIT

INDUSTRIAL TEMPERATURE RANGES

4.3

TEST ACCESS PORT CONTROLLER

The TAP controller is a 16-state synchronous state machine. Figure-

26 shows its state diagram A description of each state follows. Note that

the figure contains two main branches to access either the data or

instruction registers. The value shown next to each state transition in

this figure states the value present at TMS at each rising edge of TCK.

Refer to Table-22 for details of the state description.

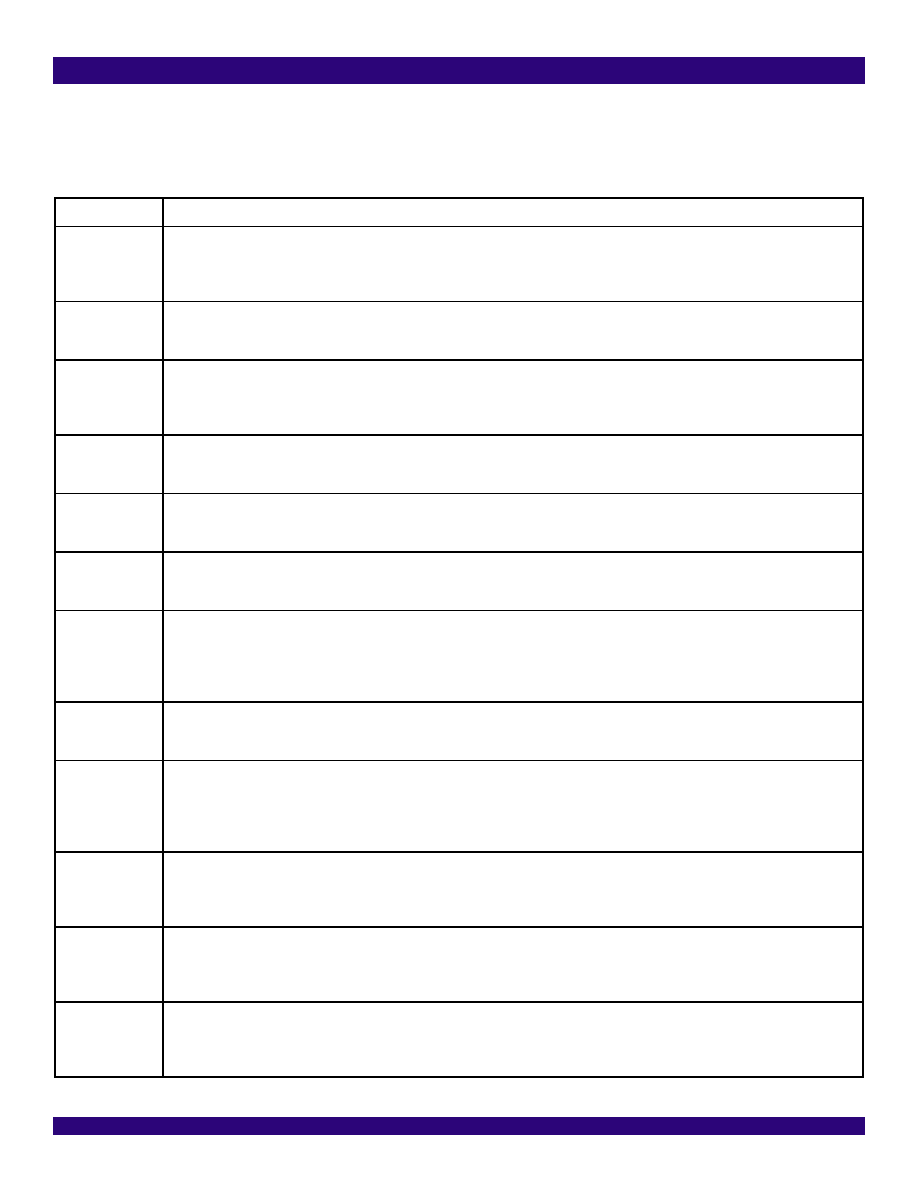

Table-22 TAP Controller State Description

State

Description

Test Logic Reset

In this state, the test logic is disabled. The device is set to normal operation. During initialization, the device initializes the instruction register

with the IDCODE instruction.

Regardless of the original state of the controller, the controller enters the Test-Logic-Reset state when the TMS input is held high for at least 5

rising edges of TCK. The controller remains in this state while TMS is high. The device processor automatically enters this state at power-up.

Run-Test/Idle

This is a controller state between scan operations. Once in this state, the controller remains in the state as long as TMS is held low. The

instruction register and all test data registers retain their previous state. When TMS is high and a rising edge is applied to TCK, the controller

moves to the Select-DR state.

Select-DR-Scan

This is a temporary controller state and the instruction does not change in this state. The test data register selected by the current instruction

retains its previous state. If TMS is held low and a rising edge is applied to TCK when in this state, the controller moves into the Capture-DR

state and a scan sequence for the selected test data register is initiated. If TMS is held high and a rising edge applied to TCK, the controller

moves to the Select-IR-Scan state.

Capture-DR

In this state, the Boundary Scan Register captures input pin data if the current instruction is EXTEST or SAMPLE/PRELOAD. The instruction

does not change in this state. The other test data registers, which do not have parallel input, are not changed. When the TAP controller is in

this state and a rising edge is applied to TCK, the controller enters the Exit1-DR state if TMS is high or the Shift-DR state if TMS is low.

Shift-DR

In this controller state, the test data register connected between TDI and TDO as a result of the current instruction shifts data on stage toward

its serial output on each rising edge of TCK. The instruction does not change in this state. When the TAP controller is in this state and a rising

edge is applied to TCK, the controller enters the Exit1-DR state if TMS is high or remains in the Shift-DR state if TMS is low.

Exit1-DR

This is a temporary state. While in this state, if TMS is held high, a rising edge applied to TCK causes the controller to enter the Update-DR

state, which terminates the scanning process. If TMS is held low and a rising edge is applied to TCK, the controller enters the Pause-DR

state. The test data register selected by the current instruction retains its previous value and the instruction does not change during this state.

Pause-DR

The pause state allows the test controller to temporarily halt the shifting of data through the test data register in the serial path between TDI

and TDO. For example, this state could be used to allow the tester to reload its pin memory from disk during application of a long test

sequence. The test data register selected by the current instruction retains its previous value and the instruction does not change during this

state. The controller remains in this state as long as TMS is low. When TMS goes high and a rising edge is applied to TCK, the controller

moves to the Exit2-DR state.

Exit2-DR

This is a temporary state. While in this state, if TMS is held high, a rising edge applied to TCK causes the controller to enter the Update-DR

state, which terminates the scanning process. If TMS is held low and a rising edge is applied to TCK, the controller enters the Shift-DR state.

The test data register selected by the current instruction retains its previous value and the instruction does not change during this state.

Update-DR

The Boundary Scan Register is provided with a latched parallel output to prevent changes while data is shifted in response to the EXTEST

and SAMPLE/PRELOAD instructions. When the TAP controller is in this state and the Boundary Scan Register is selected, data is latched into

the parallel output of this register from the shift-register path on the falling edge of TCK. The data held at the latched parallel output changes

only in this state. All shift-register stages in the test data register selected by the current instruction retain their previous value and the instruc-

tion does not change during this state.

Select-IR-Scan

This is a temporary controller state. The test data register selected by the current instruction retains its previous state. If TMS is held low and

a rising edge is applied to TCK when in this state, the controller moves into the Capture-IR state, and a scan sequence for the instruction reg-

ister is initiated. If TMS is held high and a rising edge is applied to TCK, the controller moves to the Test-Logic-Reset state. The instruction

does not change during this state.

Capture-IR

In this controller state, the shift register contained in the instruction register loads a fixed value of ‘100’ on the rising edge of TCK. This sup-

ports fault-isolation of the board-level serial test data path. Data registers selected by the current instruction retain their value and the instruc-

tion does not change during this state. When the controller is in this state and a rising edge is applied to TCK, the controller enters the Exit1-

IR state if TMS is held high, or the Shift-IR state if TMS is held low.

Shift-IR

In this state, the shift register contained in the instruction register is connected between TDI and TDO and shifts data one stage towards its

serial output on each rising edge of TCK. The test data register selected by the current instruction retains its previous value and the instruction

does not change during this state. When the controller is in this state and a rising edge is applied to TCK, the controller enters the Exit1-IR

state if TMS is held high, or remains in the Shift-IR state if TMS is held low.

相关PDF资料 |

PDF描述 |

|---|---|

| IDT72T3645L6-7BB | IC FIFO 1024X36 6-7NS 208-BGA |

| MAX11208AEUB+T | IC ADC 19BIT SRL 120SPS 10UMAX |

| MS27508E10B35SB | CONN RCPT 13POS BOX MNT W/SCKT |

| MAX11203EEE+T | IC ADC 16BIT SPI/SRL 16QSOP |

| IDT723633L12PF | IC FIFO SYNC 512X36 128-TQFP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| IDT82V2048BBG | 功能描述:IC LIU T1/E1 8CH SHORT 160-BGA RoHS:是 类别:集成电路 (IC) >> 接口 - 驱动器,接收器,收发器 系列:- 标准包装:250 系列:- 类型:收发器 驱动器/接收器数:2/2 规程:RS232 电源电压:3 V ~ 5.5 V 安装类型:表面贴装 封装/外壳:16-TSSOP(0.173",4.40mm 宽) 供应商设备封装:16-TSSOP 包装:带卷 (TR) |

| IDT82V2048DA | 功能描述:IC LIU T1/E1 8CH SHORT 144-TQFP RoHS:否 类别:集成电路 (IC) >> 接口 - 驱动器,接收器,收发器 系列:- 标准包装:250 系列:- 类型:收发器 驱动器/接收器数:2/2 规程:RS232 电源电压:3 V ~ 5.5 V 安装类型:表面贴装 封装/外壳:16-TSSOP(0.173",4.40mm 宽) 供应商设备封装:16-TSSOP 包装:带卷 (TR) |

| IDT82V2048DAG | 功能描述:IC LIU T1/E1 8CH SHORT 144-TQFP RoHS:是 类别:集成电路 (IC) >> 接口 - 驱动器,接收器,收发器 系列:- 标准包装:250 系列:- 类型:收发器 驱动器/接收器数:2/2 规程:RS232 电源电压:3 V ~ 5.5 V 安装类型:表面贴装 封装/外壳:16-TSSOP(0.173",4.40mm 宽) 供应商设备封装:16-TSSOP 包装:带卷 (TR) |

| IDT82V2048E | 制造商:IDT 制造商全称:Integrated Device Technology 功能描述:OCTAL CHANNEL T1/E1/J1 SHORT HAUL LINE INTERFACE UNIT |

| IDT82V2048EBB | 功能描述:IC LIU T1/E1 8CH SHORT 208-BGA RoHS:否 类别:集成电路 (IC) >> 接口 - 驱动器,接收器,收发器 系列:- 标准包装:250 系列:- 类型:收发器 驱动器/接收器数:2/2 规程:RS232 电源电压:3 V ~ 5.5 V 安装类型:表面贴装 封装/外壳:16-TSSOP(0.173",4.40mm 宽) 供应商设备封装:16-TSSOP 包装:带卷 (TR) |

发布紧急采购,3分钟左右您将得到回复。