- 您现在的位置:买卖IC网 > PDF目录2000 > IDTNW6006AS (IDT, Integrated Device Technology Inc)IC CALLER ID DECODER 20-SOIC PDF资料下载

参数资料

| 型号: | IDTNW6006AS |

| 厂商: | IDT, Integrated Device Technology Inc |

| 文件页数: | 16/22页 |

| 文件大小: | 0K |

| 描述: | IC CALLER ID DECODER 20-SOIC |

| 标准包装: | 37 |

| 类型: | 来电身份解码器 |

| 应用: | 传真,调制解调器,寻呼机 |

| 电压 - 电源,模拟: | 2.5 V ~ 3.8 V |

| 电压 - 电源,数字: | 2.5 V ~ 3.8 V |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 20-SOIC(0.295",7.50mm 宽) |

| 供应商设备封装: | 20-SOIC |

| 包装: | 管件 |

| 其它名称: | NW6006AS |

3

INDUSTRIAL TEMPERATURE RANGE

NW6006 ENHANCED TYPE II CALLER ID DECODER

WITH STUTTER DIAL TONE DETECTOR

Abbreviation Index

CAS

----------------------------------------------------------- CPE Alerting Signal

CDS

---------------------------------------------------------- Caller Display Service

CID

---------------------------------------------------------- Calling Identity Delivery

CIDCW

---------------------------------------------------------- Calling Identity Delivery on Call Waiting

CLIP

---------------------------------------------------------- Calling Line Identity Presentation

CNAM

--------------------------------------------------------- Calling Name Delivery

CND

--------------------------------------------------------- Calling Number Delivery

CNIC

---------------------------------------------------------- Calling Number Identification Circuit

CO

---------------------------------------------------------- Central Office

DT-AS

---------------------------------------------------------- Dual Tone Alert Signal

MEI

---------------------------------------------------------- Multiple Extension Interworking

SDT

---------------------------------------------------------- Stutter Dial Tone

TE

---------------------------------------------------------- Terminal Equipment

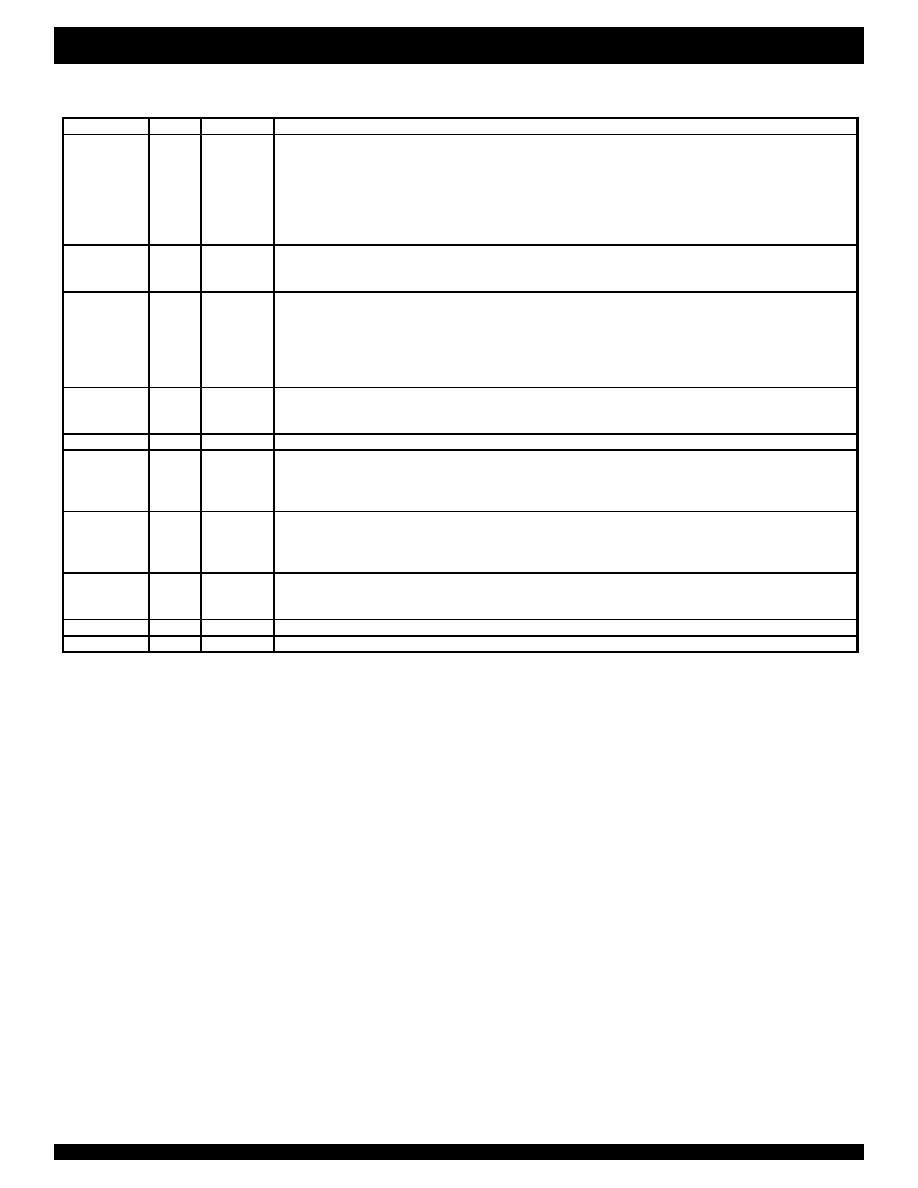

PIN INFORMATION (CONTINUED)

Name

Type

Pin No.

Description

DR/STD

O/NC

11

Data Ready or DT-AS Detection Delayed Steering Output.

This pin is active low. When FSK demodulation is enabled, this pin is the Data Ready output. In FSK interface mode 0,

this pin is unused and reads ‘1’. While in mode 1, this pin is normally high and goes low for half a bit time at the end of

a word. If DCLK starts during DR low, the first rising edge of the DCLK input will return DR to high. In this way, reading

of the first DATA bit can clear the interrupt requested by a low going DR.

When DT-AS detection is enabled, this pin is the Delayed Steering Output. An active low signal on this output indicates

the detection of a ‘guard time qualified’ DT-AS.

EST

O

12

DT-AS Early Steering Output.

This pin is an active high output to indicate the detection of a raw DT-AS signal. It is used with the ST/GT pin and

external components to time qualify the detection.

ST/GT

I/O

13

DT-AS Detection Steering Input/Guard Time Output.

It’s a CMOS output and an input of voltage comparator. It is used in conjunction with the EST pin and external

components to time qualify a raw DT-AS signal detection.

If the voltage at this pin is greater than the voltage threshold, DR/STD pin is asserted low to indicate that a DT-AS has

been detected. A voltage less than the threshold enable the device to accept a new DT-AS and return the DR/STD pin

to high.

CD/STRDT

O

14

FSK Carrier Detector or Stutter Dial Tone Detector Output.

This is an active low CMOS output signal to indicate the presence of in-band FSK signal or valid Stutter Dial Tone

signal.

VCC

-

15

3/5 V Power Supply.

CB1

I

16

Control Bit 1 (Function Select 1).

This pin is used with CB2 to select FSK demodulation, Tip/Ring DT-AS/Dial Tone detection, Hybrid DT-AS/Dial Tone

detection with or without Stutter Dial Tone Detection. See Table 1. When CB0 is high, CB1 and CB2 pins are both low,

the device is set into the power down state.

CB2

I

17

Control Bit 2 (Function Select 0).

This pin is used with CB2 to select FSK demodulation, Tip/Ring DT-AS/Dial Tone detection, Hybrid DT-AS/Dial Tone

detection with or without Stutter Dial Tone Detection. See Table 1. When CB0 is high, CB1 and CB2 pins are both low,

the device is set into the power down state.

GS2

O

18

Gain Select Output of the gain adjustable Hybrid OP amp.

The hybrid receive signal can be amplified or attenuated at GS2 by adjusting the feedback resistor between GS2 and

IN2-. When the CPE is off-hook, DT-AS detection of the GS2 signal should be enabled via the CB1 and CB2 pins.

IN2-

I

19

Inverting Input of the gain adjustable Hybrid OP amp.

IN2+

I

20

Non-inverting Input of the gain adjustable Hybrid OP amp.

相关PDF资料 |

PDF描述 |

|---|---|

| IDTSSTE32882HLBBKG | IC REGISTERING CLK DRIVER 176BGA |

| IDTSSTE32882KA1AKG | IC REGISTERING CLK DRIVER 176BGA |

| ISD1750SYR | IC VOICE REC/PLAY 50SEC 28-SOIC |

| ISD5008EYI | IC VOICE REC/PLAY 4-8MIN 28-TSOP |

| ISL12008IB8Z | IC RTC I2C LO-POWER 8-SOIC |

相关代理商/技术参数 |

参数描述 |

|---|---|

| IDTP62000NLG | 制造商:Integrated Device Technology Inc 功能描述:IC PWM CTRLR 2/3/4-PHASE 64QFN |

| IDTP62000NLG8 | 制造商:Integrated Device Technology Inc 功能描述:IC PWM CTRLR 2/3/4-PHASE 64QFN |

| IDTP63131-00NDGI | 制造商:Integrated Device Technology Inc 功能描述:IC BUCK CTRLR MULTI-PH 40QFN |

| IDTP63131-00NDGI8 | 制造商:Integrated Device Technology Inc 功能描述:IC BUCK CTRLR MULTI-PH 40QFN |

| IDTP63133-00NDGI | 制造商:Integrated Device Technology Inc 功能描述:IC BUCK CTRLR MULTI-PH 40QFN |

发布紧急采购,3分钟左右您将得到回复。