- 您现在的位置:买卖IC网 > PDF目录239729 > IM42-67025V-55 (ATMEL CORP) 8K X 16 DUAL-PORT SRAM, 55 ns, CQCC84 PDF资料下载

参数资料

| 型号: | IM42-67025V-55 |

| 厂商: | ATMEL CORP |

| 元件分类: | SRAM |

| 英文描述: | 8K X 16 DUAL-PORT SRAM, 55 ns, CQCC84 |

| 封装: | LCC-84 |

| 文件页数: | 9/23页 |

| 文件大小: | 257K |

| 代理商: | IM42-67025V-55 |

M 67025

MATRA MHS

Rev. D (29/09/95)

17

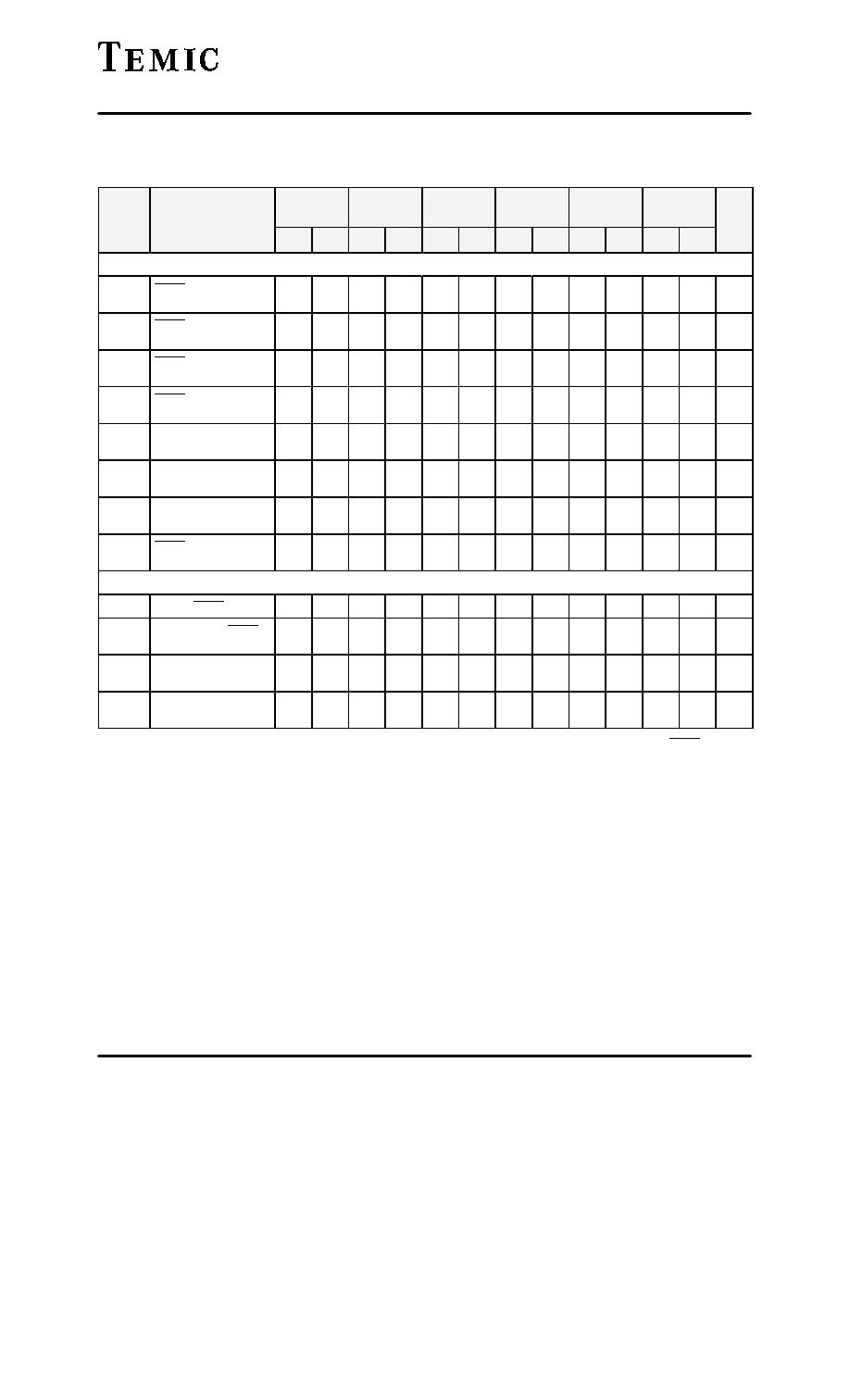

AC Electrical Characteristics

over the Full Operating Temperature and Supply Voltage Range

WRITE

CYCLE

PARAMETER

M

67025–20

M

67025–25

M

67025–30

M

67025–35

M

67025–45

M

67025–55

UNIT

CYCLE

PARAMETER

Min. Max. Min. Max. Min. Max. Min. Max. Min. Max. Min. Max.

UNIT

BUSY TIMING (For Master 67025 only)

tBAA

BUSY Access time

to address

–

20

–

25

–

30

–

35

–

35

–

45

ns

tBDA

BUSY Disable time

to address

–

15

–

20

–

25

–

30

–

30

–

40

ns

tBAC

BUSY Access time

to Chip Select

–

15

–

20

–

25

–

30

–

30

–

40

ns

tBDC

BUSY Disable time

to Chip Select

–

13

–

17

–

20

–

25

–

25

–

35

ns

tWDD

Write Pulse to data Delay

(1)

–

45

–

50

–

55

–

60

–

70

–

80

ns

tDDD

Write data valid to read

data delay (1)

–

35

–

35

–

40

–

45

–

55

–

65

ns

tAPS

Arbitration priority

set–up time (2)

5

–

5

–

5

–

5

–

5

–

5

–

ns

tBDD

BUSY disable to valid

data

–

Note 3

–

Note 3

–

Note 3

–

Note 3

–

Note 3

–

Note 3

ns

BUSY TIMING (For Slave 67025 only)

tWB

Write to BUSY input (4)

0

–

0

–

0

–

0

–

0

–

0

–

ns

tWH

Write hold after BUSY

(5)

15

–

17

–

20

–

25

–

25

–

25

–

ns

tWDD

Write pulse to data delay

(6)

–

45

–

50

–

55

–

60

–

70

–

80

ns

tDDD

Write data valid to read

data delay (6)

–

35

–

35

–

40

–

45

–

55

–

65

ns

Notes :

1. Port-to-port delay through RAM cells from writing port to reading port, refer to “Timing Waveform of Read with BUSY (For

Master 67025 only).

2. To ensure that the earlier of the two ports wins.

3. tBDD is a calculated parameter and is the greater of 0, tWDD – tWP (actual) ot tDDD – tDW (actual).

4. To ensure that the write cycle is inhibited during contention.

5. To ensure that a write cycle is completed after contention.

6. Port-to-port delay through RAM cells from writing port to reading port, refer to “Timing Waveforms of Read with Port-to-port

delay (For Slave, 67025 only)”.

相关PDF资料 |

PDF描述 |

|---|---|

| IDT7052S20G | 2K X 8 FOUR-PORT SRAM, 20 ns, CPGA108 |

| IS61NVP12836B-200B3 | 128K X 36 ZBT SRAM, 3.1 ns, PBGA165 |

| IDT7202SA120DB | 1K X 9 OTHER FIFO, 120 ns, CDIP28 |

| IDT7202SA25L8 | 1K X 9 OTHER FIFO, 25 ns, CQCC32 |

| IDT7202SA35SO8 | 1K X 9 OTHER FIFO, 35 ns, PDSO28 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| IM42CGR | 功能描述:高频/射频继电器 IM RELAY 100mW RoHS:否 制造商:Omron Electronics 触点形式:2 Form C (DPDT-BM) 触点电流额定值: 线圈电压:5 VDC 线圈类型:Non-Latching 频率: 功耗:100 mW 端接类型:Solder Terminal 绝缘:20 dB to 30 dB at 1 GHz 介入损耗:0.2 dB at 1 GHz |

| IM42DGR | 功能描述:高频/射频继电器 IM RELAY 100mW RoHS:否 制造商:Omron Electronics 触点形式:2 Form C (DPDT-BM) 触点电流额定值: 线圈电压:5 VDC 线圈类型:Non-Latching 频率: 功耗:100 mW 端接类型:Solder Terminal 绝缘:20 dB to 30 dB at 1 GHz 介入损耗:0.2 dB at 1 GHz |

| IM42GR | 功能描述:高频/射频继电器 DPDT 4.5VDC 1-Coil 1000 RoHS:否 制造商:Omron Electronics 触点形式:2 Form C (DPDT-BM) 触点电流额定值: 线圈电压:5 VDC 线圈类型:Non-Latching 频率: 功耗:100 mW 端接类型:Solder Terminal 绝缘:20 dB to 30 dB at 1 GHz 介入损耗:0.2 dB at 1 GHz |

| IM42JR | 制造商:MA-COM 制造商全称:M/A-COM Technology Solutions, Inc. 功能描述:IM Series Signal Relays |

发布紧急采购,3分钟左右您将得到回复。