参数资料

| 型号: | IP80C88 |

| 厂商: | Intersil |

| 文件页数: | 37/38页 |

| 文件大小: | 0K |

| 描述: | IC CPU 8/16BIT 5V 5MHZ 40-DIP |

| 标准包装: | 99 |

| 处理器类型: | 80C88 8/16-位 |

| 速度: | 5MHz |

| 电压: | 4.5 ~ 5.5V |

| 安装类型: | 通孔 |

| 封装/外壳: | 40-DIP(0.600",15.24mm) |

| 供应商设备封装: | 40-DIP |

| 包装: | 管件 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页当前第37页第38页

8

FN2949.4

February 22, 2008

.

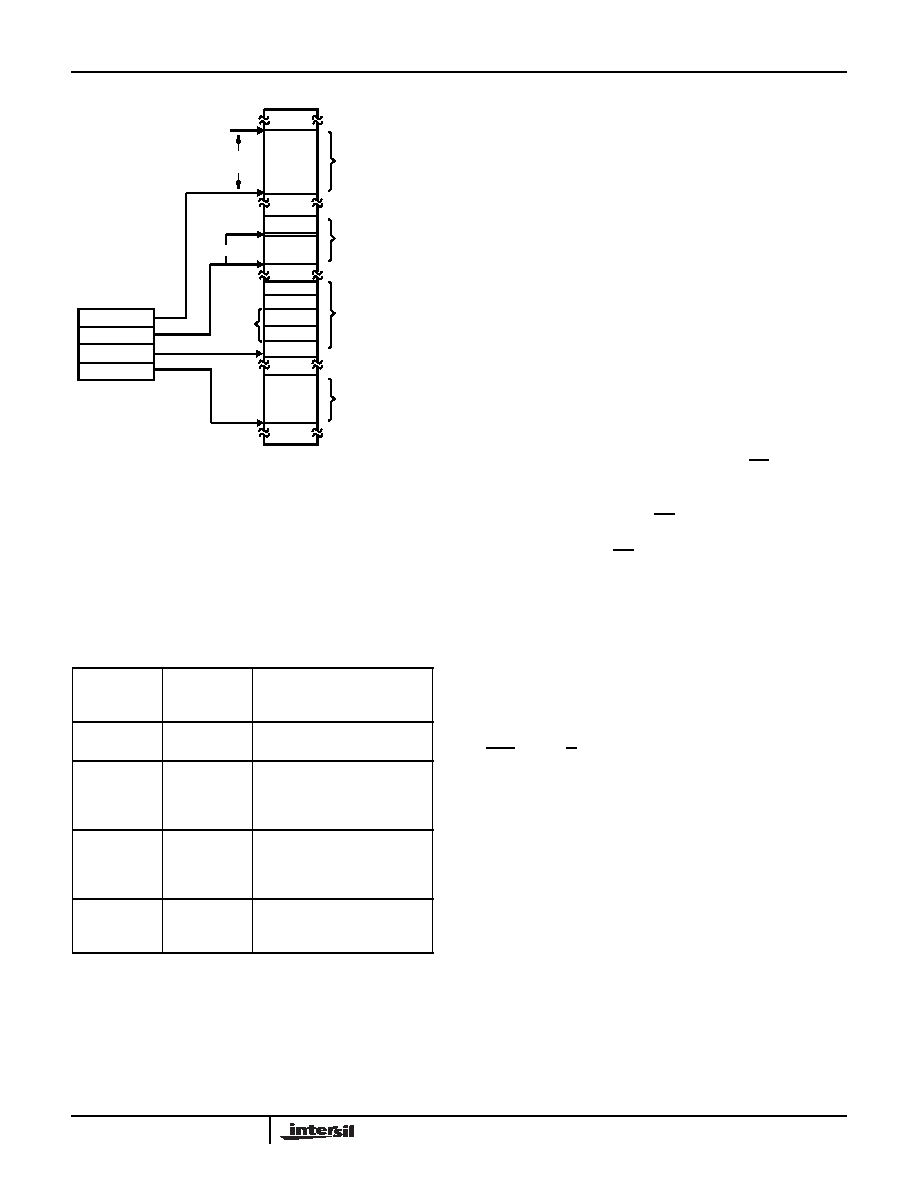

All memory references are made relative to base addresses

contained in high speed segment registers. The segment

types were chosen based on the addressing needs of

programs. The segment register to be selected is

automatically chosen according to specific rules as shown in

Table1. All information in one segment type share the same

logical attributes (e.g., code or data). By structuring memory

into relocatable areas of similar characteristics and by

automatically selecting segment registers, programs are

shorter, faster, and more structured.

Word (16-bit) operands can be located on even or odd

address boundaries. For address and data operands, the

least significant byte of the word is stored in the lower valued

address location and the most significant byte in the next

higher address location.

The BIU will automatically execute two fetch or write cycles

for 16-bit operands.

Certain locations in memory are reserved for specific CPU

operations. (See Figure 2). Locations from addresses

FFFF0H through FFFFFH are reserved for operations

including a jump to initial system initialization routine.

Following RESET, the CPU will always begin execution at

location FFFF0H where the jump must be located. Locations

00000H through 003FFH are reserved for interrupt

operations. Each of the 256 possible interrupt service

routines is accessed through its own pair of 16-bit pointers -

segment address pointer and offset address pointer. The

first pointer, used as the offset address, is loaded into the IP,

and the second pointer, which designates the base address,

is loaded into the CS. At this point program control is

transferred to the interrupt routine. The pointer elements are

assumed to have been stored at their respective places in

reserved memory prior to the occurrence of interrupts.

Minimum and Maximum Modes

The requirements for supporting minimum and maximum

80C88 systems are sufficiently different that they cannot be

done efficiently with 40 uniquely defined pins. Consequently,

the 80C88 is equipped with a strap pin (MN/MX) which

defines the system configuration. The definition of a certain

subset of the pins changes, dependent on the condition of

the strap pin. When the MN/MX pin is strapped to GND, the

80C88 defines pins 24 through 31 and 34 in maximum

mode. When the MN/MX pins is strapped to VCC, the 80C88

generates bus control signals itself on pins 24 through 31

and 34.

The minimum mode 80C88 can be used with either a

muliplexed or demultiplexed bus. This architecture provides

the 80C88 processing power in a highly integrated form.

The demultiplexed mode requires one latch (for 64k address

ability) or two latches (for a full megabyte of addressing). An

82C86 or 82C87 transceiver can also be used if data bus

buffering is required. (See Figure 3). The 80C88 provides

DEN and DT/R to control the transceiver, and ALE to latch

the addresses. This configuration of the minimum mode

provides the standard demultiplexed bus structure with

heavy bus buffering and relaxed bus timing requirements.

The maximum mode employs the 82C88 bus controller (See

Figure 4). The 82C88 decode status lines S0, S1 and S2,

and provides the system with all bus control signals. Moving

the bus control to the 82C88 provides better source and sink

current capability to the control lines, and frees the 80C88

pins for extended large system features. Hardware lock,

queue status, and two request/grant interfaces are provided

by the 80C88 in maximum mode. These features allow

coprocessors in local bus and remote bus configurations.

TABLE 1.

MEMORY

REFERENCE

NEED

SEGMENT

REGISTER

USED

SEGMENT

SELECTION RULE

Instructions

CODE (CS)

Automatic with all instruction

prefetch.

Stack

STACK (SS)

All stack pushes and pops.

Memory references relative to

BP base register except data

references.

Local Data

DATA (DS)

Data references when: relative

to stack, destination of string

operation, or explicitly

overridden.

External Data

(Global)

EXTRA (ES)

Destination of string

operations: Explicitly selected

using a segment override.

SEGMENT

REGISTER FILE

CS

SS

DS

ES

64K-BIT

+ OFFSET

FFFFFH

CODE SEGMENT

XXXXOH

STACK SEGMENT

DATA SEGMENT

EXTRA SEGMENT

00000H

FIGURE 1. MEMORY ORGANIZATION

MSB

BYTE

LSB

70

WORD

80C88

相关PDF资料 |

PDF描述 |

|---|---|

| SPC5200CBV400B | IC MPU 32BIT 500MHZ 272PBGA |

| ABB85DHBR | CONN EDGECARD 170PS R/A .050 SLD |

| XF2M-2215-1A | CONN FPC 22POS 0.5MM PITCH SMD |

| MPC859TCVR100A | IC MPU POWERQUICC 100MHZ 357PBGA |

| FMC25DRES | CONN EDGECARD 50POS .100 EYELET |

相关代理商/技术参数 |

参数描述 |

|---|---|

| IP80C88/+ | 制造商:未知厂家 制造商全称:未知厂家 功能描述:16-Bit Microprocessor |

| IP80C88-2 | 功能描述:微处理器 - MPU CPU 8/16BIT 5V 8MHZ IND RoHS:否 制造商:Atmel 处理器系列:SAMA5D31 核心:ARM Cortex A5 数据总线宽度:32 bit 最大时钟频率:536 MHz 程序存储器大小:32 KB 数据 RAM 大小:128 KB 接口类型:CAN, Ethernet, LIN, SPI,TWI, UART, USB 工作电源电压:1.8 V to 3.3 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:FBGA-324 |

| IP80C88-2/+ | 制造商:未知厂家 制造商全称:未知厂家 功能描述:16-Bit Microprocessor |

| IP80C88-2S2064 | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| IP80C88S2064 | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

发布紧急采购,3分钟左右您将得到回复。