- 您现在的位置:买卖IC网 > PDF目录383110 > IP82C84A (INTERSIL CORP) CMOS Clock Generator Driver PDF资料下载

参数资料

| 型号: | IP82C84A |

| 厂商: | INTERSIL CORP |

| 元件分类: | XO, clock |

| 英文描述: | CMOS Clock Generator Driver |

| 中文描述: | 8 MHz, PROC SPECIFIC CLOCK GENERATOR, PDIP18 |

| 封装: | PLASTIC, DIP-18 |

| 文件页数: | 3/10页 |

| 文件大小: | 89K |

| 代理商: | IP82C84A |

4-289

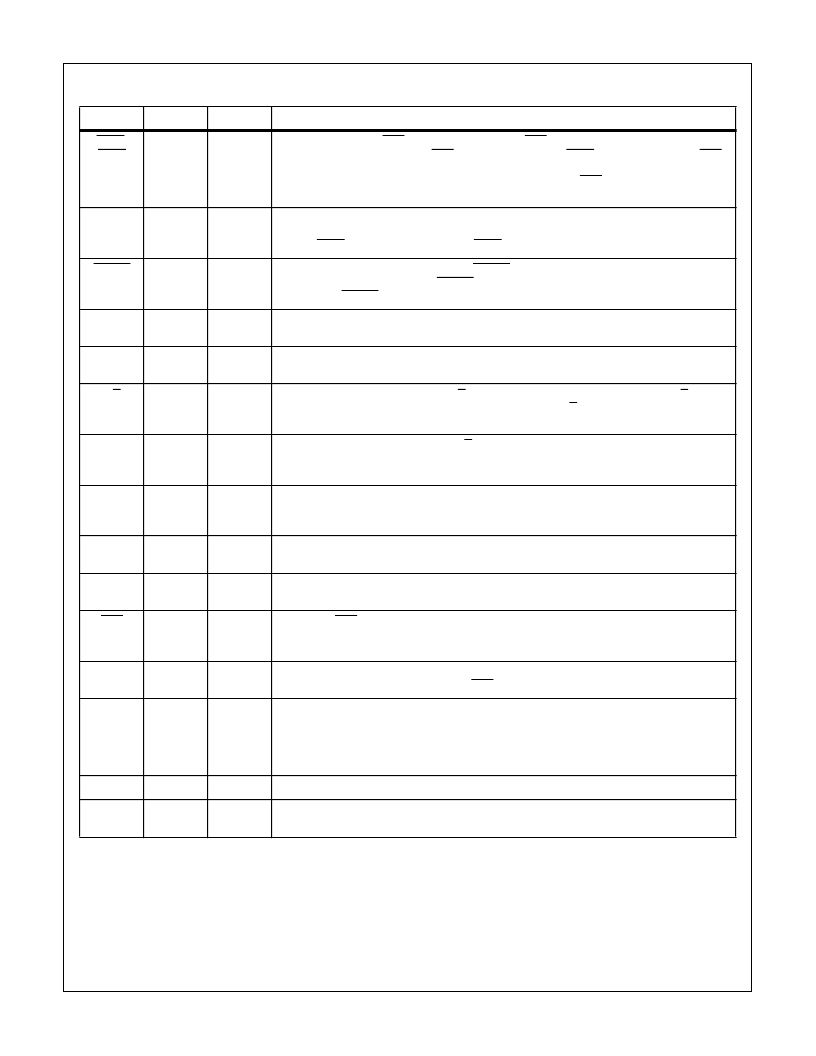

Pin Description

SYMBOL

NUMBER

TYPE

DESCRIPTION

AEN1,

AEN2

3, 7

I

ADDRESS ENABLE: AEN is an active LOW signal. AEN serves to qualify its respective Bus

Ready Signal (RDY1 or RDY2). AEN1 validates RDY1 while AEN2 validates RDY2. Two AEN

signal inputs are useful in system configurations which permit the processor to access two Multi-

Master System Busses. In non-Multi-Master configurations, the AEN signal inputs are tied true

(LOW).

RDY1,

RDY2

4, 6

I

BUS READY (Transfer Complete). RDY is an active HIGH signal which is an indication from a

device located on the system data bus that data has been received, or is available RDY1 is qual-

ified by AEN1 while RDY2 is qualified by AEN2.

ASYNC

15

I

READY SYNCHRONIZATION SELECT: ASYNC is an input which defines the synchronization

mode of the READY logic. When ASYNC is low, two stages of READY synchronization are pro-

vided. When ASYNC is left open or HIGH, a single stage of READY synchronization is provided.

READY

5

O

READY: READY is an active HIGH signal which is the synchronized RDY signal input. READY

is cleared after the guaranteed hold time to the processor has been met.

X1, X2

17, 16

I O

CRYSTAL IN: X1 and X2 are the pins to which a crystal is attached. The crystal frequency is 3

times the desired processor clock frequency, (Note 1).

F/C

13

I

FREQUENCY/CRYSTAL SELECT: F/C is a strapping option. When strapped LOW. F/C permits

the processor’s clock to be generated by the crystal. When F/C is strapped HIGH, CLK is gen-

erated for the EFI input, (Note 1).

EFI

14

I

EXTERNAL FREQUENCY IN: When F/C is strapped HIGH, CLK is generated from the input fre-

quency appearing on this pin. The input signal is a square wave 3 times the frequency of the de-

sired CLK output.

CLK

8

O

PROCESSOR CLOCK: CLK is the clock output used by the processor and all devices which di-

rectly connect to the processor’s local bus. CLK has an output frequency which is 1/3 of the crys-

tal or EFI input frequency and a 1/3 duty cycle.

PCLK

2

O

PERIPHERAL CLOCK: PCLK is a peripheral clock signal whose output frequency is 1/2 that of

CLK and has a 50% duty cycle.

OSC

12

O

OSCILLATOR OUTPUT: OSC is the output of the internal oscillator circuitry. Its frequency is

equal to that of the crystal.

RES

11

I

RESET IN: RES is an active LOW signal which is used to generate RESET. The 82C84A pro-

vides a Schmitt trigger input so that an RC connection can be used to establish the power-up

reset of proper duration.

RESET

10

O

RESET: RESET is an active HIGH signal which is used to reset the 80C86 family processors. Its

timing characteristics are determined by RES.

CSYNC

1

I

CLOCK SYNCHRONIZATION: CSYNC is an active HIGH signal which allows multiple 82C84As

to be synchronized to provide clocks that are in phase. When CSYNC is HIGH the internal

counters are reset. When CSYNC goes LOW the internal counters are allowed to resume count-

ing. CSYNC needs to be externally synchronized to EFI. When using the internal oscillator

CSYNC should be hardwired to ground.

GND

9

Ground

V

CC

18

V

CC

: The +5V power supply pin. A 0.1

μ

F capacitor between V

CC

and GND is recommended for

decoupling.

NOTE:

1. If the crystal inputs are not used X1 must be tied to V

CC

or GND and X2 should be left open.

82C84A

相关PDF资料 |

PDF描述 |

|---|---|

| IP82C86H | CMOS Octal Bus Transceiver |

| IP82C86H-5 | CMOS Octal Bus Transceiver |

| IP82C87H | CMOS Octal Inverting Bus Transceiver |

| IP82C87H-5 | CMOS Octal Inverting Bus Transceiver |

| IP82C88 | CMOS Bus Controller |

相关代理商/技术参数 |

参数描述 |

|---|---|

| IP82C86H | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:CMOS Octal Bus Transceiver |

| IP82C86H/+ | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Single 8-bit Bus Transceiver |

| IP82C86H-5 | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| IP82C87H | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:CMOS Octal Inverting Bus Transceiver |

| IP82C87H/+ | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Single 8-Bit Inverting Bus Transceiver |

发布紧急采购,3分钟左右您将得到回复。