- 您现在的位置:买卖IC网 > PDF目录383110 > IP82C89 (HARRIS SEMICONDUCTOR) CMOS Bus Arbiter PDF资料下载

参数资料

| 型号: | IP82C89 |

| 厂商: | HARRIS SEMICONDUCTOR |

| 元件分类: | 外设及接口 |

| 英文描述: | CMOS Bus Arbiter |

| 中文描述: | 8 MHz, BUS ARBITER AND CONT SIG GEN, PDIP20 |

| 文件页数: | 13/15页 |

| 文件大小: | 123K |

| 代理商: | IP82C89 |

4-355

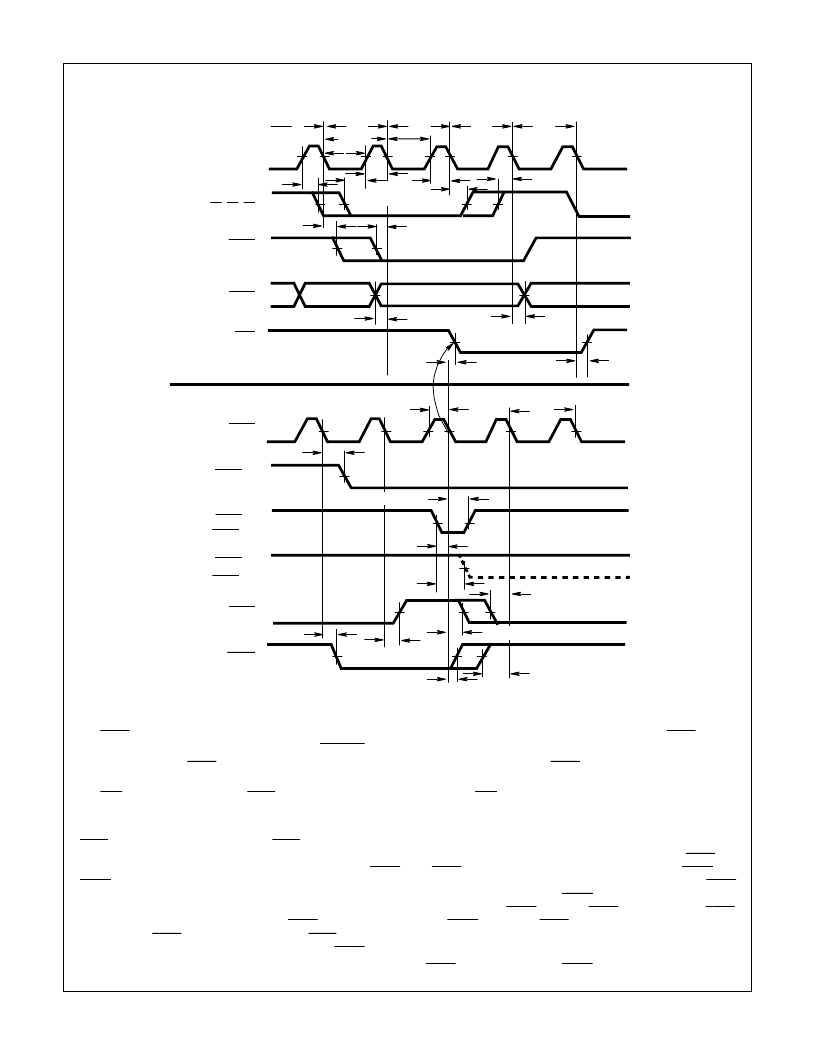

Timing Waveform

NOTES:

1. LOCK active can occur during any state, as long as the relationships shown above with respect to the CLK are maintained. LOCK inactive

has no critical time and can be asynchronous. CRQLCK has no critical timing and is considered an asynchronous input signal.

2. Glitching of SYSB/RESB is permitted during this time. After

θ

2 of T1, and before

θ

1 of T4, SYSB/RESB should be stable to maintain sys-

tem efficiency.

3. AEN leading edge is related to BCLK, trailing edge to CLK. The trailing edge of AEN occurs after bus priority is lost.

ADDITIONAL NOTES:

The signals related to CLK are typical processor signals, and do not relate to the depicted sequence of events of the signals referenced to

BCLK. The signals shown related to the BCLK represent a hypothetical sequence of events for illustration. Assume 3 bus arbiters of priori-

ties 1, 2 and 3 configured in serial priority resolving scheme (as shown in Figure 3). Assume arbiter 1 has the bus and is holding BUSY low.

Arbiter #2 detects its processor wants the bus and pulls low BREQ #2. If BPRN #2 is high (as shown), arbiter #2 will pull low CBRQ line.

CBRQ signals to the higher priority arbiter #1 that a lower priority arbiter wants the bus. [A higher priority arbiter would be granted BPRN

when it makes the bus request rather than having to wait for another arbiter to release the bus through CBRQ]. *Arbiter #1 will relinquish the

multi-master system bus when it enters a state not requiring it (see Table 1), by lowering its BPRO #1 (tied to BPRN #2) and releasing BUSY.

Arbiter #2 now sees that is has priority from BPRN #2 being low and releases CBRQ. As soon as BUSY signifies the bus is available (high),

arbiter #2 pulls BUSY low on next falling edge of BCLK. Note that if arbiter #2 didn’t want the bus at the time it received priority, it would pass

priority to the next lower priority arbiter by lowering its BPRO #2 [TPNPO].

Note that even a higher priority arbiter which is acquiring the bus through BPRN will momentarily drop CBRQ until it has acquired the bus.

STATE

CLK

S2, S1, S0

LOCK

(SEE NOTE 1)

SYSB/RESB

AEN

(SEE NOTE 3)

PROCESSOR CLK RELATED

BUS CLK RELATED

BCLK

BREQ #2

BPRN #2

(BPRO #1)

BPRO #2

(BPRN #3)

BUSY

CBRQ

(20)

TPnPO

(14)

TPNBL

(22)

TBLBYH

(11)

TBHCL

(24)

TBLAEL

(13)

TCLL2

(12)

TCLLL1

(6)

THVCH

(4)

TSVCH

(7)

THVCL

(2)

TCLCH

(16)

TCLSR2

(SEE

NOTE 2)

(23)

TCLAEH

(10)

TBLBL

TBYSBL (8)

TCBSBL (9)

(26) TBLCBH

TCLSR1 (15)

(SEE NOTE 2)

TSHCL (5)

(25) TBLCBL

(18) TBLBRL

T4

T1

T2

T3

T4

TCLCL

(1)

(3)

TCHCL

TBLPOH (19)

TBLBYL (21)

82C89

相关PDF资料 |

PDF描述 |

|---|---|

| IPA60R125CP | CoolMOS Power Transistor |

| IPA60R165CP | CoolMOS Power Transistor |

| IPA60R199CP | CoolMOS Power Transistor |

| IPA60R299CP | CoolMOS Power Transistor |

| IPA60R385CP | CoolMOS Power Transistor |

相关代理商/技术参数 |

参数描述 |

|---|---|

| IP8327A-4 | 制造商:AMD 制造商全称:Advanced Micro Devices 功能描述:Multimode DMA Controller |

| IP8327A-4B | 制造商:AMD 制造商全称:Advanced Micro Devices 功能描述:Multimode DMA Controller |

| IP8327A-5 | 制造商:AMD 制造商全称:Advanced Micro Devices 功能描述:Multimode DMA Controller |

| IP8327A-5B | 制造商:AMD 制造商全称:Advanced Micro Devices 功能描述:Multimode DMA Controller |

| IP83C151C-12 | 制造商:TEMIC 制造商全称:TEMIC Semiconductors 功能描述:CMOS 0 to 36 MHz Single Chip 8-bit Microcontroller |

发布紧急采购,3分钟左右您将得到回复。