- 您现在的位置:买卖IC网 > PDF目录11818 > IS82C50A-5 (Intersil)IC PERIPH UART/BRG 10MHZ 44-PLCC PDF资料下载

参数资料

| 型号: | IS82C50A-5 |

| 厂商: | Intersil |

| 文件页数: | 7/25页 |

| 文件大小: | 0K |

| 描述: | IC PERIPH UART/BRG 10MHZ 44-PLCC |

| 标准包装: | 26 |

| 特点: | 单芯片 UART/BRG |

| 通道数: | 1,UART |

| 规程: | RS232C |

| 电源电压: | 4.5 V ~ 5.5 V |

| 带并行端口: | 是 |

| 带故障启动位检测功能: | 是 |

| 带调制解调器控制功能: | 是 |

| 带CMOS: | 是 |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 44-LCC(J 形引线) |

| 供应商设备封装: | 44-PLCC |

| 包装: | 管件 |

15

FN2958.5

August 24, 2006

82C50A

Reset

After powerup, the 82C50A Master Reset Schmitt trigger

input (MR) should be held high for TMRW ns to reset the

82C50A circuits to an idle mode until initialization. A high on

MR causes the following:

1. Initializes the transmitter and receiver internal clock

counters.

2. Clears the Line Status Register (LSR), except for

Transmitter Shift Register Empty (TE MT) and Transmit

Holding Register Empty (THRE), which are set. The

Modem Control Register (MCR) is also cleared. All of the

discrete lines, memory elements and miscellaneous logic

associated with these register bits are also cleared or

turned off. Divisor Latches, Receiver Buffer Register,

Transmitter Buffer Register are not effected.

Following removal of the reset condition (MR low), the

82C50A remains in the idle mode until programmed.

A hardware reset of the 82C50A sets the THRE and TEMT

status bit in the LSR. When interrupts are subsequently

enabled, an interrupt occurs due to THRE.

A summary of the effect of a Master Reset on the 82C50A is

given in Table 7.

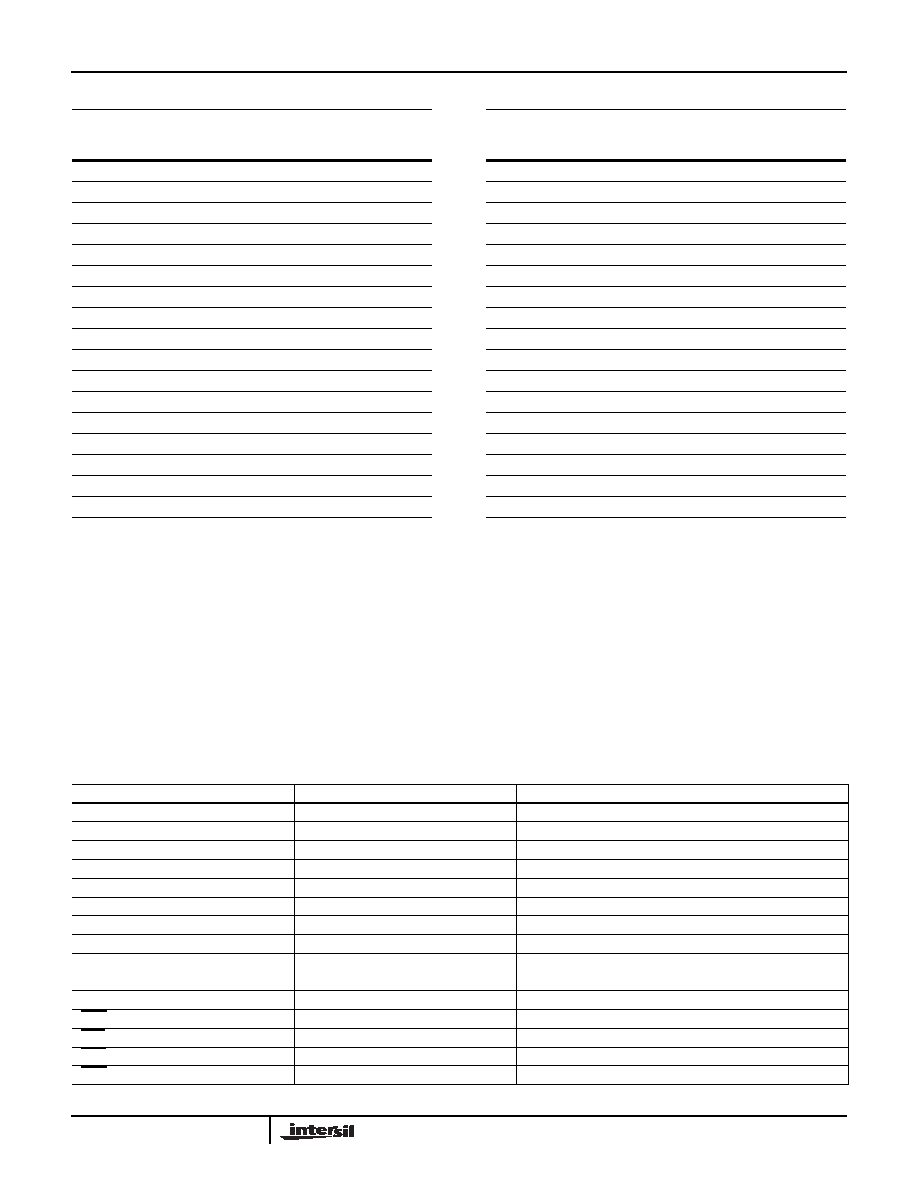

TABLE 5. BAUD RATES USING 2.4576MHz CRYSTAL

DESIRED

BAUD

RATE

DIVISOR USED TO

GENERATE

16 x CLOCK

PERCENT ERROR

DIFFERENCE BETWEEN

DESIRED AND ACTUAL

50

3072

-

75

2048

-

110

1396

0.026

134.5

1142

0.0007

150

1024

-

300

512

-

600

256

-

1200

128

-

1800

85

0.392

2000

77

0.260

2400

64

-

3600

43

0.775

4800

32

-

7200

21

1.587

9600

16

-

19200

8

-

38400

4

-

TABLE 6. BAUD RATES USING 3.072MHz CRYSTAL

DESIRED

BAUD

RATE

DIVISOR USED TO

GENERATE

16 x CLOCK

PERCENT ERROR

DIFFERENCE BETWEEN

DESIRED AND ACTUAL

50

3840

-

75

2560

-

110

1745

0.026

134.5

1428

0.034

150

1280

-

300

640

-

600

320

-

1200

160

-

1800

107

0.312

2000

96

-

2400

80

-

3600

53

0.628

4800

40

-

7200

27

1.23

9600

20

-

19200

10

-

38400

5

-

TABLE 7. 82C50A RESET OPERATIONS

REGISTER/SIGNAL

RESET CONTROL

RESET

Interrupt Enable Register

Master Reset

All Bits Low (0-3 forced and 4-7 permanent)

Interrupt Identification Register

Master Reset

Bit 0 is High, Bits 1 and 2 Low Bits 3-7 are Permanently Low

Line Control Register

Master Reset

All Bits Low

MODEM Control Register

Master Reset

All Bits Low

Line Status Register

Master Reset

All Bits Low, Except Bits 5 and 6 are High

MODEM Status Register

Master Reset

Bit 0-3 Low Bits 4-7 Input Signal

SOUT

Master Reset

High

lntrpt (RCVR Errs)

Read LSR/MR

Low

lntrpt (RCVR Data Ready)

Read RBR/MR

Low

lntrpt (THRE)

Read lIR/Write THR/MR

Low

lntrpt (Modem Status Changes)

Read MSR/MR

Low

Out2

Master Reset

High

RTS

Master Reset

High

DTR

Master Reset

High

Out1

Master Reset

High

相关PDF资料 |

PDF描述 |

|---|---|

| IS82C50A-5Z | IC PERIPH UART/BRG 10MHZ 44-PLCC |

| ATMEGA329-16MUR | MCU AVR 32K FLASH 16MHZ 64QFN |

| CS82C50A-5Z96 | IC ASYNC COMM ELEMNT UART 44PLCC |

| CS82C50A-5Z | IC COMMUNICATION ELEMENT 44-PLCC |

| CP82C52Z | IC UART/BRG 5V 16MHZ 28-PDIP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| IS82C50A-5Z | 功能描述:UART 接口集成电路 W/ANNEAL PERIPH UART /BRG 5V 10MHZ RoHS:否 制造商:Texas Instruments 通道数量:2 数据速率:3 Mbps 电源电压-最大:3.6 V 电源电压-最小:2.7 V 电源电流:20 mA 最大工作温度:+ 85 C 最小工作温度:- 40 C 封装 / 箱体:LQFP-48 封装:Reel |

| IS82C52 | 功能描述:UART 接口集成电路 PERIPH UART/BRG 5V 16MHZ 28PLCC IND RoHS:否 制造商:Texas Instruments 通道数量:2 数据速率:3 Mbps 电源电压-最大:3.6 V 电源电压-最小:2.7 V 电源电流:20 mA 最大工作温度:+ 85 C 最小工作温度:- 40 C 封装 / 箱体:LQFP-48 封装:Reel |

| IS82C52/TR100/BAE | 制造商:Intersil Corporation 功能描述:PERIPH UART/BRG 5V 16MHZ 28PLCC IND - Tape and Reel |

| IS82C5296 | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| IS82C52R2490 | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

发布紧急采购,3分钟左右您将得到回复。