参数资料

| 型号: | ISL12024IVZ |

| 厂商: | Intersil |

| 文件页数: | 9/25页 |

| 文件大小: | 0K |

| 描述: | IC RTC/CALENDAR EEPROM 8-TSSOP |

| 标准包装: | 960 |

| 类型: | 时钟/日历 |

| 特点: | 警报器,闰年,唯一 ID |

| 时间格式: | HH:MM:SS(12/24 小时) |

| 数据格式: | YY-MM-DD-dd |

| 接口: | I²C,2 线串口 |

| 电源电压: | 2.7 V ~ 5.5 V |

| 电压 - 电源,电池: | 1.8 V ~ 5.5 V |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 8-TSSOP(0.173",4.40mm 宽) |

| 供应商设备封装: | 8-TSSOP |

| 包装: | 管件 |

17

FN6370.3

August 18, 2008

Write Operations

Byte Write

For a write operation, the device requires the Slave Address

Byte and the Word Address Bytes. This gives the master

access to any one of the words in the array or CCR.

(Note: Prior to writing to the CCR, the master must write a

02h, then 06h to the status register in two preceding

operations to enable the write operation. See “Writing to the

Clock/Control Registers” on page 12. Upon receipt of each

address byte, the ISL12024 responds with an acknowledge.

After receiving both address bytes the ISL12024 awaits the

8 bits of data. After receiving the 8 data bits, the ISL12024

again responds with an acknowledge. The master then

terminates the transfer by generating a stop condition. The

ISL12024 then begins an internal write cycle of the data to

the non-volatile memory. During the internal write cycle, the

device inputs are disabled, so the device will not respond to

any requests from the master. The SDA output is at high

impedance. (see Figure 16).

A write to a protected block of memory is ignored, but will still

receive an acknowledge. At the end of the write command,

the ISL12024 will not initiate an internal write cycle, and will

continue to ACK commands.

Byte writes to all of the non-volatile registers are allowed,

except the DWAn registers which require multiple byte writes

or page writes to trigger non-volatile writes. See “Device

Operation” on page 12 for more information.

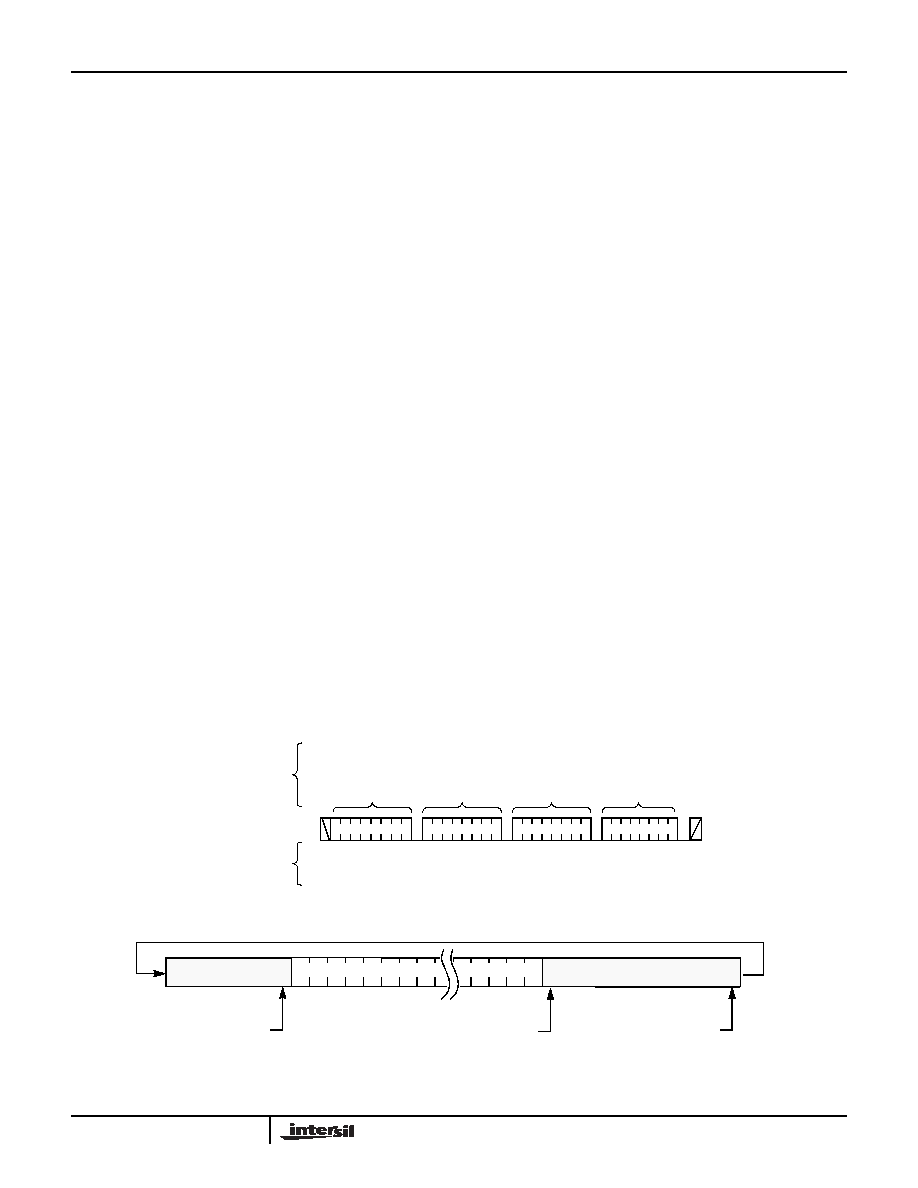

Page Write

The ISL12024 has a page write operation. It is initiated in the

same manner as the byte write operation; but instead of

terminating the write cycle after the first data byte is

transferred, the master can transmit up to 15 more bytes to

the memory array and up to 7 more bytes to the clock/control

registers. The RTC registers require a page write (8 bytes),

individual register writes are not allowed. (Note: Prior to

writing to the CCR, the master must write a 02h, then 06h to

the status register in two preceding operations to enable the

write operatio (see “Writing to the Clock/Control Registers”

After the receipt of each byte, the ISL12024 responds with

an acknowledge, and the address is internally incremented

by one. The address pointer remains at the last address byte

written. When the counter reaches the end of the page, it

“rolls over” and goes back to the first address on the same

page. This means that the master can write 16 bytes to a

memory array page or 8 bytes to a CCR section starting at

any location on that page. For example, if the master begins

writing at location 10 of the memory and loads 15 bytes, then

the first 6 bytes are written to addresses 10 through 15, and

the last 6 bytes are written to columns 0 through 5.

Afterwards, the address counter would point to location 6 on

the page that was just written. If the master supplies more

than the maximum bytes in a page, then the previously

loaded data is over-written by the new data, one byte at a

time. (see Figure 17). The master terminates the Data Byte

loading by issuing a stop condition, which causes the

ISL12024 to begin the non-volatile write cycle. As with the

byte write operation, all inputs are disabled until completion

of the internal write cycle. See Figure 18 for the address,

acknowledge and data transfer sequence.

Stops and Write Modes

Stop conditions that terminate write operations must be sent

by the master after sending at least 1 full data byte and its

associated ACK signal. If a stop is issued in the middle of a

data byte, or before 1 full data byte + ACK is sent, then the

ISL12024 resets itself without performing the write. The

contents of the array are not affected.

S

T

A

R

T

S

T

O

P

SLAVE

ADDRESS

WORD

ADDRESS 1

DATA

A

C

K

A

C

K

A

C

K

SDA BUS

SIGNALS FROM

THE SLAVE

SIGNALS FROM

THE MASTER

0

A

C

K

WORD

ADDRESS 0

1

00 0 0 0 0 0

FIGURE 16. BYTE WRITE SEQUENCE

ADDRESS

10

6 BYTES

15

6 BYTES

ADDRESS = 5

ADDRESS POINTER ENDS

FIGURE 17. WRITING 12 BYTES TO A 16-BYTE MEMORY PAGE STARTING AT ADDRESS 10

AT ADDR = 5

ISL12024

相关PDF资料 |

PDF描述 |

|---|---|

| ISL12025IVZ | IC RTC/CALENDAR EEPROM 8-TSSOP |

| ISL12026IBZ-T7A | IC RTC/CALENDAR EEPROM 8SOIC |

| ISL12027IV27AZ | IC RTC/CALENDAR EEPROM 8-TSSOP |

| ISL12028IVZ | IC RTC/CALENDAR EEPROM 14-TSSOP |

| ISL12029IVZ | IC RTC/CALENDAR EEPROM 14-TSSOP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ISL12024IVZ-T | 功能描述:实时时钟 REAL TIME CLK/CLNDR W/EEPROM IN 8LD RoHS:否 制造商:Microchip Technology 功能:Clock, Calendar. Alarm RTC 总线接口:I2C 日期格式:DW:DM:M:Y 时间格式:HH:MM:SS RTC 存储容量:64 B 电源电压-最大:5.5 V 电源电压-最小:1.8 V 最大工作温度:+ 85 C 最小工作温度: 安装风格:Through Hole 封装 / 箱体:PDIP-8 封装:Tube |

| ISL12025 | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:Real-Time Clock/Calendar with EEPROM |

| ISL12025IBZ | 功能描述:实时时钟 REAL TIME CLK/CLNDR W/EEPROM 2 63VSET RoHS:否 制造商:Microchip Technology 功能:Clock, Calendar. Alarm RTC 总线接口:I2C 日期格式:DW:DM:M:Y 时间格式:HH:MM:SS RTC 存储容量:64 B 电源电压-最大:5.5 V 电源电压-最小:1.8 V 最大工作温度:+ 85 C 最小工作温度: 安装风格:Through Hole 封装 / 箱体:PDIP-8 封装:Tube |

| ISL12025IBZ-T | 功能描述:实时时钟 REAL TIME CLK/CLNDR W/EEPROM 2 63VSET RoHS:否 制造商:Microchip Technology 功能:Clock, Calendar. Alarm RTC 总线接口:I2C 日期格式:DW:DM:M:Y 时间格式:HH:MM:SS RTC 存储容量:64 B 电源电压-最大:5.5 V 电源电压-最小:1.8 V 最大工作温度:+ 85 C 最小工作温度: 安装风格:Through Hole 封装 / 箱体:PDIP-8 封装:Tube |

| ISL12025IVZ | 功能描述:实时时钟 REAL TIME CLK/CLNDR W/EEPROM 2 63SET 8 RoHS:否 制造商:Microchip Technology 功能:Clock, Calendar. Alarm RTC 总线接口:I2C 日期格式:DW:DM:M:Y 时间格式:HH:MM:SS RTC 存储容量:64 B 电源电压-最大:5.5 V 电源电压-最小:1.8 V 最大工作温度:+ 85 C 最小工作温度: 安装风格:Through Hole 封装 / 箱体:PDIP-8 封装:Tube |

发布紧急采购,3分钟左右您将得到回复。