参数资料

| 型号: | ISL12028IVAZ |

| 厂商: | Intersil |

| 文件页数: | 14/29页 |

| 文件大小: | 0K |

| 描述: | IC RTC/CALENDAR EEPROM 14-TSSOP |

| 产品培训模块: | Solutions for Industrial Control Applications |

| 标准包装: | 960 |

| 类型: | 时钟/日历 |

| 特点: | 警报器,闰年,监控器,监视计时器 |

| 时间格式: | HH:MM:SS(12/24 小时) |

| 数据格式: | YY-MM-DD-dd |

| 接口: | I²C,2 线串口 |

| 电源电压: | 2.7 V ~ 5.5 V |

| 电压 - 电源,电池: | 1.8 V ~ 5.5 V |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 14-TSSOP(0.173",4.40mm 宽) |

| 供应商设备封装: | 14-TSSOP |

| 包装: | 管件 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页当前第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页

21

FN8233.9

November 30, 2010

the sixteen bit address is initialized to 0h. In this way, a current

address read immediately after the power on reset can

download the entire contents of memory starting at the first

location. Upon receipt of the Slave Address Byte with the R/W

bit set to one, the ISL12028 issues an acknowledge, then

transmits eight data bits. The master terminates the read

operation by not responding with an acknowledge during the

ninth clock and issuing a stop condition. Refer to Figure 23 for

the address, acknowledge, and data transfer sequence.

It should be noted that the ninth clock cycle of the read

operation is not a “don’t care.” To terminate a read operation,

the master must either issue a stop condition during the

ninth cycle or hold SDA HIGH during the ninth clock cycle

and then issue a stop condition.

RANDOM READ

Random read operations allow the master to access any

location in the ISL12028. Prior to issuing the Slave Address

Byte with the R/W bit set to zero, the master must first

perform a “dummy” write operation.

The master issues the start condition and the slave address

byte, receives an acknowledge, then issues the word

address bytes. After acknowledging receipt of each word

address byte, the master immediately issues another start

condition and the slave address byte with the R/W bit set to

one. This is followed by an acknowledge from the device and

then by the 8-bit data word. The master terminates the read

operation by not responding with an acknowledge and then

issuing a stop condition. Refer to Figure 25 for the address,

acknowledge, and data transfer sequence.

In a similar operation called “Set Current Address,” the

device sets the address if a stop is issued instead of the

second start shown in Figure 25. The ISL12028 then goes

into standby mode after the stop and all bus activity will be

ignored until a start is detected. This operation loads the new

address into the address counter. The next Current Address

Read operation will read from the newly loaded address.

This operation could be useful if the master knows the next

address it needs to read, but is not ready for the data.

SEQUENTIAL READ

Sequential reads can be initiated as either a current address

read or random address read. The first data byte is

transmitted as with the other modes; however, the master

now responds with an acknowledge, indicating it requires

additional data. The device continues to output data for each

acknowledge received. The master terminates the read

operation by not responding with an acknowledge and then

issuing a stop condition.

The data output is sequential, with the data from address n

followed by the data from address n + 1. The address

counter for read operations increments through all page and

column addresses, allowing the entire memory contents to

be serially read during one operation. At the end of the

address space, the counter “rolls over” to the start of the

address space and the ISL12028 continues to output data

for each acknowledge received. Refer to Figure 26 for the

acknowledge and data transfer sequence.

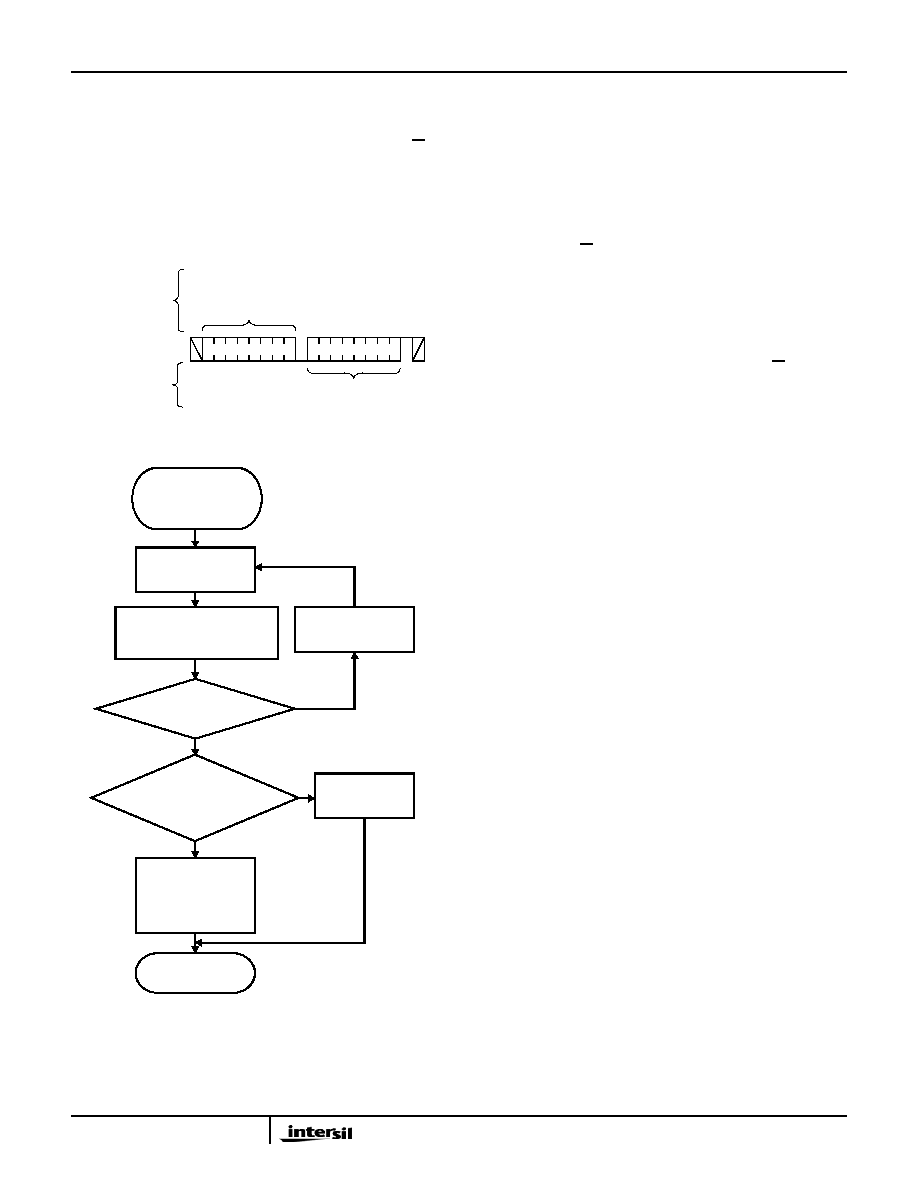

S

T

A

R

T

S

T

O

P

SLAVE

ADDRESS

DATA

A

C

K

SDA BUS

SIGNALS FROM

THE SLAVE

SIGNALS FROM

THE MASTER

1

FIGURE 23. CURRENT ADDRESS READ SEQUENCE

FIGURE 24. ACKNOWLEDGE POLLING SEQUENCE

ACK

RETURNED?

ISSUE MEMORY ARRAY SLAVE

ADDRESS BYTE

AFH (READ) OR AEH (WRITE)

BYTE LOAD

COMPLETED BY

ISSUING STOP.

ENTER ACK POLLING

ISSUE STOP

ISSUE START

NO

YES

ISSUE STOP

NO

CONTINUE

NORMAL READ OR

WRITE COMMAND

SEQUENCE

PROCEED

YES

NON-VOLATILE WRITE

CYCLE COMPLETE. CONTINUE

COMMAND SEQUENCE?

ISL12028, ISL12028A

相关PDF资料 |

PDF描述 |

|---|---|

| AD5206BN10 | IC DGTL POT 6CH 256POS 24-DIP |

| VI-2NT-MW | CONVERTER MOD DC/DC 6.5V 100W |

| VE-B3F-MY-F3 | CONVERTER MOD DC/DC 72V 50W |

| AD5280BRUZ200 | IC DGTL POT 200K 256POS 14-TSSOP |

| VE-B3F-MY-F2 | CONVERTER MOD DC/DC 72V 50W |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ISL12028IVAZ-T | 功能描述:实时时钟 REAL TIME CLKRTC W/ EPROM 4 64VSET 14 RoHS:否 制造商:Microchip Technology 功能:Clock, Calendar. Alarm RTC 总线接口:I2C 日期格式:DW:DM:M:Y 时间格式:HH:MM:SS RTC 存储容量:64 B 电源电压-最大:5.5 V 电源电压-最小:1.8 V 最大工作温度:+ 85 C 最小工作温度: 安装风格:Through Hole 封装 / 箱体:PDIP-8 封装:Tube |

| ISL12028IVZ | 功能描述:实时时钟 REAL TIME CLKRTC W/ EPROM IN 14LD RoHS:否 制造商:Microchip Technology 功能:Clock, Calendar. Alarm RTC 总线接口:I2C 日期格式:DW:DM:M:Y 时间格式:HH:MM:SS RTC 存储容量:64 B 电源电压-最大:5.5 V 电源电压-最小:1.8 V 最大工作温度:+ 85 C 最小工作温度: 安装风格:Through Hole 封装 / 箱体:PDIP-8 封装:Tube |

| ISL12028IVZ-T | 功能描述:实时时钟 REAL TIME CLKRTC W/ EPROM IN 14LD T RoHS:否 制造商:Microchip Technology 功能:Clock, Calendar. Alarm RTC 总线接口:I2C 日期格式:DW:DM:M:Y 时间格式:HH:MM:SS RTC 存储容量:64 B 电源电压-最大:5.5 V 电源电压-最小:1.8 V 最大工作温度:+ 85 C 最小工作温度: 安装风格:Through Hole 封装 / 箱体:PDIP-8 封装:Tube |

| ISL12029 | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:Real Time Clock/Calendar with I2C Bus? and EEPROM |

| ISL12029_10 | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:Real Time Clock/Calendar with I2C Busa?¢ and EEPROM |

发布紧急采购,3分钟左右您将得到回复。