- 您现在的位置:买卖IC网 > PDF目录19717 > ISL6142CB-T (Intersil)IC CONTROLLER HOT PLUG 14-SOIC PDF资料下载

参数资料

| 型号: | ISL6142CB-T |

| 厂商: | Intersil |

| 文件页数: | 19/23页 |

| 文件大小: | 0K |

| 描述: | IC CONTROLLER HOT PLUG 14-SOIC |

| 标准包装: | 2,500 |

| 类型: | 热交换控制器 |

| 应用: | 通用型 VoIP |

| 内部开关: | 无 |

| 电源电压: | 36 V ~ 72 V |

| 工作温度: | 0°C ~ 70°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 14-SOIC(0.154",3.90mm 宽) |

| 供应商设备封装: | 14-SOICN |

| 包装: | 带卷 (TR) |

�� �

�

�

�ISL6142,� ISL6152�

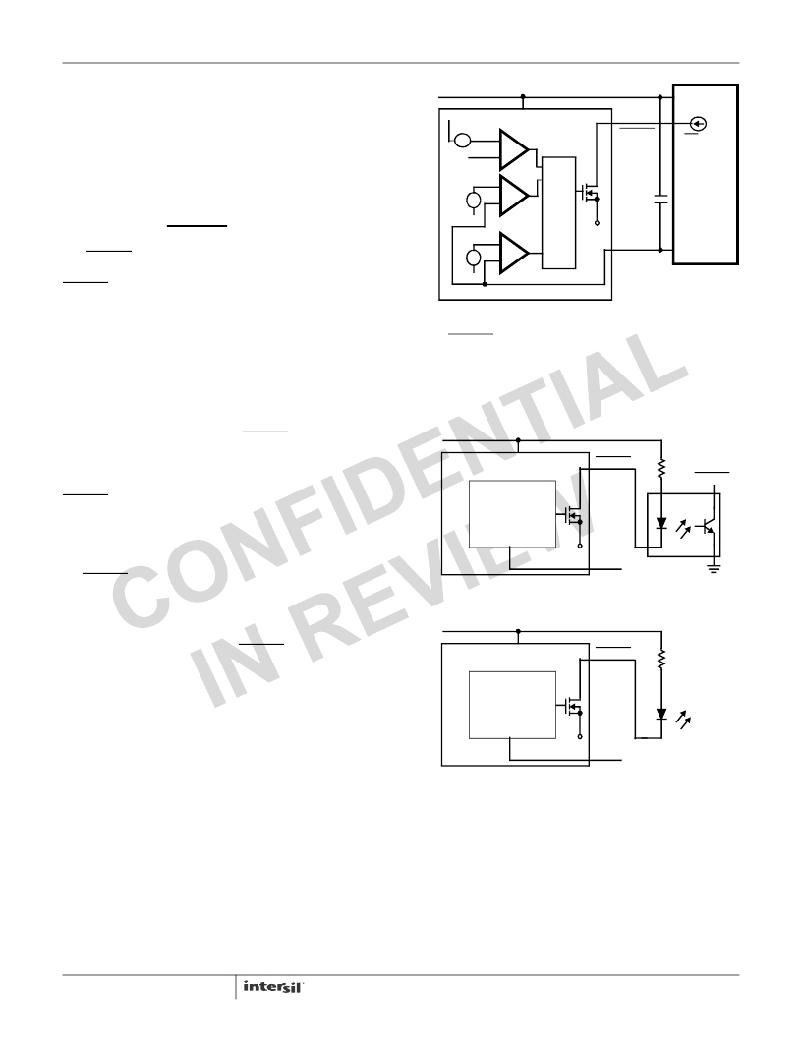

�(one� for� each� pin,� both� from� V� DD� to� -V� IN� ).� This� also� allows�

�the� user� to� adjust� or� trim� either� trip� point� independently.�

�VDD�

�VIN+� VOUT+�

�Some� applications� employ� a� short� pin� ground� on� the�

�Δ� V� GATE�

�(SECTION� OF)� ISL6142�

�connector� tied� to� R4� to� ensure� the� hot� plug� device� is� fully�

�powered� up� before� the� UV� and� OV� pins� (tied� to� the� short� pin�

�ground)� are� biased.� This� ensures� proper� control� of� the� GATE�

�GATE�

�V� GH�

�-�

�+�

�(L� VERSION)�

�PWRGD�

�ON/OFF�

�is� maintained� during� power� up.� This� is� not� a� requirement� for�

�the� ISL6142/52� however� the� circuit� will� perform� properly� if� a�

�short� pin� scheme� is� implemented� (reference� Figure� 38).�

�Applications:� PWRGD/PWRGD�

�The� PWRGD/PWRGD� outputs� are� typically� used� to� directly�

�V� PG�

�+�

�-�

�V� EE�

�V� DH�

�+�

�-�

�+�

�-�

�+�

�-�

�LATCH� Q2�

�LOGIC�

�V� EE�

�CL�

�+�

�ACTIVE� LOW�

�ENABLE�

�MODULE�

�VIN-�

�VOUT-�

�enable a� power� module,� such� as� a� DC/DC� converter.� The�

�PWRGD� (ISL6142)� is� used� for� modules� with� active� low�

�enable� (L� version),� and� PWRGD� (ISL6152)� for� those� with� an�

�active� high� enable� (H� version).� The� modules� usually� have� a�

�pull-up� device� built-in,� as� well� as� an� internal� clamp.� If� not,� an�

�external� pull-up� resistor� may� be� needed.� If� the� pin� is� not�

�used,� it� can� be� left� open.�

�For� both� versions� at� initial� start-up,� when� the� DRAIN� to� V� EE�

�voltage� differential� is� less� than� 1.3V� and� the� GATE� voltage� is�

�within� 2.5V� (V� GH� )� of� its� normal� operating� voltage� (13.6V),�

�power� is� considered� good� and� the� PWRGD/PWRGD� pins�

�V� EE�

�DRAIN�

�FIGURE� 34.� ACTIVE� LOW� ENABLE� MODULE�

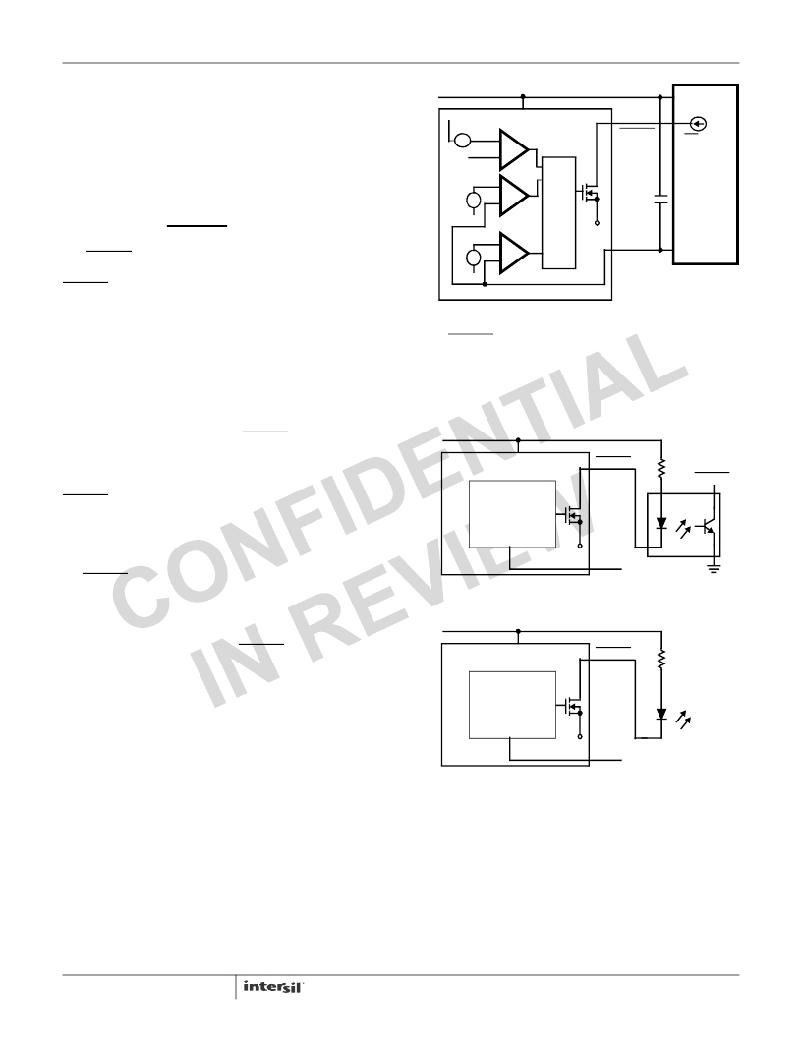

�The� PWRGD� can� also� drive� an� opto-coupler� (such� as� a�

�4N25),� as� shown� in� Figure� 35� or� LED� (Figure� 36).� In� both�

�cases,� they� are� on� (active)� when� power� is� good.� Resistors�

�R13� or� R14� are� chosen� based� on� the� supply� voltage,� and� the�

�amount� of� current� needed� by� the� loads.�

�V� DD�

�will� go� active.� At� this� point� the� output� is� latched� and� the�

�comparators� above� no� longer� control� the� output.� However� a�

�second� DRAIN� comparator� remains� active� and� will� drive� the�

�(SECTION� OF)� ISL6142�

�(L� VERSION)�

�PWRGD�

�R13�

�PWRGD�

�PWRGD/PWRGD� output� inactive� if� the� DRAIN� voltage�

�LOGIC�

�Q2�

�OPTO�

�exceeds� V� EE� by� more� than� 8V.� The� latch� is� reset� by� any� of�

�the� signals� that� shut� off� the� GATE� (Over-Voltage,�

�Under-Voltage;� Under-Voltage-Lock-Out;� Over-Current�

�Time-Out,� disable� pin� high,� or� powering� down).� In� this� case�

�the� PWRGD/PWRGD� output� will� go� inactive,� indicating�

�power� is� no� longer� good.�

�LATCH�

�COMPARATORS�

�V� EE�

�DRAIN�

�FIGURE� 35.� ACTIVE� LOW� ENABLE� OPTO-ISOLATOR�

�ISL6142� (L� version;� Figure� 34):� Under� normal� conditions�

�(DRAIN� voltage� -� V� EE� <� V� PG� ,� and� Δ� V� GATE� -� V� GATE� <� V� GH� )�

�the� Q2� DMOS� will� turn� on,� pulling� PWRGD� low,� enabling� the�

�module.�

�V� DD�

�(SECTION� OF)� ISL6142�

�(L� VERSION)�

�PWRGD�

�R14�

�When� any� of� the� 5� conditions� occur� that� turn� off� the� GATE�

�(OV,� UV,� UVLO,� Over-Current� Time-Out,� disable� pin� high)�

�the� PWRGD� latch� is� reset� and� the� Q2� DMOS� device� will� shut�

�LOGIC�

�LATCH�

�COMPARATORS�

�Q2�

�LED� (GREEN)�

�off� (high� impedance).� The� pin� will� quickly� be� pulled� high� by�

�the� external� module� (or� an� optional� pull-up� resistor� or�

�equivalent)� which� in� turn� will� disable� it.� If� a� pull-up� resistor� is�

�V� EE�

�DRAIN�

�used,� it� can� be� connected� to� any� supply� voltage� that� doesn’t�

�exceed� the� IC� pin� maximum� ratings� on� the� high� end,� but� is�

�high� enough� to� give� acceptable� logic� levels� to� whatever�

�signal� it� is� driving.� An� external� clamp� may� be� used� to� limit� the�

�voltage� range.�

�FIGURE� 36.� ACTIVE� LOW� ENABLE� LED�

�ISL6152� (H� version;� Figure� 37):� Under� normal� conditions�

�(DRAIN� voltage� -� V� EE� <� V� PG� ,� and� Δ� V� GATE� -� V� GATE� <� V� GH� ),�

�the� Q3� DMOS� will� be� on,� shorting� the� bottom� of� the� internal�

�resistor� to� V� EE� ,� turning� Q2� off.� If� the� pull-up� current� from� the�

�external� module� is� high� enough,� the� voltage� drop� across� the�

�6.2k� ?� resistor� will� look� like� a� logic� high� (relative� to� DRAIN).�

�Note� that� the� module� is� only� referenced� to� DRAIN,� not� V� EE�

�(but� under� normal� conditions,� the� FET� is� on,� and� the� DRAIN�

�and� V� EE� are� almost� the� same� voltage).�

�19�

�相关PDF资料 |

PDF描述 |

|---|---|

| MIC39101-2.5BM TR | IC REG LDO 2.5V 1A 8-SOIC |

| EBM15DCWT | CONN EDGECARD 30POS DIP .156 SLD |

| ISPLSI 2096E-135LQ128 | IC PLD ISP 96I/O 7.5NS 128PQFP |

| M4A3-192/96-7VNI | IC CPLD ISP 4A 192MC 144TQFP |

| M4A3-192/96-6VNC | IC CPLD ISP 4A 192MC 144TQFP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ISL6142CBZA | 功能描述:IC HOT PLUG CTRLR NEG 14-SOIC RoHS:是 类别:集成电路 (IC) >> PMIC - 热交换 系列:- 产品培训模块:Obsolescence Mitigation Program 标准包装:100 系列:- 类型:热插拔开关 应用:通用 内部开关:是 电流限制:可调 电源电压:9 V ~ 13.2 V 工作温度:-40°C ~ 150°C 安装类型:表面贴装 封装/外壳:10-WFDFN 裸露焊盘 供应商设备封装:10-TDFN-EP(3x3) 包装:管件 |

| ISL6142CBZA-T | 功能描述:IC CTRLR HOT PLUG NEG V 14-SOIC RoHS:是 类别:集成电路 (IC) >> PMIC - 热交换 系列:- 产品培训模块:Obsolescence Mitigation Program 标准包装:100 系列:- 类型:热插拔开关 应用:通用 内部开关:是 电流限制:可调 电源电压:9 V ~ 13.2 V 工作温度:-40°C ~ 150°C 安装类型:表面贴装 封装/外壳:10-WFDFN 裸露焊盘 供应商设备封装:10-TDFN-EP(3x3) 包装:管件 |

| ISL6142IB | 功能描述:IC CTRLR HOT PLUG NEG 14-SOIC RoHS:否 类别:集成电路 (IC) >> PMIC - 热交换 系列:- 产品培训模块:Obsolescence Mitigation Program 标准包装:100 系列:- 类型:热插拔开关 应用:通用 内部开关:是 电流限制:可调 电源电压:9 V ~ 13.2 V 工作温度:-40°C ~ 150°C 安装类型:表面贴装 封装/外壳:10-WFDFN 裸露焊盘 供应商设备封装:10-TDFN-EP(3x3) 包装:管件 |

| ISL6142IB-T | 功能描述:IC CTRLR HOT PLUG NEG 14-SOIC RoHS:否 类别:集成电路 (IC) >> PMIC - 热交换 系列:- 产品培训模块:Obsolescence Mitigation Program 标准包装:100 系列:- 类型:热插拔开关 应用:通用 内部开关:是 电流限制:可调 电源电压:9 V ~ 13.2 V 工作温度:-40°C ~ 150°C 安装类型:表面贴装 封装/外壳:10-WFDFN 裸露焊盘 供应商设备封装:10-TDFN-EP(3x3) 包装:管件 |

| ISL6142IBZA | 功能描述:IC CTRLR HOT PLUG NEG 14-SOIC RoHS:是 类别:集成电路 (IC) >> PMIC - 热交换 系列:- 产品培训模块:Obsolescence Mitigation Program 标准包装:100 系列:- 类型:热插拔开关 应用:通用 内部开关:是 电流限制:可调 电源电压:9 V ~ 13.2 V 工作温度:-40°C ~ 150°C 安装类型:表面贴装 封装/外壳:10-WFDFN 裸露焊盘 供应商设备封装:10-TDFN-EP(3x3) 包装:管件 |

发布紧急采购,3分钟左右您将得到回复。